# **Ultra-low Power Sub-1GHz Wireless Transceiver**

#### **MCU Features**

- A 32-bit general-purpose micro-controller based on the Arm® Cortex®-M0 core, Single cycle hardware multiply instruction

- Up to 64 KByte on-chip Flash

- supports encrypted storage and hardware ECC verification

- Endurance more than 100,000 cycles, 10 years of data retention

- 8 KByte on-chip SRAM, supports hardware parity

- Programming method:

- SWD online debugging interface

- UART Bootloader

- 23 / 29 general IO (4 with SPI multiplexing in RF part)

- Low-power management:

- Stop mode: RTC Runs, maximum 8 KByte SRAM retention, CPU register retention, all IO retention

- Power Down mode (PD): supports 3 IO wakeup

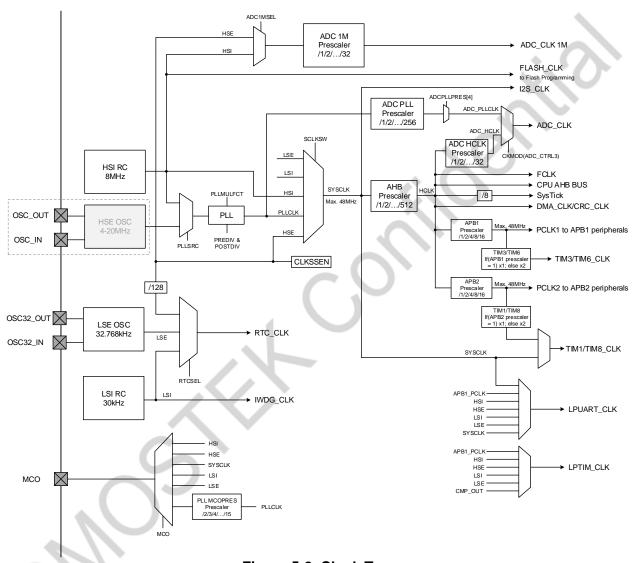

- Clock: Up to 48 MHz

- HSE: 4 MHz~20 MHz, external high-speed crystal

- LSE: 32.768 KHz, external low-speed crystal

- HSI: Internal high-speed RC OSC 8 MHz

- LSI: Internal low-speed RC OSC 30 kHz

- Built-in high-speed PLL

- One channel clock output, which can be configured as configurable system clock, HSE, HSI or PLL post-divided output

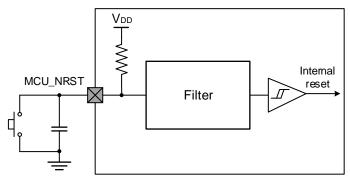

- Reset

- Supports power-on/power-down/external pin reset

- Supports programmable low voltage detection and reset

- Supports watchdog reset

- Communication Interface

- 3xUART interface, with a maximum rate of 3 Mbps, of which 2 USART interfaces support 1xISO7816, 1xIrDA, LIN,1 of which supports low power consumption (LPUART), the highest communication rate in this mode is 9600bps and stop mode can be awakened.

- 2xSPI, the rate is up to 18 MHz, one of which supports multiplexing with I2S

- 2xI2C, the rate is up to 1 MHz, master-slave mode is configurable, and dual-address response is supported in slave mode

- Analog interface

- -1x12 bit high-speed ADC, 1 Msps, up to 6 external single-ended input channels

- -1xOPAMP, built-in programmable gain amplifier up to 32 times

- -1xCOMP, built-in 64-level adjustable comparison benchmark

- -1x high speed 5-channel DMA control, source address and destination address can be configured

#### arbitrarily

- Timer/Counter

- 1xRTC (real-time clock), supports leap year perpetual calendar, alarm event, periodic wake-up, supports internal and external clock calibration

- 2x16 bit Advanced Timer Counters, supports input capture, complementary output, quadrature encoding input, 4 independent channels, of which 3 channels support 6 complementary PWM outputs

- 1x16 bit General Timer, 4 independent channels, supports input capture/output comparison/PWM output

- 1x16 bit Basic Timer

- 1 x 16 bit Low-Power Timer

- 1 x 24 bit SysTick

- 1x 7 bit Window Watchdog (WWDG)

- 1x12 bit Independent Watchdog (IWDG)

- Hardware Divider (HDIV) and Square Root(SQRT)

- Security features

- Flash storage encryption

- CRC16/32 calculation

- Supports write protection (WRP), multiple read protection (RDP) levels (L0/L1/L2)

- Supports clock failure monitoring, anti-dismantling monitoring

- 96-bit UID and 128-bit UCID

#### **RF Features**

- Working frequency: 127 1020 MHz

- Modulation style: (G)FSK, (G)MSK, OOK

- Data rate: 0.5 300 kbps

- Sensitivity: -121 dBm @ 434 MHz, FSK

- RX current: 8.5 mA @ 434 MHz, FSK

- TX current: 72 mA @ 20 dBm, 434 MHz

- Maximum configurable FIFO of 64 Byte

### **System Features**

- Working voltage: 1.8 3.6 V

- Working temperature: -40 85 °C

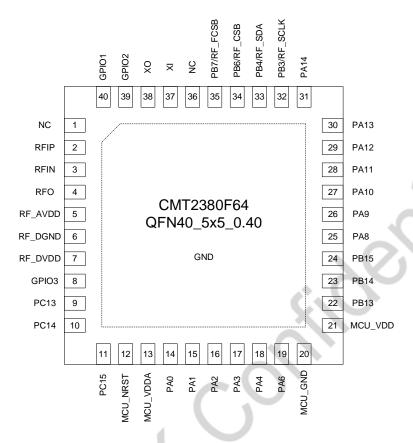

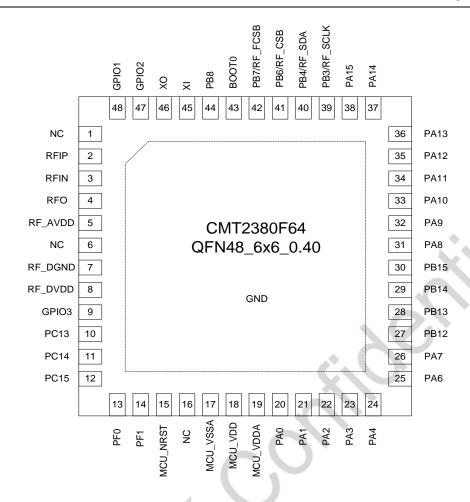

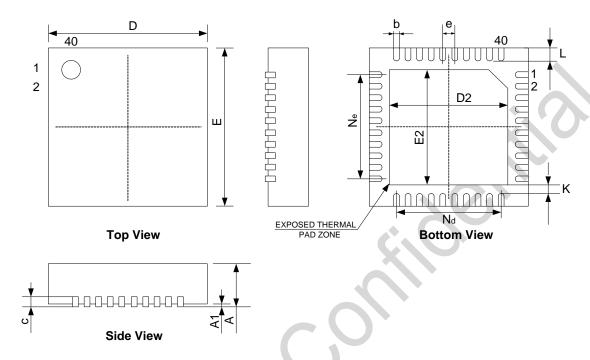

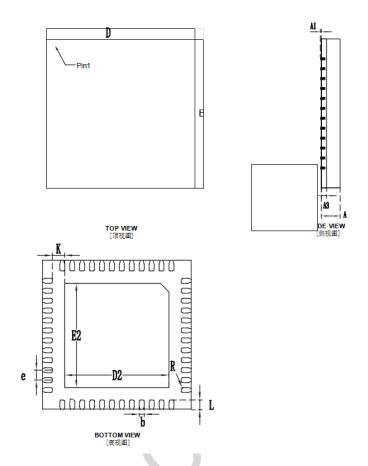

- Package: QFN40 5x5 / QFN 48 6x6

#### Overview

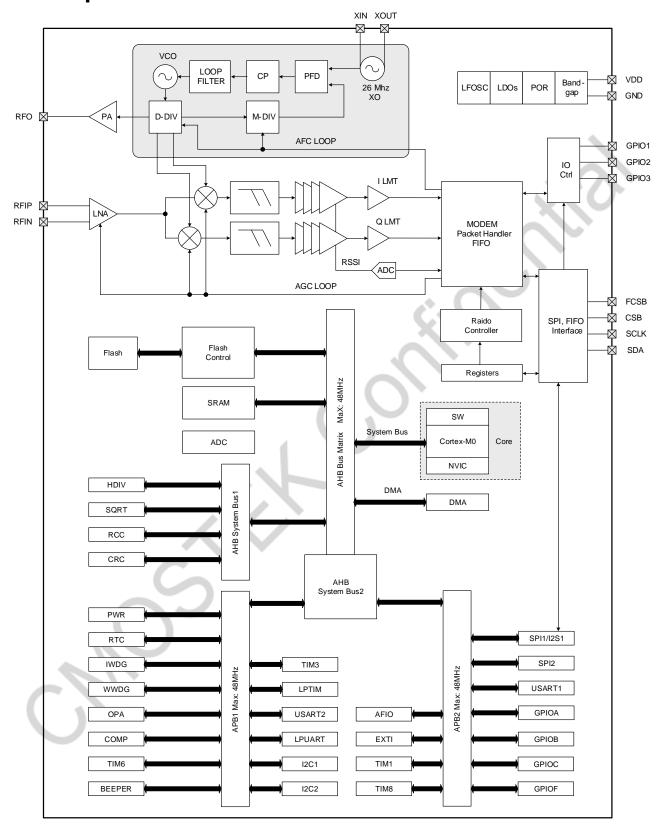

CMT2380F64 integrates a 32-bit ARM Cortex®-M0 core with a super low power consumption RF transceiver. It is a high efficiency super-low power MCU, applying for wireless application of (G) FSK (G) MSK and OOK transceiver from 127 to 1020 MHz.CMT2380F64 is an ultra-low power, high performance, OOK (G) FSK RF transceiver suitable for a variety of 140 to 1020 MHz wireless applications. CMT2380F64 operates from 1.8 V to 3.6 V and supports up to +20 dBm TX power consumption and -121 dBm receiving sensitivity with the corresponding TX current and RX current of 72 mA and 8.5 mA.(MCU power consumption is not included). CMT2380F64 integrates a wealth of peripherals supports standard UART, I2C and SPI interface, with up to 23 general IO

(CMT2380F64-EQR40) / 30 general IO (CMT2380F64-EQR48), supports internal high speed /low speed low power consumption RC oscillator and 32.768 kHz external crystal oscillator, supports a variety of packet formats and encoding and decoding methods up to 64-byte Tx/Rx FIFO, supports featured rich RF GPIO, a variety of low power operation mode and fast startup mechanism, high precision RSSI, manual fast frequency hopping and 12 bit high speed ADCmulti-channel input,etc. CMT2380F64 has a small QFN package size of 5mmx5mm/6mmx6mm, which is ideal for small size and power consumption of Internet applications.

### **Application**

- Auto metering

- Home security and building automation

- Wireless sensor nodes and industrial monitoring

- ISM band data communication

Table1. CMT2380F64 resources list

|                |      |                         |          | Tubicii Ciii 2000i Ci Toocui Coo IIC |                    |       |                     |     |     |     |      |         |

|----------------|------|-------------------------|----------|--------------------------------------|--------------------|-------|---------------------|-----|-----|-----|------|---------|

| Memo           | ory  | Analog peripheral       |          |                                      | Digital peripheral |       |                     |     |     |     |      |         |

| ROM            | RAM  | ADC                     | PDR      | RTC                                  | WDT                | Timer | UART                | SPI | I2C | I2S | GPIO | Package |

| 64 KB<br>Flash | 8 KB | 12 bits x 6-ch<br>1Msps | <b>√</b> | 1                                    | 1                  | 5     | 2xUSART<br>1xLPUART | 2   | 2   | 1   | 19+4 | QFN40   |

| 64 KB<br>Flash | 8 KB | 12 bits x 6-ch<br>1Msps | √        | 1                                    | 1                  | 5     | 2xUSART<br>1xLPUART | 2   | 2   | 1   | 25+4 | QFN48   |

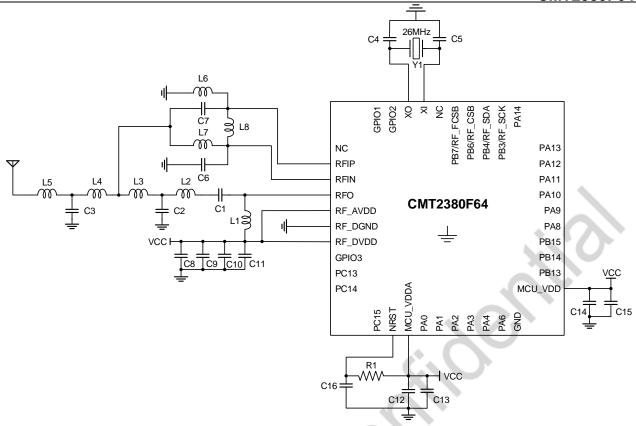

Figure 1.CMT 2380 F64 (QFN 40 5x5) Typical application diagram (20 dBm power output)

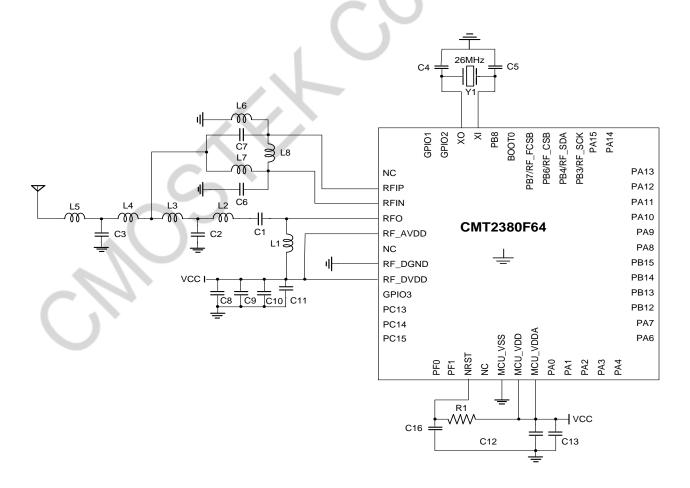

Figure 2.CMT2380F64 (QFN 48 6x6) Typical application diagram (20 dBm power output)

|     |                                                                                         | С       | omponent value |         |      |              |

|-----|-----------------------------------------------------------------------------------------|---------|----------------|---------|------|--------------|

| No. | Description                                                                             | 434 MHz | 868 MHz        | 915 MHz | Unit | Supplier     |

| C1  | ±5%, 0402 NP0, 50 V                                                                     | 15      | 18             | 18      | pF   | -            |

| C2  | ±5%, 0402 NP0, 50 V                                                                     | 3       | 3.6            | 3.6     | pF   | -            |

| C3  | ±5%, 0402 NP0, 50 V                                                                     | 6.2     | 3.3            | 3.3     | pF   | -            |

| C4  | ±5%, 0402 NP0, 50 V                                                                     | 24      | 24             | 24      | pF   | -            |

| C5  | ±5%, 0402 NP0, 50 V                                                                     | 24      | 24             | 24      | pF   |              |

| C6  | ±5%, 0402 NP0, 50 V                                                                     | 4.7     | 2              | 1.8     | pF   |              |

| C7  | ±5%, 0402 NP0, 50 V                                                                     | 4.7     | 2              | 1.8     | pF   | -            |

| C8  | ±20%, 0603 X7R, 25 V                                                                    |         | 4.7            | 1       | uF   | -            |

| C9  | ±5%, 0402 NP0, 50 V                                                                     |         | 470            | 10      | pF   | -            |

| C10 | ±20%, 0402 X7R, 25 V                                                                    |         | 0.1            |         | uF   |              |

| C11 | ±20%, 0402 X7R, 25 V                                                                    |         | 0.1            | 10.     | uF   |              |

| C12 | ±20%, 0402 X7R, 25 V                                                                    |         | 0.1            |         | uF   | -            |

| C13 | ±20%, 0603 X7R, 25 V                                                                    |         | 1              |         | uF   | -            |

| C14 | ±20%, 0402 X7R, 25 V                                                                    |         | 0.1            |         | uF   | -            |

| C15 | ±20%, 0603X7R, 25 V                                                                     |         | 1              |         | uF   | -            |

| C16 | ±20%, 0402 X7R, 25 V                                                                    |         | 0.1            |         | uF   |              |

| R1  | ±5%, 0603 Chip Resistor                                                                 |         | 10             |         | kΩ   |              |

| L1  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 180     | 100            | 100     | nΗ   | Sunlord SDCL |

| L2  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 22      | 12             | 12      | nΗ   | Sunlord SDCL |

| L3  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 15pF    | 15             | 15      | nΗ   | Sunlord SDCL |

| L4  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 33      | 6.2            | 6.2     | nΗ   | Sunlord SDCL |

| L5  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 33      | 6.2            | 6.2     | nΗ   | Sunlord SDCL |

| L6  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 27      | 15             | 15      | nΗ   | Sunlord SDCL |

| L7  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 27      | 15             | 15      | nΗ   | Sunlord SDCL |

| L8  | ±10%, 0603 Multi-layer Chip Inductor                                                    | 68      | 12             | 12      | nH   | Sunlord SDCL |

| Y1  | ±10 ppm, SMD32*25 mm                                                                    |         | 26             |         | MHz  |              |

| U1  | CMT2380F64, Ultra low power consumption Sub-1 GHz Wireless transceiver micro-controller |         | -              |         | -    | CMOSTEK      |

### **Table of Contents**

| 1 | 1 Electrical Characteristic                                     | 8              |

|---|-----------------------------------------------------------------|----------------|

|   | 1.1 Recommended Operation Condition                             | 8              |

|   | 1.2 Absolute Maximum Rating                                     | 8              |

|   | 1.3 Power Consumption                                           |                |

|   | 1.4 RF Receiver Specification                                   |                |

|   | 1.5 RF Transmitter Specification                                |                |

|   | 1.6 Settling Time of RF Status Switching                        |                |

|   | 1.8 Crystal Oscillator Specification                            |                |

|   | Controller Reset and Power Control Module Specification         |                |

|   | 1.10 Controller Embedded Reference Voltage                      |                |

|   | 1.11 Controller Working Current Characteristic                  | 14             |

|   | 1.12 External Clock Source Charateristic                        | 16             |

|   | 1.13 Controller internal clock source characteristics           |                |

|   | 1.14 Controller low-power mode wake-up time                     |                |

|   | 1.15 PLL characteristics                                        |                |

|   | 1.17 I/O port characteristic                                    |                |

|   | 1.18 MCU_NRST Pin Characteristics                               |                |

|   | 1.19 TIM characteristic                                         |                |

|   | 1.20 I2C Characteristic                                         |                |

|   | 1.21 SPI/I2S Characteristic                                     |                |

|   | 1.22 ADC Characteristic                                         | 30             |

|   | 1.23 Operational Amplifier (OPAMP) Characteritic                | 31             |

|   | 1.24 COMP Characteristic                                        | 32             |

|   | 1.25 Temperature Sensor(TS) Characteristics                     |                |

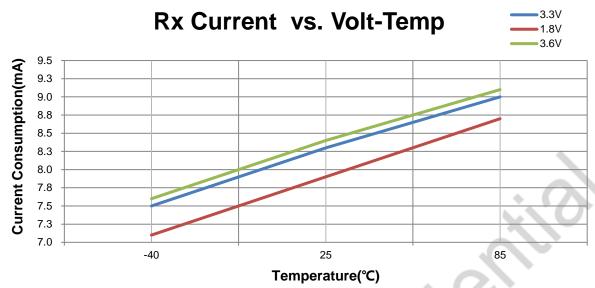

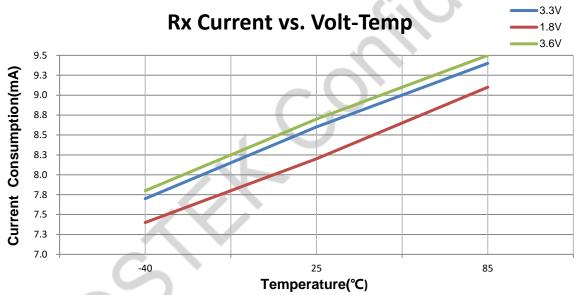

|   | 1.26 Rx Current VS. Supply Voltage                              | 33<br>21       |

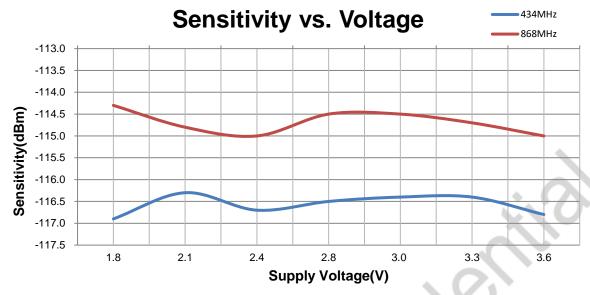

|   | 1.28 Sensitivity vs. Supply Voltage                             | 3 <del>4</del> |

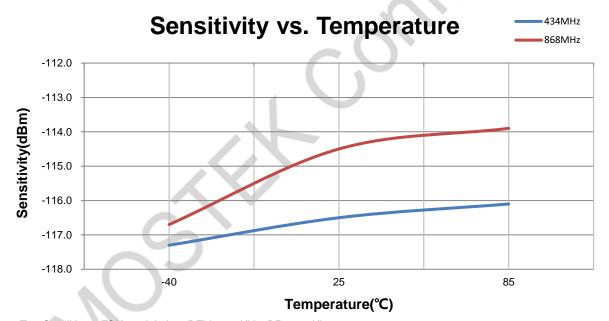

|   | 1.29 Sensitivity vs. Tmeperature                                |                |

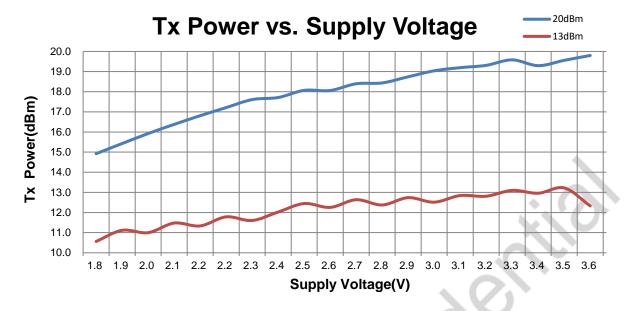

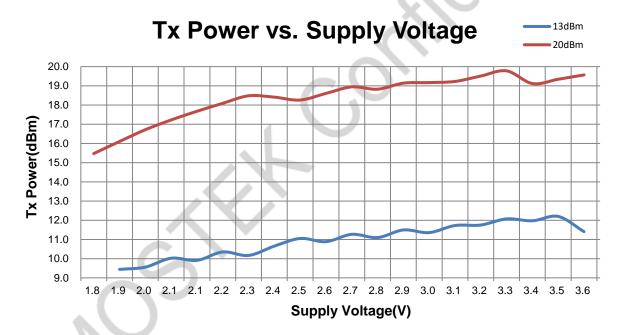

|   | 1.30 Tx Power vs. Supply Voltage                                |                |

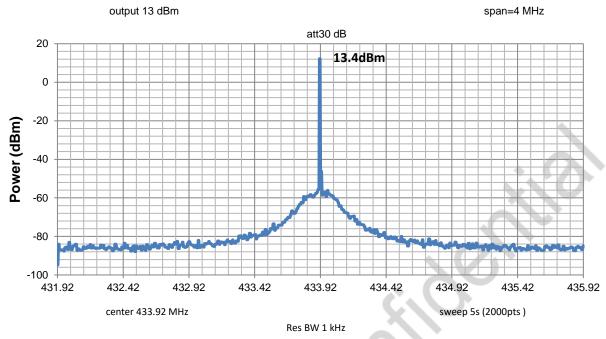

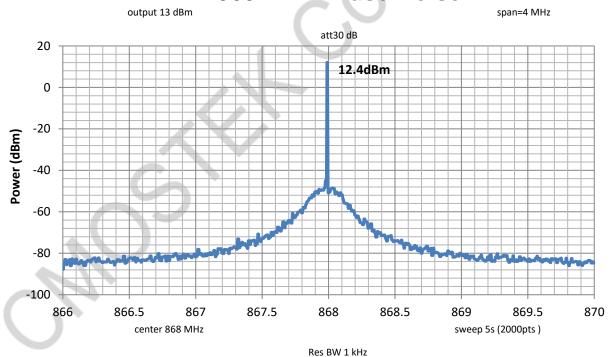

|   | 1.31 Tx Phase Noise                                             |                |

| 2 | 2 Pin Description                                               | 38             |

|   | 3 Chip Frame                                                    |                |

|   | 4 Sub-G Transceiver                                             |                |

| 4 |                                                                 |                |

|   | 4.1 Transmitter                                                 | 47             |

|   | 4.2 Receiver                                                    |                |

|   | 4.3 Power-on Reset (POR)                                        |                |

|   | 4.4 Crystal Oscillator                                          |                |

|   | 4.5 Low power frequency oscillator (LPOSC)                      |                |

|   | 4.6 Internal Low Power Detection                                |                |

|   | 4.7 Received Signal Strength Indicator (RSSI)                   |                |

|   | 4.8 Phase Jump Detector (PJD)                                   |                |

|   | 4.9 Clock Data Recovery (CDR) 4.10 Fast Freguncy Hopping        |                |

|   | 4.11 Chip Operation                                             |                |

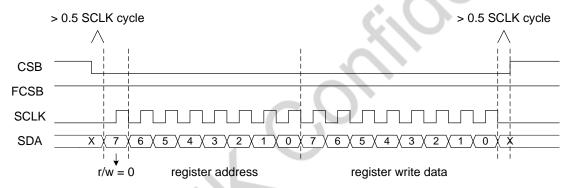

|   | 4.11.1 SPI Interface                                            |                |

|   |                                                                 |                |

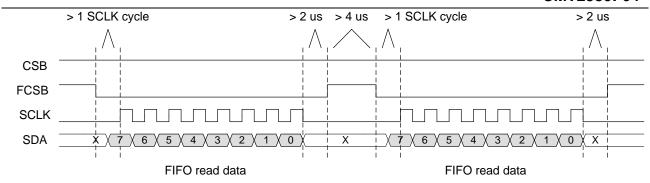

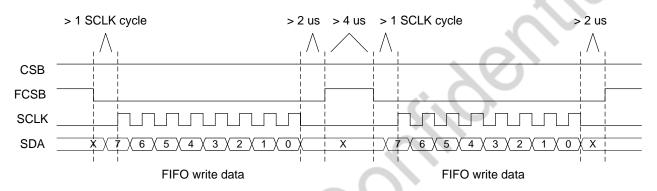

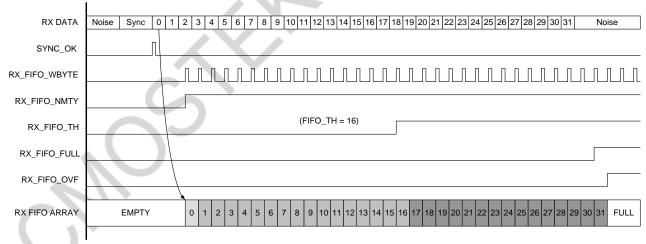

|   | 4.11.2 FIFO Interface                                           |                |

|   | 4.11.3 Transceiver working status, timing and power consumption |                |

|   | 4.11.4 GPIO Function and Interrupt Mapping                      |                |

| 5 | 5 Function Description                                          | 60             |

|   | 5.1 Memory                                                      | 60             |

|   | 5.1.1 Embedded flash memory                                     |                |

|   | 5.1.2 Embedded SRAM                                             |                |

|   | 5.1.3 Nested vectored interrupt controller (NVIC)               |                |

|   |                                                                 |                |

|   | 5.2 Extended interrupt/ event controller (EXTI)                 |                |

|   | 5.4 Boot Modes                                                  |                |

|   | 5.5 Power supply scheme                                         |                |

|   | 5.6 Programmable voltage monitor                                |                |

|   |                                                                 |                |

| _  | 5.7 Low Power Mode                                                   |    |

|----|----------------------------------------------------------------------|----|

|    | 5.8 Direct Memory Access (DMA)                                       |    |

|    | 5.9 Real Time Clock (RTC)                                            |    |

|    | 5.10 Timer and Watch Dog.                                            |    |

|    | 5.10.1 Basic timer TIM6                                              |    |

|    | 5.10.2 General purpose timer TIM3                                    |    |

|    | 5.10.3 Low power timer (LPTIM)                                       |    |

|    | 5.10.4 Adcanced control timer (TIM1/TIM8)                            | 66 |

|    | 5.10.5 Systick                                                       | 67 |

|    | 5.10.6 Watchdog Timer (WDG)                                          | 67 |

|    | 5.11 I2C Bus Interface                                               |    |

|    | 5.12 Universal synchronous asynchronous receiver transmitter (USART) |    |

|    | 5.13 Serial Perigheral Interface (SPI)                               |    |

|    | 5.14 Synchronous Serial Interchip Sound (I2S)                        |    |

|    | 5.15 General purpose input/output (GPIO)                             |    |

|    | 5.17 Operational Amplifier (OPAMP)                                   |    |

|    | 5.18 Analog Comparator (COMP)                                        |    |

|    | 5.19 Temperature Sensor (TS)                                         |    |

|    | 5.20 BEEPER                                                          |    |

|    | 5.21 HDIV/ SQRT                                                      | 74 |

|    | 5.22 Cyclic Redundancy Check Calculation Unit (CRC)                  |    |

|    | 5.23 Unique device ID(UID)                                           |    |

|    | 5.24 Serial wire SWD debug port (SWD)                                |    |

| 6  | Order Information                                                    | 76 |

| 7  | Package Outline                                                      | 77 |

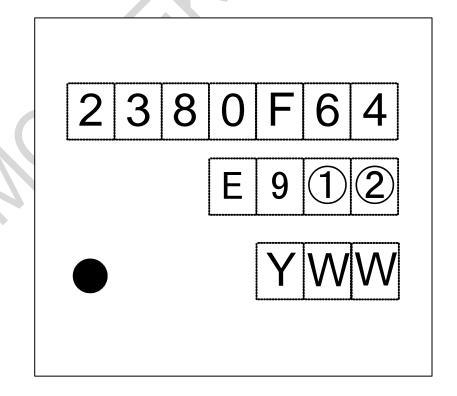

| 8  | Silk Printing Information                                            | 79 |

|    | Relevant Documents                                                   |    |

| 9  |                                                                      |    |

| 10 | Revision                                                             | 82 |

| 11 | Contacts                                                             | 83 |

# 1 Electrical Characteristic

VDD= 3.3 V, TOP= 25 °C, FRF = 433.92 MHz, sensitivity is measured by receiving a PN9 coded data and matching impedance to  $50\Omega$  under 0.1% BER standard.Unless otherwise stated, all results are tested on the CMT2380F17-EM evaluation board.

### 1.1 Recommended Operation Condition

| Parameter               | Symbol               | Condition                 | Min. | Тур. | Max. | Unit       |

|-------------------------|----------------------|---------------------------|------|------|------|------------|

| Operating power voltage | $V_{DD-RF}$          |                           | 1.8  |      | 3.6  | V          |

|                         | V <sub>MCU</sub>     | CPU working rate 0-48 MHz | 1.8  |      | 3.6  | V          |

| Operating temperature   | T <sub>OP</sub>      |                           | -40  |      | 85   | $^{\circ}$ |

| RF power voltage slope  | V <sub>RF-PSR</sub>  |                           | 1    |      |      | mV/us      |

| Voltage slope           | V <sub>MCU-PSR</sub> |                           | 10   |      |      | mV/us      |

| AHB clock frequency     | f <sub>HCLK</sub>    |                           | 0    |      | 48   | MHz        |

| APB1 clock frequency    | f <sub>PCLK1</sub>   |                           | 0    |      | 48   | MHz        |

| APB2 clock frequency    | f <sub>PCLK2</sub>   |                           | 0    |      | 48   | MHz        |

### 1.2 Absolute Maximum Rating

| Parameter                            | Symbol                       | Conditions              | Min  | Max | Unit                                                                               |

|--------------------------------------|------------------------------|-------------------------|------|-----|------------------------------------------------------------------------------------|

| Supply Voltage                       | $V_{DD}$                     |                         | -0.3 | 3.6 | V                                                                                  |

| Interface Voltage                    | V <sub>IN</sub>              |                         | -0.3 | 3.6 | V                                                                                  |

| Junction Temperature                 | TJ                           |                         | -40  | 125 | $^{\circ}$                                                                         |

| Storage Temperature                  | T <sub>STG</sub>             |                         | -50  | 150 | $^{\circ}$                                                                         |

| Soldering Temperature                | T <sub>SDR</sub>             | Retention at least 30 s |      | 255 | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| ESD Rating <sup>[2]</sup>            | $\langle                   $ | Human body mode(HBM)    | -2   | 2   | kV                                                                                 |

| Latch-up Current                     |                              | <b>@ 85</b> ℃           | -100 | 100 | mA                                                                                 |

| MCU-VDD maximum current to<br>Ground | ) T                          |                         |      | 200 | mA                                                                                 |

| MCU pin maximum sink current         |                              |                         |      | 16  | mA                                                                                 |

#### Notes:

<sup>[2].</sup> CMT2380F64 is a high performance RF integrated circuit. The operation and assembly of this chip should only be performed on a workbench with good protection.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

<sup>[1].</sup> Exceeding the Absolute Maximum Ratings may cause permanent damage to the equipment. This value is a pressure rating and does not imply that the function of the equipment is affected under this pressure condition, but if it is exposed to absolute maximum ratings for extended periods of time, it may affect equipment reliability.

# 1.3 Power Consumption

| Parameter             | Symbol               | Condition                                      | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------|------------------------------------------------|------|------|------|------|

| Cloop current         |                      | Sleep mode, sleep timer is off                 |      | 300  |      | nA   |

| Sleep current         | ISLEEP               | Sleep mode, sleep timer is on                  |      | 800  |      | nA   |

| Standby current       | I <sub>Standby</sub> | Crystal oscillator is on                       |      | 1.45 |      | mA   |

|                       |                      | 433 MHz                                        |      | 5.7  |      | mA   |

| RFS current           | I <sub>RFS</sub>     | 868 MHz                                        |      | 5.8  |      | mA   |

|                       |                      | 915 MHz                                        |      | 5.8  |      | mA   |

|                       |                      | 433 MHz                                        |      | 5.6  | 4    | mA   |

| TFS current           | I <sub>TFS</sub>     | 868 MHz                                        |      | 5.9  |      | mA   |

|                       |                      | 915 MHz                                        |      | 5.9  | • (  | mA   |

|                       |                      | FSK, 433 MHz, 10 kbps,10 kHz F <sub>DEV</sub>  |      | 8.5  |      | mA   |

| RX current (high      | I <sub>Rx-HP</sub>   | FSK, 868 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 8.6  |      | mA   |

| performance)          |                      | FSK, 915 MHz, 10 kbps,10 kHz F <sub>DEV</sub>  |      | 8.9  |      | mA   |

|                       |                      | FSK, 433 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.2  |      | mA   |

| RX current (low power | I <sub>Rx-LP</sub>   | FSK, 868 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.3  |      | mA   |

| consumption)          |                      | FSK, 915 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.6  |      | mA   |

|                       |                      | FSK, 433 MHz, +20 dBm (Direct Tie)             |      | 72   |      | mA   |

|                       |                      | FSK, 433 MHz, +20 dBm (RF switch)              |      | 77   |      | mA   |

|                       |                      | FSK, 433 MHz, +13 dBm (Direct Tie)             |      | 23   |      | mA   |

|                       |                      | FSK, 433 MHz, +10 dBm (Direct Tie)             |      | 18   |      | mA   |

|                       |                      | FSK, 433 MHz, - 10 dBm (Direct Tie)            |      | 8    |      | mA   |

|                       |                      | FSK, 868 MHz, +20 dBm (Direct Tie)             |      | 87   |      | mA   |

|                       |                      | FSK, 868 MHz, +20 dBm (RF switch)              |      | 80   |      | mA   |

|                       |                      | FSK, 868 MHz, +13 dBm (Direct Tie)             |      | 27   |      | mA   |

| TX current            | I <sub>Tx</sub>      | FSK, 868 MHz, +10 dBm (Direct Tie)             |      | 19   |      | mA   |

|                       |                      | FSK, 868 MHz, - 10 dBm (Direct Tie)            |      | 8    |      | mA   |

|                       |                      | FSK, 915 MHz, +20 dBm (Direct Tie)             |      | 70   |      | mA   |

|                       |                      | FSK, 915 MHz, +20 dBm (RF switch)              |      | 75   |      | mA   |

|                       |                      | FSK, 915 MHz, +13 dBm (Direct Tie)             |      | 28   |      | mA   |

|                       |                      | FSK, 915 MHz, +10 dBm (Direct Tie)             |      | 19   |      | mA   |

|                       |                      | FSK, 915 MHz, - 10 dBm (Direct Tie)            |      | 8    |      | mA   |

|                       |                      | . 5. 3, 5 15 III IZ, 16 dBill (Billott 110)    |      | U    |      |      |

Notes: The above power consumption is only RF working current, excluding the working current of the controller part.

# 1.4 RF Receiver Specification

| Parameter             | Symbol              | Condition                                                   | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------|-------------------------------------------------------------|------|------|------|------|

| Data rate             | DR                  | ООК                                                         | 0.5  |      | 40   | kbps |

| Data fale             | DK                  | FSK and GFSK                                                | 0.5  |      | 300  | kbps |

| Deviation             | F <sub>DEV</sub>    | FSK and GFSK                                                | 2    |      | 200  | kHz  |

|                       | S <sub>433-HP</sub> | $DR = 2.0 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$           |      | -121 |      | dBm  |

|                       |                     | $DR = 10 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$            |      | -116 |      | dBm  |

|                       |                     | DR = 10 kbps, $F_{DEV}$ = 10 kHz (Low power setting)        |      | -115 |      | dBm  |

| Sensitivity @ 433 MHz |                     | $DR = 20 \text{ kbps}, F_{DEV} = 20 \text{ kHz}$            |      | -113 |      | dBm  |

|                       |                     | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (Low power setting) |      | -112 |      | dBm  |

|                       |                     | $DR = 50 \text{ kbps}, F_{DEV} = 25 \text{ kHz}$            |      | -111 |      | dBm  |

Rev 0.3 | 9 / 83

|                                               |                     |                                                                                                                     | 1    | <u>CI</u> | MT2380 | <u> 1564 </u> |

|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|------|-----------|--------|---------------|

| Parameter                                     | Symbol              | Condition                                                                                                           | Min. | Тур.      | Max.   | Unit          |

|                                               |                     | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                                                             |      | -108      |        | dBm           |

|                                               |                     | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                                                            |      | -105      |        | dBm           |

|                                               |                     | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                                                            |      | 103       |        | dBm           |

|                                               |                     | DR = 2.0 kbps, F <sub>DEV</sub> = 10 kHz                                                                            |      | -119      |        | dBm           |

|                                               |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz                                                                             |      | -113      |        | dBm           |

|                                               |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz (Low power setting)                                                         |      | -111      |        | dBm           |

|                                               |                     | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz                                                                             |      | -111      |        | dBm           |

| Sensitivity @ 868 MHz                         | S <sub>868-HP</sub> | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (Low power setting)                                                         |      | -109      |        | dBm           |

|                                               |                     | DR = 50 kbps, $F_{DEV}$ = 25 kHz                                                                                    |      | -108      |        | dBm           |

|                                               |                     | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                                                             |      | -105      |        | dBm           |

|                                               |                     | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                                                            |      | -102      |        | dBm           |

|                                               |                     | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                                                            |      | -99       |        | dBm           |

|                                               |                     | DR = 2.0 kbps, F <sub>DEV</sub> = 10 kHz                                                                            |      | -117      |        | dBm           |

|                                               |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz                                                                             | 4    | -113      |        | dBm           |

|                                               |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz (Low power setting)                                                         |      | -111      |        | dBm           |

|                                               |                     | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz                                                                             | V    | -111      |        | dBm           |

| Sensitivity @ 915 MHz                         | S <sub>915-HP</sub> | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (Low power setting)                                                         |      | -109      |        | dBm           |

|                                               |                     | DR = 50 kbps, F <sub>DEV</sub> = 25 kHz                                                                             |      | -109      |        | dBm           |

|                                               |                     | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                                                             |      | -105      |        | dBm           |

|                                               |                     | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                                                            |      | -102      |        | dBm           |

|                                               |                     | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                                                            |      | 99        |        | dBm           |

| Saturation Input Signal<br>Level              | P <sub>LVL</sub>    | (5)                                                                                                                 |      |           | 20     | dBm           |

|                                               |                     | F <sub>RF</sub> =433 MHz                                                                                            |      | 35        |        | dBc           |

| Image Rejection Ratio                         | IMR                 | F <sub>RF</sub> =868 MHz                                                                                            |      | 33        |        | dBc           |

|                                               |                     | F <sub>RF</sub> =915 MHz                                                                                            |      | 33        |        | dBc           |

| RX Channel Bandwidth                          | BW                  | RX channel bandwidth                                                                                                | 50   |           | 500    | kHz           |

| Co-channel Rejection<br>Ratio                 | CCR                 | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; Interfere with the same modulation                                         |      | -7        |        | dBc           |

| Adjacent Channel<br>Rejection Ratio           | ACR-I               | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; BW=100 kHz, 200 kHz<br>Channel spacing, interfere with the same modulation |      | 30        |        | dBc           |

| Alternate Channel<br>Rejection Ratio          | ACR-II              | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; BW=100 kHz, 400 kHz<br>Channel spacing, interfere with the same modulation |      | 45        |        | dBc           |

| Blocking Rejection                            |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; ±1 MHz Deviation, continuous wave interference                             |      | 70        |        | dBc           |

| Ratio                                         | ВІ                  | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; ± 2 MHz Deviation, continuous wave interference                            |      | 72        |        | dBc           |

|                                               |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; ±10 MHz Deviation, continuous wave interference                            |      | 75        |        | dBc           |

| Input3 <sup>rd</sup> Order Intercept<br>Point | IIP3                | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; 1 MHz 和 2 MHz Deviation dual tone test, maximum system gain setting.       |      | -25       |        | dBm           |

| RSSI Range                                    | RSSI                |                                                                                                                     | -120 |           | 20     | dBm           |

|                                               |                     | 433.92 MHz, DR = 1.2 kbps, F <sub>DEV</sub> = 5 kHz                                                                 |      | -122.9    |        | dBm           |

|                                               |                     | 433.92 MHz, DR = 1.2 kbps, F <sub>DEV</sub> = 10 kHz                                                                |      | -121.8    |        | dBm           |

| More Sensitivity                              |                     | 433.92 MHz, DR = 1.2 kbps, F <sub>DEV</sub> = 20 kHz                                                                |      | -119.5    |        | dBm           |

| (Typical Configuration)                       |                     | 433.92 MHz, DR = 2.4 kbps, F <sub>DEV</sub> = 5 kHz                                                                 |      | -120.6    |        | dBm           |

|                                               |                     | 433.92 MHz, DR = 2.4 kbps, F <sub>DEV</sub> = 10 kHz                                                                |      | -120.3    |        | dBm           |

|                                               |                     | 433.92 MHz, DR = 2.4 kbps, $F_{DEV}$ = 20 kHz                                                                       |      | -119.7    |        | dBm           |

| Parameter | Symbol | Condition                                              | Min. | Тур.   | Max. | Unit |

|-----------|--------|--------------------------------------------------------|------|--------|------|------|

|           |        | 433.92 MHz, DR = 9.6 kbps, $F_{DEV}$ = 9.6 kHz         |      | -116.0 |      | dBm  |

|           |        | 433.92 MHz, DR = 9.6 kbps, $F_{DEV}$ = 19.2 kHz        |      | -116.1 |      | dBm  |

|           |        | 433.92 MHz, DR = 20 kbps, $F_{DEV}$ = 10 kHz           |      | -114.2 |      | dBm  |

|           |        | 433.92 MHz, DR = 20 kbps, $F_{DEV}$ = 20 kHz           |      | -113.0 |      | dBm  |

|           |        | 433.92 MHz, DR = 50 kbps, $F_{DEV}$ = 25 kHz           |      | -110.6 |      | dBm  |

|           |        | 433.92 MHz, DR = 50 kbps, $F_{DEV}$ = 50 kHz           |      | -109.0 |      | dBm  |

|           |        | 433.92 MHz, DR = 100 kbps, $F_{DEV}$ = 50 kHz          |      | -107.8 |      | dBm  |

|           |        | 433.92 MHz, DR = 200 kbps, $F_{DEV}$ = 50 kHz          |      | -103.5 |      | dBm  |

|           |        | 433.92 MHz, DR = 200 kbps, $F_{DEV} = 100 \text{ kHz}$ |      | -104.3 |      | dBm  |

|           |        | 433.92 MHz, DR = 300 kbps, F <sub>DEV</sub> = 50 kHz   |      | -98.0  |      | dBm  |

|           |        | 433.92 MHz, DR = 300 kbps, $F_{DEV} = 150 \text{ kHz}$ |      | -101.6 |      | dBm  |

# 1.5 RF Transmitter Specification

| Parameter                                    | Symbol               | Condition                                         | Min. | Тур. | Max. | Unit |

|----------------------------------------------|----------------------|---------------------------------------------------|------|------|------|------|

| Output power                                 | Роит                 | Specific peripheral materials                     | -20  | (    | +20  | dBm  |

| σαιραί ρονιοί                                |                      | are needed for                                    | •    |      |      |      |

|                                              |                      | different frequency bands                         | 12.  | J    |      |      |

| Output power step                            | P <sub>STEP</sub>    |                                                   |      | 1    |      | dB   |

| GFSK Gaussian filter coefficient             | ВТ                   |                                                   | 0.3  | 0.5  | 1.0  | -    |

| Output power variation                       | P <sub>OUT-TOP</sub> | Temperature from -40 to +85℃                      |      | 1    |      | dB   |

| Transmitting anurious                        |                      | Pout= +13 dBm,433 MHz, F <sub>RF</sub> <1 GHz     |      |      | -54  | dBm  |

| Transmitting spurious emission               |                      | 1 GHz to 12.75 GHz, with harmonic                 |      |      | -36  | dBm  |

| Harmonic output for                          | H2 <sub>433</sub>    | 2 <sup>nd</sup> harmonic +20 dBm P <sub>OUT</sub> |      | -46  |      | dBm  |

| F <sub>RF</sub> = 433 MHz <sup>[1]</sup>     | H3 <sub>433</sub>    | 3 <sup>nd</sup> harmonic +20 dBm P <sub>OUT</sub> |      | -50  |      | dBm  |

| Harmonic output                              | H2 <sub>868</sub>    | 2 <sup>nd</sup> harmonic +20 dBm P <sub>OUT</sub> |      | -43  |      | dBm  |

| for FRF= 868 MHz[1]                          | H3 <sub>868</sub>    | 3 <sup>nd</sup> harmonic +20 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

| Harmonic output                              | H2 <sub>915</sub>    | 2 <sup>nd</sup> harmonic +20 dBm P <sub>OUT</sub> |      | -48  |      | dBm  |

| for FRF= 915 MHz[1]                          | H3 <sub>915</sub>    | 3 <sup>nd</sup> harmonic +20 dBm P <sub>OUT</sub> |      | -53  |      | dBm  |

| Harmonic output                              | H2 <sub>433</sub>    | 2 <sup>nd</sup> harmonic +13 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

| for FRF= 433 MHz[1]                          | H3 <sub>433</sub>    | 3 <sup>nd</sup> harmonic +13 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

| Harmonic output                              | H2 <sub>868</sub>    | 2 <sup>nd</sup> harmonic +13 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

| for F <sub>RF</sub> = 868 MHz <sup>[1]</sup> | H3 <sub>868</sub>    | 3 <sup>nd</sup> harmonic +13 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

| Harmonic output                              | H2 <sub>915</sub>    | 2 <sup>nd</sup> harmonic +13 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

| for F <sub>RF</sub> = 915 MHz <sup>[1]</sup> | H3 <sub>915</sub>    | 3 <sup>nd</sup> harmonic +13 dBm P <sub>OUT</sub> |      | -52  |      | dBm  |

### Notes:

# 1.6 Settling Time of RF Status Switching

| Parameter | Symbol              | Condition          | Min. | Тур. | Max. | Unit |

|-----------|---------------------|--------------------|------|------|------|------|

|           | T <sub>SLP-RX</sub> | From Sleep to RX   |      | 1000 |      | us   |

|           | T <sub>SLP-TX</sub> | From Sleep toTX    |      | 1000 |      | us   |

|           | T <sub>STB-RX</sub> | From Standby to RX |      | 350  |      | us   |

Rev 0.3 | 11 / 83

<sup>[1].</sup> The harmonic parameter values mainly depend on the quality of the hardware matching network. The above data is measured based on the CMT2380F17-EM module; testing results will be differently when it is done on the self-designed PCB.

|               |                     |                                                             |                            | <u> </u> |

|---------------|---------------------|-------------------------------------------------------------|----------------------------|----------|

|               | T <sub>STB-TX</sub> | From Standby toTX                                           | 350                        | us       |

|               | T <sub>RFS-RX</sub> | From RFS to RX                                              | 20                         | us       |

| Settling time | T <sub>TFS-RX</sub> | From TFS toTX                                               | 20                         | us       |

|               | T <sub>TX-RX</sub>  | From TX to RX (Ramp Down time needs 2 T <sub>symbol</sub> ) | 2 T <sub>symbol</sub> +350 | us       |

|               | T <sub>RX-TX</sub>  | From RX to TX                                               | 350                        | us       |

Notes:

# 1.7 RF Frequency Synthesizer

| Parameter                        | Symbol            | Condition                              | Min. | Тур.  | Max. | Unit   |

|----------------------------------|-------------------|----------------------------------------|------|-------|------|--------|

|                                  |                   |                                        | 760  |       | 1020 | MHz    |

|                                  |                   |                                        | 380  |       | 510  | MHz    |

| Frequency range                  | $F_RF$            | Different matching network is required | 190  |       | 340  | MHz    |

|                                  |                   |                                        | 127  |       | 170  | MHz    |

| Synthesizer frequency resolution | F <sub>RES</sub>  |                                        |      | 25    |      | Hz     |

| Frequency tuning time            | <b>t</b> TUNE     |                                        |      | 150   |      | us     |

|                                  |                   | 10 kHz frequency deviation             |      | -94   |      | dBc/Hz |

|                                  |                   | 100 kHz frequency deviation            |      | -99   |      | dBc/Hz |

| Di                               | PN <sub>433</sub> | 500 kHz frequency deviation            |      | - 118 |      | dBc/Hz |

| Phase noise@ 433 MHz             |                   | 1 MHz frequency deviation              |      | - 127 |      | dBc/Hz |

|                                  |                   | 10 MHz frequency deviation             |      | - 134 |      | dBc/Hz |

|                                  |                   | 10 kHz frequency deviation             |      | -92   |      | dBc/Hz |

|                                  |                   | 100 kHz frequency deviation            |      | -95   |      | dBc/Hz |

| Dhara asias @ 000 MHz            | PN <sub>868</sub> | 500 kHz frequency deviation            |      | -114  |      | dBc/Hz |

| Phase noise@ 868 MHz             |                   | 1 MHz frequency deviation              |      | - 121 |      | dBc/Hz |

|                                  |                   | 10 MHz frequency deviation             |      | - 130 |      | dBc/Hz |

|                                  |                   | 10 kHz frequency deviation             |      | -89   |      | dBc/Hz |

|                                  |                   | 100 kHz frequency deviation            |      | -92   |      | dBc/Hz |

| Discussion @ 045 Mills           | PN <sub>915</sub> | 500 kHz frequency deviation            |      | - 111 |      | dBc/Hz |

| Phase noise@ 915 MHz             |                   | 1 MHz frequency deviation              |      | - 121 |      | dBc/Hz |

|                                  |                   | 10 MHz frequency deviation             |      | - 130 |      | dBc/Hz |

<sup>[1].</sup> Both of TSLP-RX and TSLP-TX are depend on the crystal oscillator startup time, which is mainly related to the crystal itself.

### 1.8 Crystal Oscillator Specification

| Parameter                          | Symbol            | Condition | Min. | Тур. | Max. | Unit |

|------------------------------------|-------------------|-----------|------|------|------|------|

| Crystal frequency <sup>[1]</sup>   | F <sub>XTAL</sub> |           |      | 26   |      | MHz  |

| Frequency tolerance <sup>[2]</sup> | ppm               |           |      | 20   |      | ppm  |

| Load capacitance                   | CLOAD             |           |      | 15   |      | pF   |

| Equivalentresistance               | Rm                |           |      | 60   |      | Ω    |

| Start-up time <sup>[3]</sup>       | †XTAL             |           |      | 400  |      | us   |

#### Notes:

- [1]. CMT2380F64 can use the external reference clock to drive the XIN pin through the coupling capacitor. The peak value of the external clock signal is between 0.3 V and 0.7 V.

- [2]. The value includes (1) initial error; (2) crystal load; (3)aging; and (4) change with temperature. The acceptable crystal frequency tolerance is limited by the receiver bandwidth and the RF frequency offset between the transmitter and the receiver.

- [3]. The parameter is largely related to the crystal.

### 1.9 Controller Reset and Power Control Module Specification

|                   |                                     |             |      | 2.   |      |      |

|-------------------|-------------------------------------|-------------|------|------|------|------|

| Parameter         | Symbol                              | Condition   | Min. | Тур. | Max. | Unit |

| Rising            |                                     | PLS[3:0]=0  | 1.8  | 1.88 | 1.96 |      |

| Falling           |                                     | PLS[3:0]=0  | 1.7  | 1.78 | 1.86 |      |

| Rising            |                                     | PLS[3:0]=1  | 2    | 2.08 | 2.16 |      |

| Falling           |                                     | PLS[3:0]=1  | 1.9  | 1.98 | 2.06 |      |

| Rising            |                                     | PLS[3:0]=2  | 2.2  | 2.28 | 2.36 |      |

| Falling           |                                     | PLS[3:0]=2  | 2.1  | 2.18 | 2.26 |      |

| Rising            |                                     | PLS[3:0]=3  | 2.4  | 2.48 | 2.56 |      |

| Falling           |                                     | PLS[3:0]=3  | 2.3  | 2.38 | 2.46 |      |

| Rising            |                                     | PLS[3:0]=4  | 2.6  | 2.68 | 2.76 |      |

| Falling           |                                     | PLS[3:0]=4  | 2.5  | 2.58 | 2.66 |      |

| Rising            |                                     | PLS[3:0]=5  | 2.8  | 2.88 | 2.96 |      |

| Falling           | V <sub>PVD</sub>                    | PLS[3:0]=5  | 2.7  | 2.78 | 2.86 | V    |

| Rising            |                                     | PLS[3:0]=6  | 3    | 3.08 | 3.16 |      |

| Falling           | (5)                                 | PLS[3:0]=6  | 2.9  | 2.98 | 3.06 |      |

| Rising            |                                     | PLS[3:0]=7  | 3.2  | 3.28 | 3.36 |      |

| Falling           |                                     | PLS[3:0]=7  | 3.1  | 3.18 | 3.26 |      |

| Rising            |                                     | PLS[3:0]=8  | 3.4  | 3.48 | 3.56 |      |

| Falling           |                                     | PLS[3:0]=8  | 3.3  | 3.38 | 3.46 |      |

| Rising            |                                     | PLS[3:0]=9  | 3.6  | 3.68 | 3.76 |      |

| Falling           |                                     | PLS[3:0]=9  | 3.5  | 3.58 | 3.66 |      |

| Rising            |                                     | PLS[3:0]=10 | 3.8  | 3.88 | 3.96 |      |

| Falling           |                                     | PLS[3:0]=10 | 3.7  | 3.78 | 3.86 |      |

| PVD delay         | V <sub>PVDhyst</sub> <sup>(2)</sup> | -           | 80   | 100  | 125  | mV   |

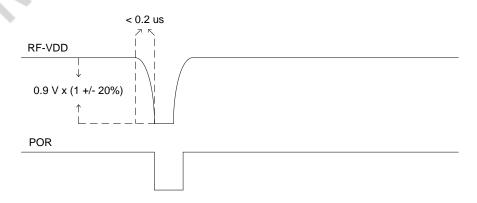

| VDD power up/down | V <sub>POR</sub>                    | -           | -    | 1.53 | -    | ٧    |

# 1.10 Controller Embedded Reference Voltage

| Parameter                          | Symbol                                | Condition                                                                           | Min. | Тур. | Max. | Unit |

|------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| Embedded reference voltage         | V <sub>REFINT</sub>                   | -40℃ <ta<+105℃< td=""><td>1.16</td><td>1.21</td><td>1.26</td><td>V</td></ta<+105℃<> | 1.16 | 1.21 | 1.26 | V    |

| Sampling time of ADC when internal | T <sub>S_vrefint</sub> <sup>(1)</sup> | PLS [2:0]=001 ( rising edge)                                                        | -    | 10   | -    | μѕ   |

| reference voltage read out         |                                       | ( 0 0 /                                                                             |      |      |      |      |

<sup>1.</sup> The minimum sampling time was obtained from multiple cycles in application.

### 1.11 Controller Working Current Characteristic

Current consumption is a combination of several parameters and factors, including operating voltage, ambient temperature, I/O pin load, product software configuration, operating frequency, I/O pin turnover rate, program location in memory, and code executed, etc.

### Maximum current consumption

The micro-controller is in the following conditions:

- All I / O pins are in input mode and are connected to a static level VDD or VSS with no load.

- All peripherals are disabled, unless otherwise noted.

- The access time of the flash memory is adjusted to the frequency (0 wait period for 0 to 18 MHz, 1 wait period for 18 to 36 MHz, 2 waiting period for over 36 MHz).

- The command pre-fetch function is turned on (notes: this parameter must be set before the clock and bus frequency distribution is set).

- When the peripherals are turned on: fpclk1 = fhclk, fpclk2 = fhclk.

# Maximum current consumption in operating mode and the data processing code is run from the internal flash memory

| Parameter                | Sign | Condition                                   | <b>f</b> HCLK | Typical Value | Unit |

|--------------------------|------|---------------------------------------------|---------------|---------------|------|

|                          |      | Futornal alask(2) anabla all                | 48 MHz        | 8.4           |      |

| Operating current in the |      |                                             | 24 MHz        | 5.0           |      |

|                          |      |                                             | 8 MHz         | 2.8           |      |

| operating mode           | lpp  |                                             | 48 MHz        | 5.0           | mA   |

|                          |      | External clock <sup>(2)</sup> , disable all | 24 MHz        | 3.3           |      |

|                          |      | the peripherals                             | 8 MHz         | 2.3           |      |

<sup>1.</sup> Guaranteed by design and comprehensive assessment, not tested in production.

# Maximum current consumption in operating mode, and data processing code is run from the internal RAM

| Parameter | Symbol | Condition                                  | fHCLK  | Typ. (1) | Unit |

|-----------|--------|--------------------------------------------|--------|----------|------|

|           |        | External clock <sup>(2)</sup> , enable all | 48 MHz | 6.2      |      |

|           |        | the peripherals                            | 24 MHz | 4.1      |      |

|           |        |                                            | 8 MHz  | 3.2      |      |

<sup>2.</sup> External clock, PLL is enabled when the f<sub>HCLK</sub> is 24 MHz or 48 MHz.

| Operating current     | I <sub>DD</sub> | External clock <sup>(2)</sup> , disable all | 48 MHz | 4.4 | mA |

|-----------------------|-----------------|---------------------------------------------|--------|-----|----|

| in the operating mode |                 | the peripherals                             | 24 MHz | 3.2 |    |

|                       |                 |                                             | 8 MHz  | 2.6 |    |

<sup>1.</sup> Guaranteed by design and comprehensive assessment, not tested in production.

### Maximum current consumption in sleep mode, and the code runs in the internal flash memory

| Parameter          | Symbol          | Condition                                                   | fHCLK  | Typ. (1) | Unit |

|--------------------|-----------------|-------------------------------------------------------------|--------|----------|------|

|                    |                 |                                                             | 48 MHz | 6.5      |      |

|                    |                 | External clock <sup>(2)</sup> , enable all the peripherals  | 24 MHz | 3.9      | C    |

| Working current in |                 |                                                             | 8 MHz  | 2.0      |      |

| sleep mode         | I <sub>DD</sub> |                                                             | 48 MHz | 2.9      | mA   |

|                    |                 | External clock <sup>(2)</sup> , disable all the peripherals | 24 MHz | 2.1      |      |

|                    |                 |                                                             | 8 MHz  | 1.4      |      |

According to the comprehensive assessment, V<sub>DDmax</sub> and f<sub>HCLKmax</sub> enabling peripheral are the test condition.

#### Typical consumption in stop and sleep mode

| Parameter          | Symbol   | Condition                                       | Typ <sup>(1)</sup>    | Max                   | Unit  |

|--------------------|----------|-------------------------------------------------|-----------------------|-----------------------|-------|

| r al allietei      | Syllibol | Condition                                       | V <sub>DD</sub> =3.3V | V <sub>DD</sub> =3.3V | Offic |

| SLEEP mode current |          | Kernel stopped, all peripherals including       | 2.7                   | 5                     | mA    |

|                    |          | Cortex-M 0 core peripherals such as NVIC,       |                       |                       |       |

|                    |          | system ticking clock (SysTick) still running    |                       |                       |       |

| STOP mode current  |          | RTC is not running, SRAM, registers and all I/O | 1.5                   | 2.5                   | uA    |

|                    |          | states retain                                   |                       | _                     |       |

| PD mode current    |          | VDD power down mode, 3 WAKEUP IO and            | 0.5                   | 1                     | uA    |

|                    |          | NRST can be awakened                            |                       |                       |       |

### Typical current consumption

MCU is under the following conditions:

- All I / O pins are in input mode and are connected to a static level VDD or VSS with no load.

- All peripherals are disabled, unless otherwise noted.

- The access time of the flash memory is adjusted to the fHCLK frequency (0 wait period for 0 to 18 MHz, 1 wait period for 18 to 36 MHz, 2 waiting period for over 36 MHz).

- The command pre-fetch function is turned on (notes: this parameter must be set before the clock and bus frequency distribution is set).

- When the peripherals are turned on:  $f_{PCLK1} = f_{HCLK}$ ,  $f_{PCLK2} = f_{HCLK}$ ,  $f_{ADCCLK} = f_{PCLK2}/3$ .

<sup>2.</sup> External clock, PLL is enabled when the fhclkis 24 MHz or 48 MHz.

<sup>2.</sup> External clock, PLL is enabled when the f<sub>HCLK</sub> is 24 MHz or 48 MHz.

# Typical current consumption in operation mode, with data processing code running from an internal Flash

| Parameter         | Symbol                         | Condition                                                             |        | Ту                         | γp <sup>(1)</sup>           | Unit  |

|-------------------|--------------------------------|-----------------------------------------------------------------------|--------|----------------------------|-----------------------------|-------|

| raranneter        | Symbol                         | Thol Condition f <sub>HCLK</sub>                                      |        | Enable all the peripherals | Disable all the peripherals | Offic |

|                   |                                | Estamable interest de la de (UCE) veira e                             | 48 MHz | 8.2                        | 4.8                         |       |

|                   | AHB prefrequency to reduce the | External high speed clock (HSE,) using AHB prefrequency to reduce the | 24 MHz | 5.0                        | 3.3                         | mA    |

| Supply current    |                                | 8 MHz                                                                 | 2.7    | 2.1                        |                             |       |

| in operating mode |                                | 1.1                                                                   | 48 MHz | 7.6                        | 4.3                         |       |

|                   |                                | nternal high speed RC oscillator (2)                                  | 24 MHz | 4.3                        | 2.7                         | mA    |

|                   |                                | (HSI), AHB pre-frequency to reduce the frequency                      | 8 MHz  | 2.1                        | 1.5                         |       |

<sup>1.</sup> Typical value is tested under TA=25°C, VDD=3.3V.

Typical current consumption in sleep mode, data processing code is run from internal Flash or RAM

| Parameter                     | Symbol   | Condition                                             |        | Typ <sup>(1</sup>          | )                           | Unit  |

|-------------------------------|----------|-------------------------------------------------------|--------|----------------------------|-----------------------------|-------|

| rarameter                     | Syllibol | Condition                                             | fhcLK  | Enable all the peripherals | Disable all the peripherals | Offic |

|                               |          | External high ancad glock                             | 48 MHz | 6.3                        | 2.7                         |       |

|                               |          | External high speed clock  (HSE) using AHB            | 24 MHz | 3.7                        | 2.0                         | mA    |

| Working current in sleep mode | loo      | (HSE), using AHB prefrequency to reduce the frequency | 8 MHz  | 1.8                        | 1.2                         |       |

|                               |          | Internal high around DC                               | 48 MHz | 5.7                        | 2.1                         |       |

|                               |          | Internal high speed RC oscillator(2) (HSI), AHB       | 24 MHz | 3.1                        | 1.4                         | mA    |

|                               |          | pre-frequency to reduce the frequency                 | 8 MHz  | 1.2                        | 0.6                         |       |

<sup>1.</sup> Typical value is tested under TA=25 ℃, VDD=3.3 V.

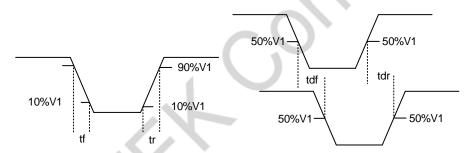

### 1.12 External Clock Source Charateristic

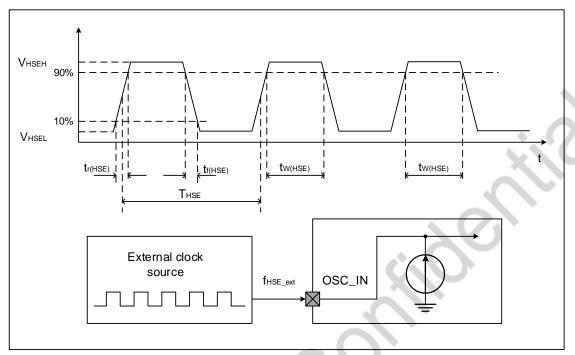

High-speed external user clock generated from external oscillation sources

The characteristic parameters in the following table are measured under a high-speed external clock source and the ambient temperature and supply voltage meet the conditions in the following table.

High-speed external user clock features

| Symbol                    | Parameter                                             | Condition | Min             | Тур | Max                 | Unit |

|---------------------------|-------------------------------------------------------|-----------|-----------------|-----|---------------------|------|

| f <sub>HSE_ext</sub>      | User external clock frequency                         |           | 4               | 8   | 20                  | MHz  |

| V <sub>HSEH</sub>         | OSC_IN input pin at high-level voltage <sup>(1)</sup> |           | 0.7 VDD         | =   | V <sub>DD</sub>     |      |

| V <sub>HSEL</sub>         | OSC_IN input pin at low-level voltage <sup>(1)</sup>  | -         | V <sub>SS</sub> | -   | 0.3 V <sub>DD</sub> | V    |

| t <sub>w(HSE)</sub>       | OSC_IN high /low time <sup>(1)</sup>                  |           | 16              | -   | -                   |      |

| $t_{r(LSE)}$ $t_{f(LSE)}$ | OSC_IN up/ down time <sup>(1)</sup>                   |           | -               | -   | 20                  | ns   |

| $C_{\text{in(HSE)}}$      | OSC_IN input capacitance (1)                          |           |                 | 5   |                     | pF   |

<sup>2.</sup> The internal high-speed clock is 8 MHz, and PLL is enabled when fhclk>8 MHz.

<sup>2.</sup> The internal high-speed clock is 8 MHz, and PLL is enabled when fHCLK>8 MHz.

| DuCy <sub>(HSE)</sub>                                      | DuCy <sub>(HSE)</sub> Duty cycle <sup>(1)</sup> |                     | 45         | = | 55 | %  |

|------------------------------------------------------------|-------------------------------------------------|---------------------|------------|---|----|----|

| I <sub>L</sub> OSC_IN input leakage current <sup>(1)</sup> |                                                 | VSS≤VIN≤VDD         | -          | - | ±1 | μΑ |

| 1. Guaranteed by                                           | y design and comprehensive evaluation           | on, not tested in p | roduction. |   |    |    |

The AC timing diagram of the external high-speed clock source

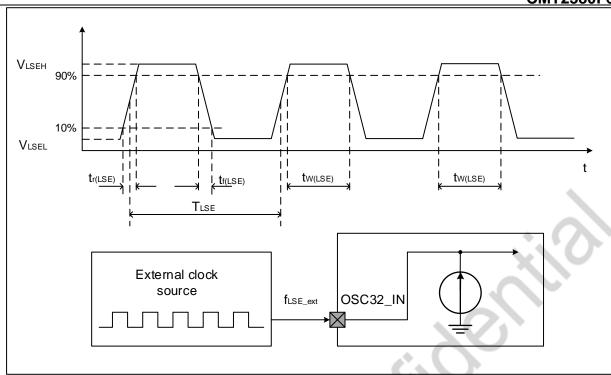

• Low-speed external user clock generated from external oscillation sources

Low-speed external user clock features

| Symbol                                             | Parameter                                               | Condition                                         | Min                 | Тур    | Max                 | Unit |

|----------------------------------------------------|---------------------------------------------------------|---------------------------------------------------|---------------------|--------|---------------------|------|

| $f_{LSE\_ext}$                                     | User external clock frequency                           |                                                   | 0                   | 32.768 | 1000                | KHz  |

| $V_{LSEH}$                                         | OSC32_IN input pin at high-level voltage <sup>(1)</sup> |                                                   | 0.7 V <sub>DD</sub> | -      | $V_{DD}$            | V    |

| $V_{LSEL}$                                         | OSC32_IN input pin at low-level voltage <sup>(1)</sup>  | _                                                 | Vss                 | -      | 0.3 V <sub>DD</sub> |      |

| tw(LSE)                                            | OSC32_IN high /low time <sup>(1)</sup>                  |                                                   | 450                 | -      | -                   | l    |

| $t_{r(LSE)}$ OSC32_IN up/ down time <sup>(1)</sup> |                                                         |                                                   | -                   | 1      | 10                  | ns   |

| DuCy <sub>(LSE)</sub>                              | Duty cycle <sup>(1)</sup>                               |                                                   | 30                  | -      | 70                  | %    |

| l <sub>L</sub>                                     | OSC32_IN input leakage current <sup>(1)</sup>           | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> | -                   | -      | ±1                  | μA   |

The AC timing diagram of the external low-speed clock source

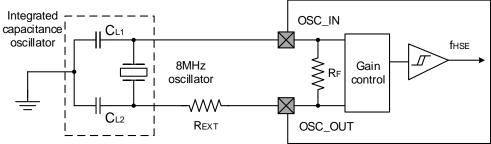

### A high-speed external clock generated by using a crystal / ceramic resonator

The high speed external clock (HSE) can be generated using an oscillator consisting of a  $4\sim20$  MHz crystal/ceramic oscillator. The information given in this section is based on the use of typical external components listed in the table below. In applications where the oscillator and load capacitance must be as close to the oscillator pin as possible to reduce output distortion and stability time at startup. For detailed parameters of crystal oscillator (frequency, package, accuracy, etc.), please consult the corresponding manufacturer (the crystal resonators mentioned here are usually referred to the passive crystal oscillator).

| Symbol                              | Parameter                                                                          | Condition                                                             | Min | Тур | Max | Unit |

|-------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                               |                                                                       | 4   | 8   | 20  | MHz  |

| $C_{L1}$ $C_{L2}^{(3)}$             | The suggested load capacitance and corresponding crystal serial resistance $(R_S)$ | $R_S = 30 \Omega$                                                     | -   | 20  |     | pF   |

| i <sub>2</sub>                      | HSE drive current                                                                  | V <sub>DD</sub> =3.3 V, V <sub>IN</sub> =V <sub>SS</sub><br>30pF load | -   | 1.1 | 1.6 | mA   |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                       | V <sub>DD</sub> is stable                                             |     | 3   |     | ms   |

**HSE 4**∼20 MHz Oscillator Characteristic

- 1. The parameters of the resonator are given by the crystal resonator manufacturer.

- 2. Guaranteed by design and comprehensive assessment, not tested in production.

- 3. For CL1 and CL2, it is recommended to use high quality ceramic dielectric capacitance (typically) between 5pF and 25pF designed for high-frequency applications, and to select suitable crystals or resonators. Usually CL1 and CL2 have the same parameters. Crystal manufacturers usually give parameters for load capacitance as serial combinations of CL1 and CL2. The capacitive reactance of PCB and MCU pins should be taken into account when selecting CL1 and CL2.

- 4. tSU(HSE) is the startup time. It is measured from the time when HSE is enabled by software until a stable 8MHz oscillation is obtained. This value is measured on a standard crystal resonator and can vary widely depending on the crystal manufacturer.

Typical applications of using 8MHz crystals

Note: The value of Rext is depended on the crystal characteristic.

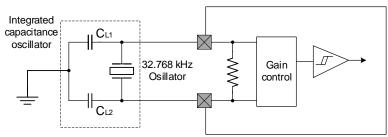

A low-speed external clock generated by using a crystal / ceramic resonator

The low speed external clock (LSE) can be generated using an oscillator consisting of a 32.768 kHz crystal/ceramic oscillator. The information given in this section is based on the use of typical external components listed in the table below. In applications where the oscillator and load capacitance must be as close to the oscillator pin as possible to reduce output distortion and stability time at startup. For detailed parameters of crystal oscillator (frequency, package, accuracy, etc.), please consult the corresponding manufacturer (the crystal resonators mentioned here are usually referred to the passive crystal oscillator).

Note: For CL1 and CL2, high quality porcelain dielectric capacitors between 5 p F and 15 p F and well-compliant crystals or oscillators are recommended. Usually, CL1 and CL2 have the same parameters. Crystal manufacturers usually give the parameters of the load capacitance as a serial combination of CL1 and CL2.

Load capacitance CL is calculated by the following equation:  $CL = CL1 \ CL2 / (CL1 + CL2) + Cstray$ , where Cstray is the capacitor of the pin and the capacitor associated with the PCB board or PCB.

| LSE | Oscillator | Characteristic | (flse=32.768 kHz)(1) |

|-----|------------|----------------|----------------------|

|-----|------------|----------------|----------------------|

| Symbol                                         | Parameter                                                                                   | Condition                   | Min | Тур | Max | Unit |

|------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------|-----|-----|-----|------|

| C <sub>L1</sub> C <sub>L2</sub> <sup>(2)</sup> | Recommended load capacitance and corresponding crystal serial impedance (RS) <sup>(3)</sup> | R <sub>s</sub> :30 KΩ~65 KΩ | 1   | 1   | 20  | pF   |

|                                                |                                                                                             | VDD=3.3 V                   |     |     |     |      |

| 12                                             | LSE drive current                                                                           | CL1=CL2=12.5 pF             | -   | 0.3 | -   | μΑ   |

|                                                |                                                                                             | $R_S=30 \text{ K}\Omega$    |     |     |     |      |

| t <sub>SU(LSE)</sub> <sup>(4)</sup>            | Startup time                                                                                | VDD is stable               | -   | 2   | -   | s    |

- 1. Guaranteed by design and comprehensive assessment, not tested in production.

- 2. See the attention and warning paragraph above this table.

- 3. Choose high quality oscillator with a small RS value that can optimize current consumption. Check with the crystal manufacturer for more details.

- 4. t<sub>SU(LSE)</sub> is the start time, measured from the software enabling LSE, until the stable 32.768 KHz oscillation is stabled. This value is measured on a standard crystal oscillator, which may vary greatly by the crystal manufacturer.

Typical applications of using 32.768 kHz crystals

### 1.13 Controller internal clock source characteristics

### • High speed internal (HSI) RC Oscillator

### HSI Oscillator Characteristic (1)(2)

| Sign                 | Parameter         | Condition                                                              | Min  | Тур | Max  | Unit |

|----------------------|-------------------|------------------------------------------------------------------------|------|-----|------|------|

| fHSI                 | Frequency         | VDD=3.3 V, $T_{A}\text{=}25~^{\circ}\text{C},\text{after calibration}$ | 7.92 | 8   | 8.08 | MHz  |

| 400                  | HSI oscillator    | VDD=3.3 V, T <sub>A</sub> = -40~105 ℃, temperature drift               | -3   | -   | 3    | %    |

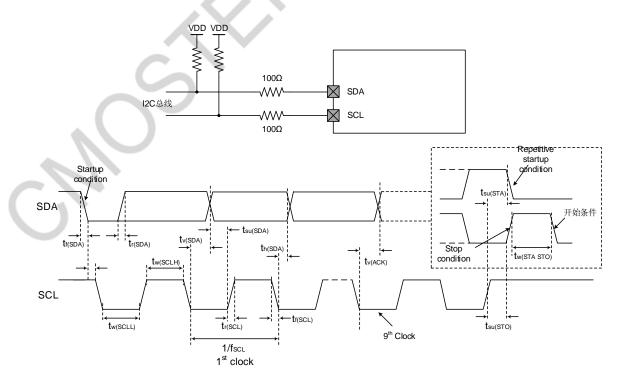

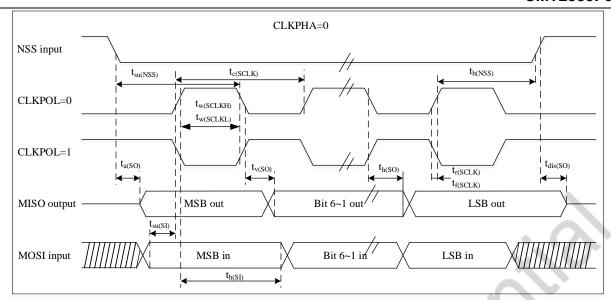

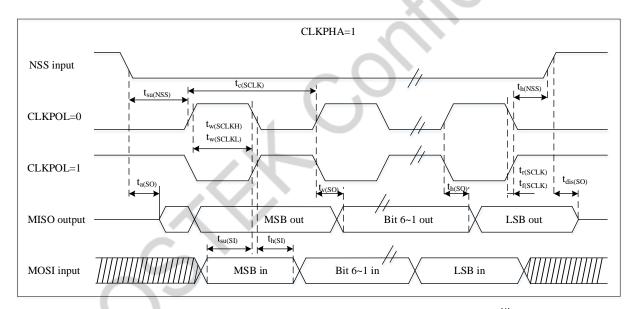

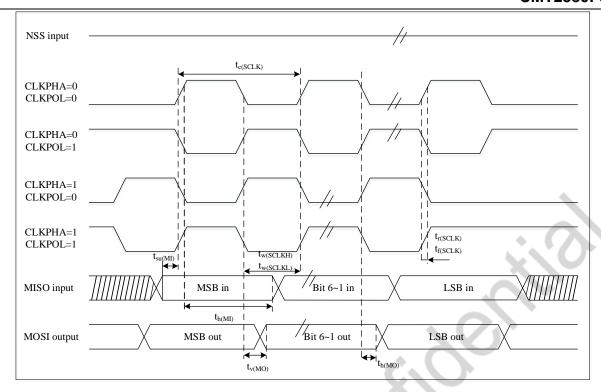

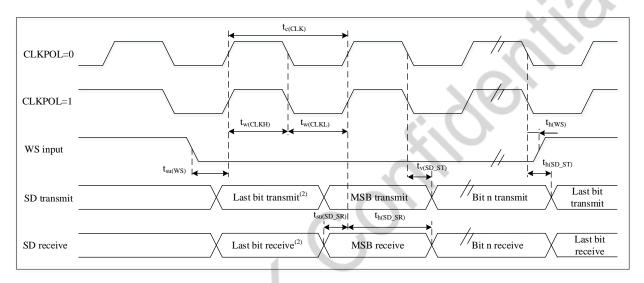

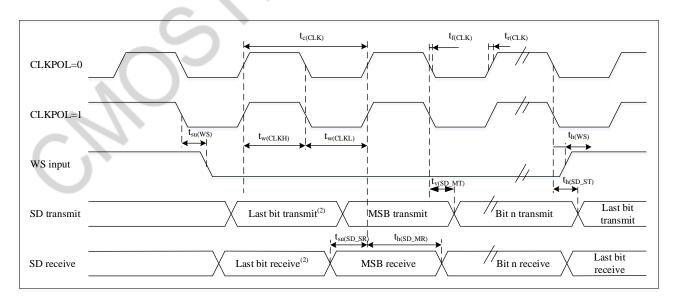

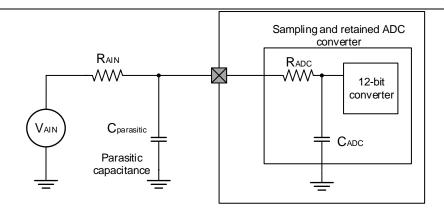

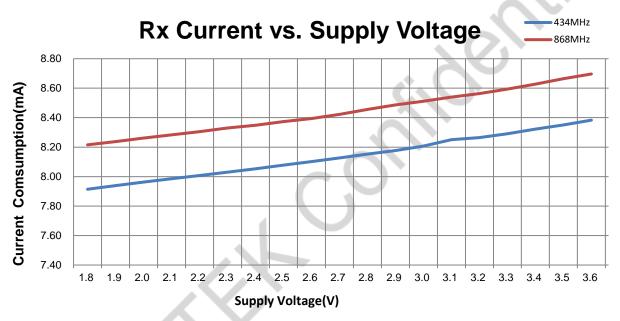

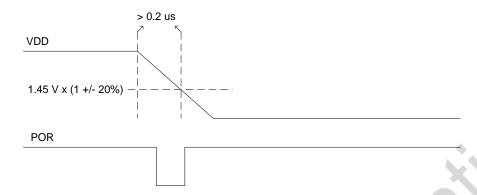

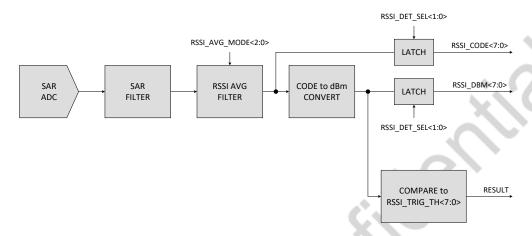

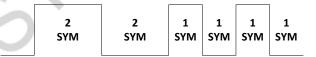

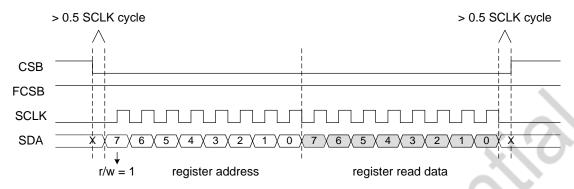

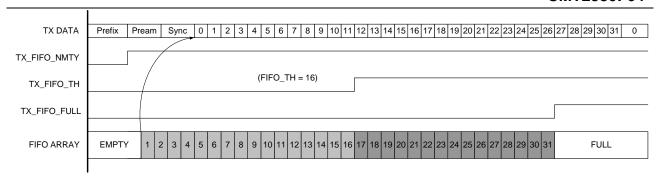

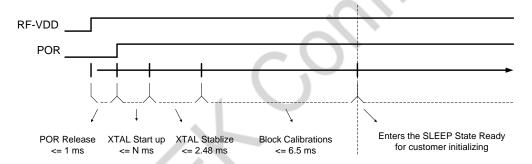

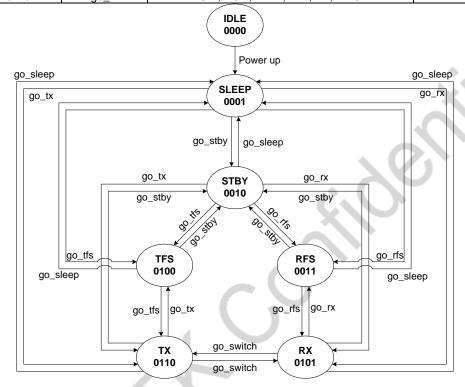

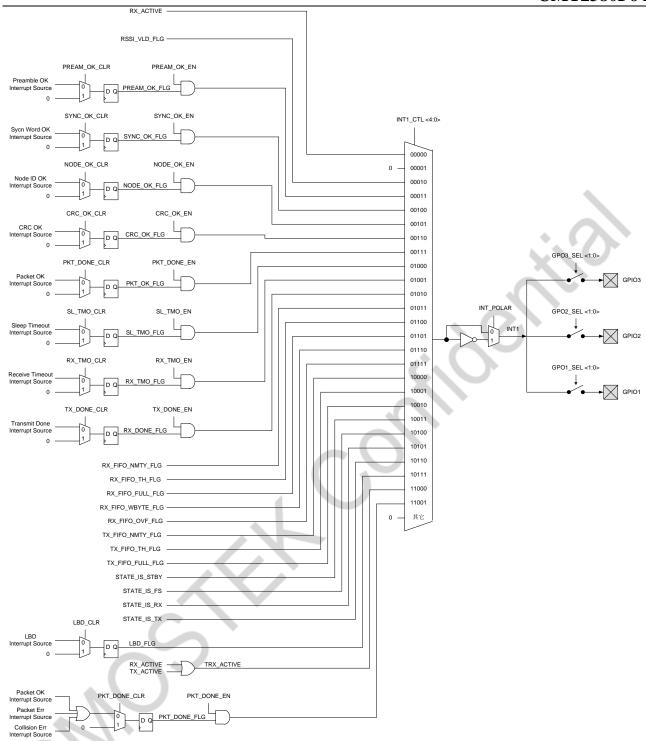

| ACC <sub>HSI</sub>   | temperature drift | VDD=3.3 V, $T_{A}$ = - 10~85 $^{\circ}\mathrm{C}$ , temperature drift  | -2.5 | -   | 2    | %    |