Rev F2, Page 1/39

#### **FEATURES**

- ♦ Integrated Hall sensors with automatic gain and offset control

- ♦ For magnetic scales of 1.0 up to 5.0 mm pole width and diametric magnets

- ♦ Current consumption of only 2 µA to 30 µA in typ. applications

- ◆ Tracking speed of up to 24 m/s (1.5 mm poles) or 15 000 rpm (32 pole pairs)

- ♦ Configurable multiturn counting up to 40 bits

- ♦ Adjustable period count per revolution: FlexCount® logic for 1 to 256 pole pairs

- ♦ Serial, parallel and incremental singleturn operating modes

- ♦ SSI multiturn data output with error, warning, parity, and synchronization bits

- ♦ Multiturn preset by pin or command

- ♦ I<sup>2</sup>C master function for initial boot-up from EEPROM

- ♦ I<sup>2</sup>C slave function for controller operation

- ♦ Supply voltage of 3.0 V to 5.5 V

- ♦ Automatic low-power operation on backup battery

- ♦ Overspeed, battery and RAM (CRC) monitoring

- ♦ Space-saving 16-pin QFN package

#### **APPLICATIONS**

- ♦ Absolute hollow-shaft position encoders

- Absolute on-axis position encoders

- ♦ Gearless revolution counting

- Linear position sensors

- Metering applications

- Battery-powered portable equipment

#### **PACKAGES**

QFN16 4 mm x 4 mm x 0.9 mm RoHS compliant

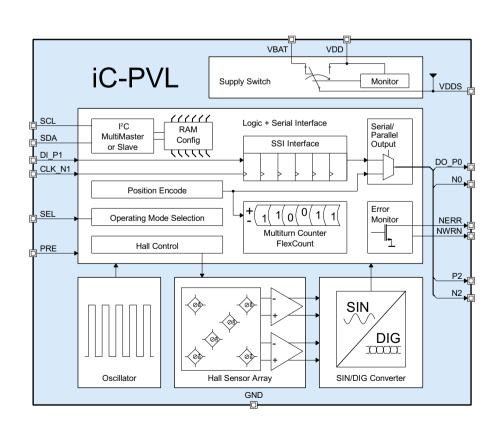

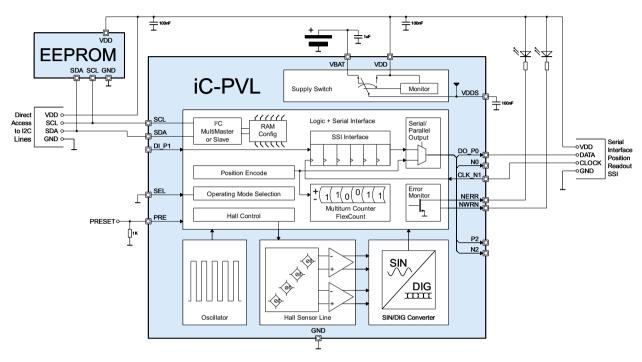

#### **BLOCK DIAGRAM**

Rev F2, Page 2/39

#### **DESCRIPTION**

iC-PVL is an ultra low power magnetic encoder, used for linear and off-axis multiturn position sensing. On main power shutdown, iC-PVL automatically switches to battery supply and continues scanning the position.

iC-PVL operates with pole wheels or linear scales with a pole width of 1.0 mm up to 5.0 mm. Due to various operating modes, iC-PVL can work with iC-Haus singleturn encoders (e.g. iC-MU Series, iC-MHM, iC-MNF, iC-TW29 etc.), as stand-alone SSI or incremental encoder, or links to embedded controllers via I<sup>2</sup>C.

The Hall signal processing stage is designed for ultra low power applications and can be configured to support angular accelerations up to 180 000 rad/s² with 16 magnetic periods per revolution. The maximum magnetic signal frequency is 8 000 Hz. This corresponds to a rotational frequency of 30 000 rpm for magnetic scales with 16 pole pairs. With higher demands on acceleration, the power consumption increases. The maximum supported acceleration is configurable, therefore an optimal trade-off between power consumption and supported acceleration can be individually chosen to meet the demands of the target application.

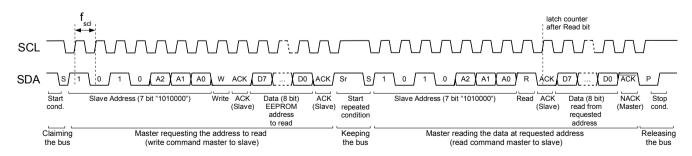

iC-PVL reads its configuration from an external EEP-ROM via an I<sup>2</sup>C interface with multimaster support. Among others, the bit length for multiturn and synchronization data, the interface mode, the maximum supported acceleration and the usage of error or parity bits can be configured. The configuration read-in is triggered by the preset pin PRE. A pulse on this pin resets the device and reads a new configuration from the EEPROM. The multiturn counter is preset to a configurable value (default 0).

The configuration RAM and multiturn counter value are protected against bit errors by an 8 bit CRC. Additionally, an error is generated on excessive speed or acceleration. An integrated battery monitor is used to signalize an empty battery as error. If an error is detected, it is displayed at output NERR and via the error bit in the SSI communication protocol. Additionally, a low battery voltage is indicated at output NWRN. Optionally, this warning can be transmitted in the serial data stream.

Besides linear position encoding, iC-PVL is also used for off-axis scanning of magnetic pole wheels or on-axis scanning of diametric cylindrical magnets. In these applications, a certain number of magnetic north-south field periods may be interpreted as one mechanical revolution. The FlexCount® circuitry offers this functionality. By electrically emulating the characteristics of a gear box, a transmission is freely programmable. For instance, 1-256 magnetic periods can be interpreted as one mechanical revolution.

The iC-PVL multiturn encoder comes in a space-saving QFN16 package. This allows its integration in existing encoder systems or the design of smaller encoders.

#### General notice on application-specific programming

Parameters defined in the datasheet represent supplier's attentive tests and validations, but - by principle - do not imply any warranty or guarantee as to their accuracy, completeness or correctness under all application conditions. In particular, setup conditions, register settings and power-up have to be thoroughly validated by the user within his specific application environment and requirements (system responsibility).

The performance of iC-PVL in application is impacted by system conditions like quality of the magnetic target and its adjustment, field strength and stray fields, temperature and mechanical stress.

Rev F2, Page 3/39

### CONTENTS

| DACKACING INFORMATION                                                     | 4  | I <sup>2</sup> C SLAVE MODE                                           | 27       |

|---------------------------------------------------------------------------|----|-----------------------------------------------------------------------|----------|

| PACKAGING INFORMATION PIN CONFIGURATION                                   | 4  | I-C SLAVE MODE                                                        | 21       |

| QFN16 4 mm x 4 mm (top view)                                              | 4  | MAGNETIC FIELD AMPLITUDE MONITORING                                   | 27       |

| PACKAGE DIMENSIONS QFN16 4x4                                              | 5  | ERROR MONITOR, STATUS AND COMMAND                                     |          |

| ABSOLUTE MAXIMUM RATINGS                                                  | 6  | REGISTER                                                              | 28       |

|                                                                           | _  | Status Register                                                       | 28       |

| THERMAL DATA                                                              | 6  | STUP_ERR: Startup Error                                               | 28       |

| ELECTRICAL CHARACTERISTICS                                                | 7  | CFG_ERR: Internal Configuration Error CTR_ERR: Internal Counter Error | 28<br>28 |

| OPERATING REQUIREMENTS                                                    | 10 | POS_ERR: Position Error                                               | 28       |

| Serial and Parallel Interface                                             | 10 | BAT_ERR: Battery Error                                                | 29       |

|                                                                           | .0 | BAT_WRN: Battery Early Warning                                        | 29       |

| CONFIGURATION PARAMETERS                                                  | 12 | PDR: Power Down Reset Detected                                        | 29       |

|                                                                           | 40 | PRESET: Pin Preset Detected                                           | 29       |

| REGISTER MAP (EEPROM)                                                     | 12 | Extended Status Byte                                                  | 29       |

| REGISTER MAP (iC-PVL during I <sup>2</sup> C slave                        |    | AMPL_ERR: Amplitude Error                                             | 29       |

| mode, ID = 0b1100 001)                                                    | 13 | MAG_ERR: Magnet Error                                                 | 29       |

| DECICIED MAD ('O DVI) decient 120 dece                                    |    | NOMAG_L: NoMagnet Working State (latched)                             | 29       |

| REGISTER MAP (iC-PVL during I <sup>2</sup> C slave mode, ID = 0b1100 000) | 14 | Error Output NERR                                                     | 29       |

| 111000, 15 05 1100 000,                                                   |    | Error Output During Startup                                           | 29       |

| OPERATING MODE SELECTION                                                  | 15 | Warning Output NWRN                                                   | 29       |

| DEVICE MODUNO STATES                                                      | 47 | Command Register                                                      | 29       |

| DEVICE WORKING STATES                                                     | 17 | CURRLY CAMECULAND DATTERY                                             |          |

| STARTUP BEHAVIOR                                                          | 18 | SUPPLY SWITCH AND BATTERY MONITORING                                  | 30       |

| MAGNETIC SCALE SELECTION                                                  | 20 | CURRENT CONSUMPTION IN BATTERY                                        |          |

| COMPENSATION OF ACCEMBLY Date Office                                      |    | MODE                                                                  | 32       |

| COMPENSATION OF ASSEMBLY: Data Offset and Counting Direction              | 22 | Serial Interface Mode (SEL = LOW)                                     | 32       |

| and counting birection                                                    |    | Parallel Encoder Mode (SEL = HIGH)                                    | 33       |

| SERIAL INTERFACE MODE (SEL = LOW)                                         | 23 | OSCILLATOR ERFOLIENCY CALIBRATION                                     | 22       |

| OUTPUTS N0, P2, N2                                                        | 24 | OSCILLATOR FREQUENCY CALIBRATION                                      | 33       |

| 001F013 Nu, F2, N2                                                        | 24 | APPLICATION EXAMPLE: iC-PVL as battery                                |          |

| MULTITURN COUNTER                                                         | 25 | powered revolution counter or metering device                         | 34       |

| PARALLEL ENCODER MODE (SEL = HIGH)                                        | 25 | DESIGN REVIEW: Notes On Chip Functions                                | 35       |

| I <sup>2</sup> C MULTIMASTER INTERFACE AND CRC                            | 26 | REVISION HISTORY                                                      | 36       |

Rev F2, Page 4/39

#### **PACKAGING INFORMATION**

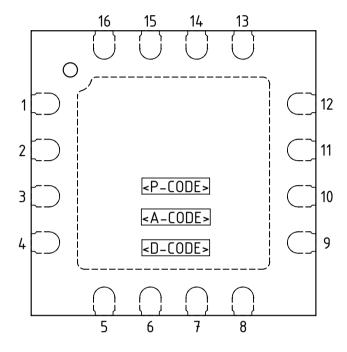

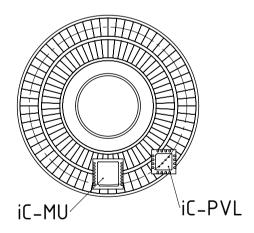

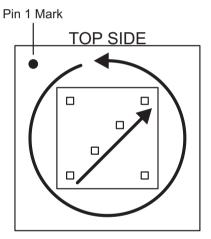

#### **PIN CONFIGURATION** QFN16 4 mm x 4 mm (top view)

### **PIN FUNCTIONS** No. Name Function

| 140. | Name      | i dilction                                                                                                                                                                    |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | SEL       | Mode Select Input <sup>1)</sup> Low: Battery buffered counter with serial readout High: 3 bit parallel complementary output Shorted to PRE input: I <sup>2</sup> C slave mode |

| 2    | PRE       | Preset Trigger Input                                                                                                                                                          |

| 3    | NERR      | Error Output (active low)                                                                                                                                                     |

| 4    | SDA       | I <sup>2</sup> C Interface, Data Line                                                                                                                                         |

| 5    | GND       | Ground                                                                                                                                                                        |

| 6    | VBAT      | Battery Supply Voltage Input (typ. 3.6 V) <sup>2)</sup>                                                                                                                       |

| 7    | VDDS      | Switched Supply Voltage Output                                                                                                                                                |

| 8    | VDD       | +3.0 V to 5.5 V Main Supply Voltage Input                                                                                                                                     |

| 9    | N2        | Parallel Position Output MSB,<br>Incremental Output B,                                                                                                                        |

| 10   | P2        | Parallel Mode Output Bit 2 (neg. logic) Parallel Position Output MSB-1, Incremental Output A,                                                                                 |

| 11   | N0        | Parallel Output Bit 2 (pos. logic) Parallel Position Output LSB, Parallel Mode Output Bit 0 (neg. logic)                                                                      |

| 12   | NWRN      | Battery Warning Output (active low)                                                                                                                                           |

| 13   | DO_P0     | Multiturn Interface, Data Output, Parallel Mode Output Bit 0 (pos. logic)                                                                                                     |

| 14   | CLK_N1    | Multiturn Interface, Clock Line, Parallel Mode Output Bit 1 (neg. logic)                                                                                                      |

| 15   | DI_P1     | Multiturn Interface, Data Input, Parallel Mode Output Bit 1 (pos. logic)                                                                                                      |

| 16   | SCL<br>BP | I <sup>2</sup> C Interface, Clock Line<br>Backside paddle <sup>3)</sup>                                                                                                       |

|      |           |                                                                                                                                                                               |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes);

Do not leave pin open.

Connect pin to VDD if iC-PVL is used without a backup power source (e.g. battery, supercap).

Connecting the backside paddle is recommended by a single link to GND. A current flow across the paddle is not permissible.

Rev F2, Page 5/39

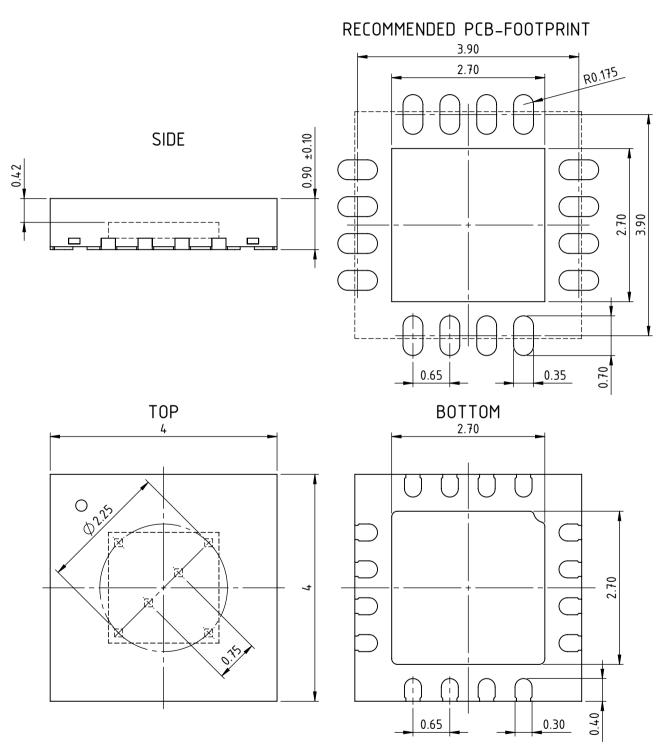

#### **PACKAGE DIMENSIONS QFN16 4x4**

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-220. Tolerance of sensor pattern: ±0.10mm / ±1° (with respect to center of backside pad). dra\_qfn16-4x4-4\_pvl\_0\_pack\_1, 15:1

Rev F2, Page 6/39

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol  | Parameter                                                                         | Conditions                            |       |      | Unit |

|------|---------|-----------------------------------------------------------------------------------|---------------------------------------|-------|------|------|

| No.  | -       |                                                                                   |                                       | Min.  | Max. |      |

| G001 | V(VDD)  | Voltage at VDD                                                                    |                                       | -0.25 | 6    | V    |

| G002 | V(VBAT) | Voltage at VBAT                                                                   | VDD > Von: VBAT < VDD + 1.0 V         | -0.25 | 6    | V    |

| G003 | V(VDDS) | Voltage at VDDS                                                                   |                                       | -0.25 | 6    | V    |

| G004 | V()     | Voltage at SCL, SDA, DI_P1, CLK_N1,<br>DO_P0, N0, NERR, NWRN, P2, N2,<br>PRE, SEL |                                       | -0.25 | 6    | V    |

| G005 | I(VDD)  | Current in VDD                                                                    |                                       | -10   | 50   | mA   |

| G006 | I(VBAT) | Current in VBAT                                                                   |                                       | -10   | 50   | mA   |

| G007 | I(VDDS) | Current in VDDS                                                                   |                                       | -10   | 50   | mA   |

| G008 | I(GND)  | Current in GND                                                                    |                                       | -50   | 10   | mA   |

| G009 | I()     | Current in SCL, SDA, DI_P1, CLK_N1,<br>DO_P0, N0, NERR, NWRN, P2, N2,<br>PRE, SEL |                                       | -30   | 30   | mA   |

| G010 | Vd()    | ESD Susceptibility at All Pins                                                    | HBM, 100 pF discharged through 1.5 kΩ |       | 2    | kV   |

| G011 | Tj      | Junction Temperature                                                              |                                       | -40   | 150  | °C   |

| G012 | Ts      | Storage Temperature Range                                                         |                                       | -40   | 150  | °C   |

#### THERMAL DATA

Operating conditions:

VDD = 3.0...5.5 V, VBAT < VDD + 1.0 V

| Item | Symbol | Parameter                           | Conditions                                                                           |      | Unit |      |     |

|------|--------|-------------------------------------|--------------------------------------------------------------------------------------|------|------|------|-----|

| No.  |        |                                     |                                                                                      | Min. | Тур. | Max. |     |

| T01  | Та     | Operating Ambient Temperature Range | package QFN16                                                                        | -40  |      | 125  | °C  |

| T02  | Rthja  |                                     | QFN16-4x4 surface mounted to PCB according to JEDEC 51 thermal measurement standards |      | 40   |      | K/W |

Rev F2, Page 7/39

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = 3.0...5.5 V, VBAT < VDD + 1.0 V,  $Tj = -40...125 ^{\circ}C$ , fslow calibrated to 34 kHz with IBIAS, unless otherwise stated.

| Item<br>No. | Symbol        | Parameter                                                                               | Conditions                                                                                                                                  | Min. | Тур.                         | Max.                   | Unit                         |

|-------------|---------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|------------------------|------------------------------|

| Total I     | Device        |                                                                                         |                                                                                                                                             |      |                              |                        |                              |

| 001         | V(VDD)        | Permissible Main Supply Voltage                                                         | VDD must never go below GND - 0.25V                                                                                                         | 3.0  |                              | 5.5                    | V                            |

| 002         | I(VDD)        | Supply Current in VDD                                                                   | Tj = 27 °C, no load                                                                                                                         | 1.5  | 4.0                          | 6.0                    | mA                           |

| 003         | V(VBAT)       | Permissible Battery Voltage <sup>1</sup>                                                | if VDD > Von: VBAT < VDD + 1 V                                                                                                              | 3.0  | 3.6                          | 5.5                    | V                            |

| 004         | lavg(VBAT)    | Average Supply Current in VBAT in Battery State                                         | VBAT = 3.6 V, Tj = 27 °C, VDD < Von depending on fmag and A_MAX, see Table 37                                                               | 1    | 10                           | 800                    | μA                           |

| 005         | lavg(VBAT)    | Average Supply Current in VBAT in PowerOn or Sleep State (POWON_ST = 1 or SLEEP_ST = 1) | VBAT = 3.6 V, VDD < Von<br>Tj = 27 °C,<br>Tj = 125 °C,                                                                                      |      | 0.3<br>1.0                   | 1.0<br>3.0             | μA<br>μA                     |

| 006         | Ispike()      | Peak Current in VDD and VBAT                                                            | tspike < 5 µs                                                                                                                               |      | 4.0                          | 10.0                   | mA                           |

| 007         | Vc()hi        | Clamp Voltage hi at All Pins                                                            | Vc()hi = V() - VDDS, I() = +1 mA                                                                                                            | 0.3  | 0.7                          | 1.6                    | V                            |

| 800         | Vc()lo        | Clamp Voltage Io at All Pins                                                            | I() = -1 mA                                                                                                                                 | -1.6 | -0.7                         | -0.25                  | V                            |

| 009         | tconfig       | Power-Up Time After Preset                                                              | VDD > 3 V, initializing from EEPROM<br>start address = 0x00, data valid<br>start address = 0xA0, data valid                                 |      | 12<br>50                     | 20<br>100              | ms<br>ms                     |

| 010         | C(VBAT)       | External Bypass Capacitor at Pin VBAT                                                   | ceramic capacitor placed as close as possible to the pin                                                                                    | 1    |                              |                        | μF                           |

| 011         | C(VDDS)       | External Bypass Capacitor at Pin VDDS <sup>1</sup>                                      | ceramic capacitor placed as close as possible to the pin                                                                                    | 100  |                              |                        | nF                           |

| 012         | C(VDD)        | External Bypass Capacitor at Pin VDD <sup>1</sup>                                       | ceramic capacitor placed as close as possible to the pin                                                                                    | 100  |                              |                        | nF                           |

| Magne       | etic Signal C | conditioning                                                                            |                                                                                                                                             |      |                              |                        |                              |

| 101         | Hext          | Permissible Magnetic Field<br>Strength <sup>1</sup>                                     | at chip surface                                                                                                                             | 10   |                              | 100                    | kA/m                         |

| 102         | Bext          | Permissible Magnetic Flux Density                                                       | at chip surface in air                                                                                                                      | 12.5 |                              | 125                    | mT                           |

| 103         | fmag          | Magnetic Input Frequency                                                                | VDDS = 3.0 V, tested via electrical input                                                                                                   |      |                              | 8                      | kHz                          |

| 104         | frot          | Permissible Rotation of Pole<br>Wheel with                                              | 16 pole pairs<br>32 pole pairs<br>64 pole pairs                                                                                             |      |                              | 30000<br>15000<br>7500 | rpm<br>rpm<br>rpm            |

| 105         | vmax          | Permissible Movement Speed (Linear)                                                     | 1.5 mm pole width (3 mm magnetic period)                                                                                                    |      |                              | 24                     | m/s                          |

| 106         | dsens         | Diameter of Hall Sensor Circle                                                          | measured from center of each Hall plate,<br>ONAX = 1                                                                                        |      | 2.25                         |                        | mm                           |

| 107         | hpac          | Sensor-to-Package-Surface<br>Distance                                                   | QFN16                                                                                                                                       |      | 0.4                          |                        | mm                           |

| 108         | Ht            | Differential Magnetic Field<br>Strength Working Threshold for<br>Position Tracking      | ATHR = 0x00 ATHR = 0x01 ATHR = 0x02 ATHR = 0x03 device is in NoMagnet working state if field strength (at chip surface) is below this value |      | 2.5<br>1.25<br>0.625<br>5.0  |                        | kA/m<br>kA/m<br>kA/m<br>kA/m |

| 109         | Bt            | Differential Magnetic Flux Density<br>Working Threshold for Position<br>Tracking        | ATHR = 0x00 ATHR = 0x01 ATHR = 0x02 ATHR = 0x03 flux value at chip surface in air                                                           |      | 3.13<br>1.56<br>0.78<br>6.25 |                        | mT<br>mT<br>mT<br>mT         |

| Oscill      | ator Freque   | i e                                                                                     | ,                                                                                                                                           |      |                              |                        |                              |

| 301         | fslow         | Slow Oscillator Frequency                                                               | calibrated to 34 kHz with IBIAS                                                                                                             | 32   | 34                           | 36                     | kHz                          |

| 302         | ffast         | Fast Oscillator Frequency                                                               | fslow calibrated with IBIAS                                                                                                                 | 4.0  | 6.0                          | 8.0                    | MHz                          |

| Suppl       | y and Batter  | y Monitoring                                                                            |                                                                                                                                             |      |                              |                        |                              |

| 401         | Von           | Switch to VDD Supply (VDD Power On)                                                     | increasing voltage at VDD; VBAT > 3.0 V                                                                                                     | 2.8  | 2.9                          | 3.0                    | V                            |

$<sup>^{\</sup>rm 1}$  For iC-PVL X1: Please refer to the design review on p. 35.

Rev F2, Page 8/39

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions:

VDD = 3.0...5.5 V, VBAT < VDD + 1.0 V, Tj = -40...125 °C, fslow calibrated to 34 kHz with IBIAS, unless otherwise stated.

| Item<br>No. | Symbol              | Parameter                                       | Conditions                                                           | Min.                         | Тур.                         | Max.                             | Unit        |

|-------------|---------------------|-------------------------------------------------|----------------------------------------------------------------------|------------------------------|------------------------------|----------------------------------|-------------|

| 402         | Voff                | Switch Back to Battery Supply (VDD Power Off)   | decreasing voltage at VDD; VBAT > 3.0 V                              | 2.7                          | 2.8                          | 2.9                              | V           |

| 403         | Vhys                | Hysteresis (VDD Switch)                         | Vhys = Von - Voff                                                    | 25                           | 100                          | 150                              | mV          |

| 404         | Vt()err             | Battery Monitoring Error<br>Threshold Voltage   | BAT_THR = "11"<br>BAT_THR = "10"<br>BAT_THR = "01"<br>BAT_THR = "00" | 2.65<br>2.75<br>2.85<br>2.95 | 2.75<br>2.85<br>2.95<br>3.05 | 2.85<br>2.95<br>3.05<br>3.15     | V<br>V<br>V |

| 405         | Vt()wrn             | Battery Monitoring Warning<br>Threshold Voltage | BAT_THR = "11" BAT_THR = "10" BAT_THR = "01" BAT_THR = "00"          | 2.75<br>2.85<br>2.95<br>3.05 | 2.85<br>2.95<br>3.05<br>3.15 | 2.975<br>3.075<br>3.175<br>3.275 | V<br>V<br>V |

| 406         | Vew                 | Difference Battery Error-to-Warning             | ΔVew = Vt()wrn - Vt()err                                             | 40                           | 100                          | 175                              | mV          |

| Digita      | Outputs: [          | DI_P1, CLK_N1, DO_P0, N0, P2, N                 | 12                                                                   | U .                          |                              |                                  |             |

| 501         | Vs()hi              | Saturation Voltage hi                           | Vs()hi = VDDS - V(), I() = -1.6 mA                                   | 0.05                         |                              | 0.4                              | V           |

| 502         | Vs()lo              | Saturation Voltage lo                           | I() = 1.6 mA                                                         | 0.05                         |                              | 0.4                              | V           |

| 503         | lsc()hi             | Short-Circuit Current hi                        | VDDS = 3.0 V, V() = GND                                              | -15                          |                              | -4                               | mA          |

| 504         | lsc()lo             | Short-Circuit Current lo                        | VDDS = 3.0 V, V() = VDDS                                             | 4                            |                              | 15                               | mA          |

| 505         | tr()                | Rise Time                                       | CL = 30 pF                                                           |                              |                              | 50                               | ns          |

| 506         | tf()                | Fall Time                                       | CL = 30 pF                                                           |                              |                              | 50                               | ns          |

| EEPR        | OM Interfac         | e: SCL, SDA                                     | 1                                                                    | U                            |                              |                                  | II.         |

| 601         | Vt()hi              | Input Threshold Voltage hi                      |                                                                      |                              | 1.7                          | 2                                | V           |

| 602         | Vt()lo              | Input Threshold Voltage lo                      |                                                                      | 0.8                          | 1.4                          |                                  | V           |

| 603         | Vt()hys             | Input Hysteresis                                | Vt()hys = Vt()hi - Vt()lo                                            | 75                           | 200                          | 500                              | mV          |

| 604         | Vs()lo              | Saturation Voltage lo                           | I() = 1.6 mA                                                         | 0.05                         |                              | 0.4                              | V           |

| 605         | lsc()lo             | Short-Circuit Current lo                        | VDDS = 3.0 V, V() = VDDS                                             | 8                            |                              | 30                               | mA          |

| 606         | lpu()               | Pull-Up Current                                 | V() = 0 VVDDS - 1 V                                                  | -1000                        | -300                         | -30                              | μA          |

| 607         | fclk(SCL)           | I <sup>2</sup> C Output Frequency at SCL        |                                                                      |                              | f <sub>fast</sub> / 128      |                                  | kHz         |

| Error       | Monitoring          | Output: NERR, NWRN                              |                                                                      | "                            |                              |                                  | "           |

| 701         | Vs()lo              | Saturation Voltage lo                           | I() = 1.6 mA                                                         | 0.05                         |                              | 0.4                              | V           |

| 702         | lsc()lo             | Short-Circuit Current lo                        | VDDS = 3.0 V, V() = VDDS                                             | 4                            |                              | 15                               | mA          |

| Digita      | l Inputs: DI        | P1, CLK_N1                                      |                                                                      | "                            |                              |                                  |             |

| 801         | Vt()hi              | Threshold Voltage hi                            |                                                                      |                              | 1.7                          | 2                                | V           |

| 802         | Vt()lo              | Threshold Voltage Io                            |                                                                      | 0.8                          | 1.4                          |                                  | V           |

| 803         | Vt()hys             | Hysteresis                                      | Vt()hys = Vt()hi - Vt()lo                                            | 75                           | 200                          | 500                              | mV          |

| 804         | lpd()               | Pull-Down Current                               | V() = 1 VVDDS                                                        | 2                            | 30                           | 100                              | μA          |

| Mode        | Select Inpu         | t: SEL                                          |                                                                      |                              |                              |                                  |             |

| 901         | Vt()hi              | Threshold Voltage hi                            |                                                                      |                              | 1.7                          | 2                                | V           |

| 902         | Vt()lo              | Threshold Voltage lo                            |                                                                      | 0.8                          | 1.4                          |                                  | V           |

| 903         | Vt()hys             | Hysteresis                                      | Vt()hys = Vt()hi - Vt()lo                                            | 75                           | 200                          | 500                              | mV          |

| Preset      | t Input: PRE        | <u> </u>                                        |                                                                      |                              |                              |                                  |             |

| A01         | Vt()hi              | Threshold Voltage hi                            |                                                                      |                              | 60                           | 75                               | %VDD        |

| A02         | Vt()lo              | Threshold Voltage lo                            |                                                                      | 30                           | 40                           |                                  | %VDD        |

| A03         | Vt()hys             | Hysteresis                                      | Vt()hys = Vt()hi - Vt()lo                                            | 0.7                          | 1.0                          | 1.4                              | V           |

| A04         | lpd()               | Pull-Down Current                               | V() = 1 VVDDS, SEL = GND                                             | 10                           | 120                          | 300                              | μA          |

| A05         | t <sub>preset</sub> | Length of Preset Pulse on PRE<br>Pin            |                                                                      | 2                            |                              |                                  | μs          |

| Serial      | Interface to        | Singleturn Sensor, SSI and Cha                  | in Mode                                                              |                              | -                            |                                  |             |

| B01         | tp()                | Propagation Delay:<br>Clock Edge vs. DO Output  |                                                                      | 10                           |                              | 100                              | ns          |

| B02         | tout                | Timeout                                         | fslow calibrated via IBIAS                                           | 15                           | 25                           | 35                               | μs          |

|             |                     |                                                 |                                                                      |                              |                              |                                  |             |

Rev F2, Page 9/39

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions:

VDD = 3.0...5.5 V, VBAT < VDD + 1.0 V, Tj = -40...125 °C, fslow calibrated to 34 kHz with IBIAS, unless otherwise stated.

| ltem    | Symbol       | Parameter                         | Conditions    |      |      | Unit |    |

|---------|--------------|-----------------------------------|---------------|------|------|------|----|

| No.     |              |                                   |               | Min. | Тур. | Max. |    |

| Paralle | el Encoder I | Mode                              |               |      |      |      |    |

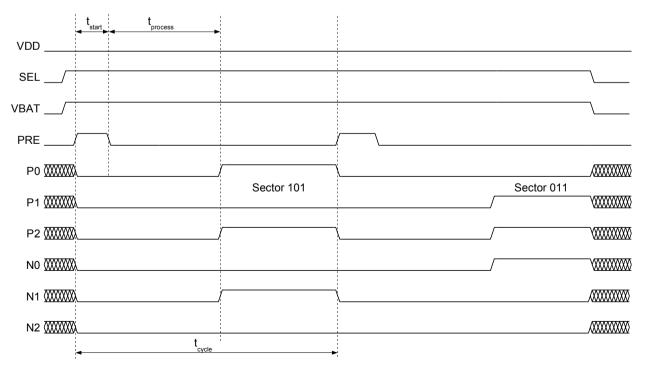

| C01     | tprocess     | Processing Time (Parallel Output) | see Figure 14 |      | 10   | 30   | μs |

| 00.     | tp:0000      | Tresecting Time (Farance Suspan)  | See Figure 11 |      |      |      | l  |

Rev F2, Page 10/39

#### **OPERATING REQUIREMENTS: Serial and Parallel Interface**

Operating conditions:

VDD = 3.0...5.5 V, VBAT < VDD + 1.0 V, Tj = -40...125 °C, fslow calibrated to 34 kHz with IBIAS, unless otherwise stated.

| Item                 | Symbol             | Parameter                                       | Conditions                                                  | 1                       |                   | Unit |

|----------------------|--------------------|-------------------------------------------------|-------------------------------------------------------------|-------------------------|-------------------|------|

| No.                  | -                  |                                                 |                                                             | Min.                    | Max.              |      |

| Serial               | Interface S        | SI Mode                                         |                                                             |                         |                   |      |

| 1001                 | t <sub>wait</sub>  | SSI Request after VDD Power-on                  |                                                             | 10                      |                   | μs   |

| 1002                 | t <sub>req</sub>   | Request Signal lo Level Duration                |                                                             | 250                     |                   | ns   |

| 1003                 | t <sub>C</sub>     | Permissible Clock Period                        | due to Elec. Char. B02                                      | 500                     | $2 \cdot t_{out}$ | ns   |

| 1004                 | $f_C$              | Permissible Clock Frequency                     | missible Clock Frequency due to Elec. Char. B02             |                         | 2                 | MHz  |

| 1005                 | t <sub>L1</sub>    | Clock Signal hi Level Duration                  | ock Signal hi Level Duration                                |                         |                   | ns   |

| 1006                 | t <sub>L2</sub>    | Clock Signal lo Level Duration                  |                                                             | 250                     |                   | ns   |

| 1007                 | t <sub>frame</sub> | Cyclic Multiturn Data Frame Request Interval    |                                                             | 85                      |                   | μs   |

| I <sup>2</sup> C Sla | ve Mode D          | irect Access                                    |                                                             |                         |                   |      |

| I010                 | t <sub>C</sub>     | Permissible Clock Period                        | due to Elec. Char. B02                                      |                         |                   |      |

| 1011                 | t <sub>wait</sub>  | I <sup>2</sup> C Request after VDD Power-on     |                                                             | 10                      |                   | μs   |

| 1012                 | f <sub>scl</sub>   | Permissible Input Clock Frequency               | I <sup>2</sup> C standard mode with timeout Elec. Char. B02 | 1/(2·t <sub>out</sub> ) | 100               | kHz  |

| Paralle              | l Encoder          | Mode (SEL = High)                               |                                                             |                         |                   |      |

| 1013                 | t <sub>start</sub> | Length of Start Pulse on PRE Pin                | see Figure 14 on Page 25                                    | 2                       |                   | μs   |

| 1014                 | t <sub>cycle</sub> | Time Between Two Consecutive Sensor Read Cycles | see Figure 14 on Page 25                                    | 30                      |                   | μs   |

| Serial               | Interface C        | hain Mode                                       |                                                             |                         |                   |      |

| 1015                 | $f_{C}$            | Permissible Clock Frequency                     | due to Elec. Char. B02                                      | 1/(2·t <sub>out</sub> ) | 1                 | MHz  |

| I016                 | t <sub>C</sub>     | Permissible Clock Period                        | due to Elec. Char. B02                                      | 1                       | 2·tout            | μs   |

| 1017                 | t <sub>L1</sub>    | Clock Signal hi Level Duration                  |                                                             | 500                     |                   | ns   |

| 1018                 | t <sub>L2</sub>    | Clock Signal lo Level Duration                  |                                                             | 500                     |                   | ns   |

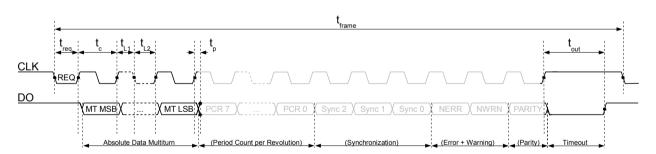

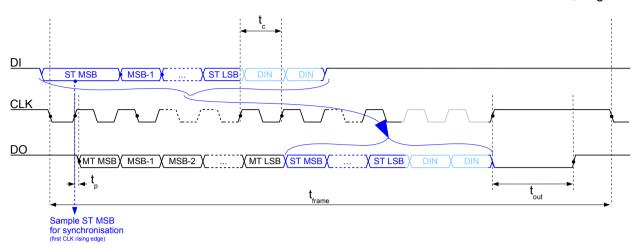

Figure 1: I/O line signals of the serial interface in SSI mode (INT\_MODE = 0)

Rev F2, Page 11/39

Figure 2: I/O line signals of the serial interface in Chain Mode (INT\_MODE = 1). **Note:** Chain Mode can only be used in specific system setups. Extended system requirements apply.

Rev F2, Page 12/39

#### **CONFIGURATION PARAMETERS**

**Hall Sensor Signal Conditioning**

DIR: Code Direction (P. 22)

OS: Electrical Offset Multiturn to Singleturn

(P. 22)

**Serial Interface**

INT\_MODE: Serial Interface Operating Mode (P. 23)

MT\_GRAY: Multiturn Output Data Format (P. 23)

ST\_GRAY: Singleturn Input Data Format (P. 23)

MT\_BW: Bit Width of Multiturn Data and Counter

(P. 23)

SYNC\_BW: Synchronization Bit Width (P. 23)

PCR: Period Count per Revolution (P. 21)

PCR OUT: PCR Output Mode (P. 21)

EN\_ERR: Error Bit Transmission Enable (P. 24)

EN PAR: Parity Bit Transmission Enable (P. 24)

**Bias and Oscillators**

IBIAS: Bias Current; Oscillator Frequency

Calibration (P. 33)

A\_MAX: Maximum Angle Acceleration (P. 32)

**Battery Monitor**

BAT\_MON: Battery Monitoring Enable (P. 30)

EN\_WRN: Low Battery Warning Enable (P. 24)

BAT\_THR: Battery Monitor Thresholds (P. 31)

Miscellaneous

POLEWID: Pole Size of Magnetic Scale (P. 20)

ONAX: On-Axis Magnetic Scanning (P. 21)

ABQUAD: AB Quadrature Output (P. 24)

HYS: Hysteresis (P. 24)

I2C\_POS: Enable I<sup>2</sup>C Position Readout (P. 27) MT\_PREL: Multiturn Counter Preload Value (P. 25)

CHIP\_REL: Chip Release (P. 27)

ATHR: Field Amplitude Threshold Value (P. 28)

NOMAG: NoMagnet Detection (P. 28)

**CRC Checksums**

CRC CFG: Checksum for Chip Configuration

(0x00-0x05) (P. 26)

CRC CTR: Checksum for MT PREL (0x07-0x0B)

(P. 26)

#### **REGISTER MAP (EEPROM)**

| OVERV     | OVERVIEW        |               |       |        |           |         |         |          |  |  |  |

|-----------|-----------------|---------------|-------|--------|-----------|---------|---------|----------|--|--|--|

| Addr      | Bit 7           | Bit 6         | Bit 5 | Bit 4  | Bit 3     | Bit 2   | Bit 1   | Bit 0    |  |  |  |

| Interface | and Hall Sig    | nal Processin | ıg    |        |           |         |         |          |  |  |  |

| 0x00      | EN_             | PAR           | EN_   | ERR    | DIR       | ST_GRAY | MT_GRAY | INT_MODE |  |  |  |

| 0x01      |                 | os            |       |        |           | MT_BW   |         |          |  |  |  |

| 0x02      | PCR             |               |       |        |           |         |         |          |  |  |  |

| Battery   | Monitor, Bias   | and Oscillato | rs    |        |           |         |         |          |  |  |  |

| 0x03      | EN_WRN          | BAT_MON       |       | A_MAX  |           |         | IBIAS   |          |  |  |  |

| Miscella  | Miscellaneous   |               |       |        |           |         |         |          |  |  |  |

| 0x04      | 0               | NON           | ЛAG   | AT     | HR        | ONAX    | POLE    | EWID     |  |  |  |

| 0x05      | I2C_POS         | PCR_OUT       | SYNC  | C_BW   | BAT_      | _THR    | HYS     | ABQUAD   |  |  |  |

| CRC Co    | nfiguration (ir | nverted)      |       |        |           |         |         |          |  |  |  |

| 0x06      |                 |               |       | CRC_C  | FG(7:0)   |         |         |          |  |  |  |

| Multituri | n Counter: Pr   | eload Value   |       |        |           |         |         |          |  |  |  |

| 0x07      |                 |               |       | MT_PR  | EL(7:0)   |         |         |          |  |  |  |

| 0x08      |                 |               |       | MT_PRI | EL(15:8)  |         |         |          |  |  |  |

| 0x09      |                 |               |       | MT_PRE | EL(23:16) |         |         |          |  |  |  |

| 0x0A      | MT_PREL(31:24)  |               |       |        |           |         |         |          |  |  |  |

| 0x0B      |                 |               |       | MT_PRE | EL(39:32) |         |         |          |  |  |  |

| CRC Co    | unter (inverte  | d)            |       |        |           |         |         |          |  |  |  |

| 0x0C      |                 |               |       | CRC_C  | TR(7:0)   |         |         |          |  |  |  |

Rev F2, Page 13/39

### REGISTER MAP (iC-PVL during I<sup>2</sup>C slave mode, ID = 0b1100 001)

| OVERV                        | 'IEW                                          |                                                                                     |               |          |                             |         |           |          |  |  |

|------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------|---------------|----------|-----------------------------|---------|-----------|----------|--|--|

| Addr                         | Bit 7                                         | Bit 6                                                                               | Bit 5         | Bit 4    | Bit 3                       | Bit 2   | Bit 1     | Bit 0    |  |  |

| Interface                    | e and Hall Sig                                | nal Processir                                                                       | ng            |          |                             |         |           |          |  |  |

| 0x00                         | EN_                                           | PAR                                                                                 | EN_           | ERR      | DIR                         | ST_GRAY | MT_GRAY   | INT_MODE |  |  |

| 0x01                         |                                               | OS                                                                                  |               |          |                             | MT_BW   |           |          |  |  |

| 0x02                         |                                               |                                                                                     |               | PC       | CR                          |         |           |          |  |  |

| Battery                      | Monitor, Bias                                 | and Oscillato                                                                       | ors           |          |                             |         |           |          |  |  |

| 0x03                         | EN_WRN                                        | BAT_MON                                                                             |               | A_MAX    |                             |         | IBIAS     |          |  |  |

| Miscellaneous                |                                               |                                                                                     |               |          |                             |         |           |          |  |  |

| 0x04                         | 0                                             | NON                                                                                 | MAG           | AT       | HR                          | ONAX    | POLI      | EWID     |  |  |

| 0x05                         | I2C_POS                                       | PCR_OUT                                                                             | SYNC          | C_BW     | BAT_                        | THR     | HYS       | ABQUAD   |  |  |

| CRC Configuration (inverted) |                                               |                                                                                     |               |          |                             |         |           |          |  |  |

| 0x06 CRC_CFG(7:0)            |                                               |                                                                                     |               |          |                             |         |           |          |  |  |

| Multitur                     | n Counter: Cu                                 | Counter: Current Count (PCR_OUT = 0) Multiturn Counter: Current Count (PCR_OUT = 1) |               |          |                             |         |           |          |  |  |

| 0x07                         |                                               |                                                                                     | JNT(7:0)      |          |                             |         | PCR(7:0)  |          |  |  |

| 0x08                         |                                               | MT_COL                                                                              |               |          |                             |         | JNT(7:0)  |          |  |  |

| 0x09                         |                                               |                                                                                     | NT(23:16)     |          |                             |         | JNT(15:8) |          |  |  |

| 0x0A                         |                                               |                                                                                     | NT(31:24)     |          |                             |         | NT(23:16) |          |  |  |

| 0x0B                         |                                               | MT_COU                                                                              | NT(39:32)     |          |                             | MT_COU  | NT(31:24) |          |  |  |

|                              | unter (inverte                                | d)                                                                                  |               |          |                             |         |           |          |  |  |

| 0x0C                         |                                               | •                                                                                   |               | CRC_C    | TR(7:0)                     |         |           |          |  |  |

| -                            | nization Bits                                 | 1                                                                                   |               |          |                             |         |           |          |  |  |

| 0x0D                         | 0                                             | 0                                                                                   | 0             | 0        | 0                           |         | SYNC(2:0) |          |  |  |

| 0x0E                         |                                               |                                                                                     |               | Rese     | erved                       |         |           |          |  |  |

|                              | lease (I <sup>2</sup> C sla                   | ve mode read                                                                        | only)         |          |                             |         |           |          |  |  |

| 0x0F                         |                                               |                                                                                     |               | CHIP     | _REL                        |         |           |          |  |  |

|                              | s Register (I <sup>2</sup> C slave mode only) |                                                                                     |               |          |                             |         |           |          |  |  |

| 0x10                         | PRESET                                        | PDR                                                                                 | BAT_WRN       | BAT_ERR  | POS_ERR                     | CTR_ERR | CFG_ERR   | STUP_ERR |  |  |

|                              | nd Register (I                                | <sup>2</sup> C slave mod                                                            | e write only) |          |                             |         |           |          |  |  |

| 0x11                         |                                               |                                                                                     |               |          | 0(7:0)                      |         |           |          |  |  |

|                              |                                               |                                                                                     | ing States an | -        | Monitor (I <sup>2</sup> C s |         | 1         |          |  |  |

| 0x12                         | SLEEP_ST                                      | NOMAG_ST                                                                            | ACTIVE_ST     | POWON_ST | Unused                      | NOMAG_L | MAG_ERR   | AMPL_ERR |  |  |

Table 6: Register map during I<sup>2</sup>C slave mode

Rev F2, Page 14/39

### REGISTER MAP (iC-PVL during I<sup>2</sup>C slave mode, ID = 0b1100 000)

| OVERV                                              | OVERVIEW                                                                                             |                          |               |          |         |         |         |          |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------|---------------|----------|---------|---------|---------|----------|--|--|--|--|

| Addr                                               | Bit 7                                                                                                | Bit 6                    | Bit 5         | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0    |  |  |  |  |

| Status Register (I <sup>2</sup> C slave mode only) |                                                                                                      |                          |               |          |         |         |         |          |  |  |  |  |

| 0x00                                               | PRESET                                                                                               | PDR                      | BAT_WRN       | BAT_ERR  | POS_ERR | CTR_ERR | CFG_ERR | STUP_ERR |  |  |  |  |

| Comma                                              | nd Register (I                                                                                       | <sup>2</sup> C slave mod | e write only) |          |         |         |         |          |  |  |  |  |

| 0x01                                               |                                                                                                      |                          |               | CMD      | (7:0)   |         |         |          |  |  |  |  |

| Extende                                            | Extended Status Register for Working States and Amplitude Monitor (I <sup>2</sup> C slave mode only) |                          |               |          |         |         |         |          |  |  |  |  |

| 0x02                                               | SLEEP_ST                                                                                             | NOMAG_ST                 | ACTIVE_ST     | POWON_ST | Unused  | NOMAG_L | MAG_ERR | AMPL_ERR |  |  |  |  |

Table 7: Register map during I<sup>2</sup>C slave mode

Rev F2, Page 15/39

#### **OPERATING MODE SELECTION**

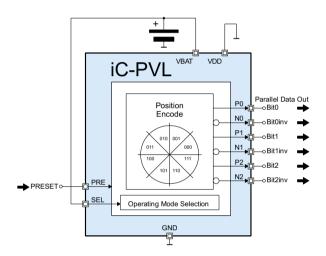

The input SEL defines the operating mode of iC-PVL. For the default application as battery buffered multiturn counter with serial position readout (SSI Interface), it is mandatory to connect the SEL input to GND potential. In case a three bit parallel and differential position output is desired, a high state at SEL input selects a parallel encoder mode. It is mandatory to connect SEL to a defined high or low potential.

IC-PVL

SCL

FC

RAM

SDA

MultiMaster

and Slave

NT\_MODE=0

SSI Data Out

DI

SSI Clock In

CLK

PRESETO

PRESETO

PRESETO

Operating Mode Selection

GND

GND

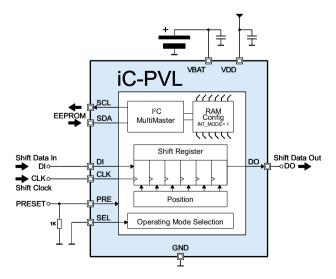

Figure 3: SEL = low: serial interface SSI mode

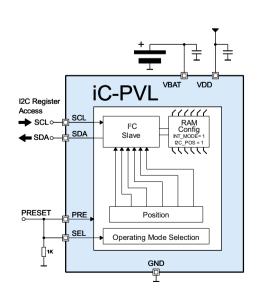

An additional operating mode is activated when SEL is shorted to input PRE. In this mode, the preset pulse does not trigger an EEPROM readout. iC-PVL now behaves as I<sup>2</sup>C slave and all registers (configuration, position, status and command registers) are accessible via I<sup>2</sup>C device ID = 0b1100 001 (see Table 6).

The register layout visible via I<sup>2</sup>C is shown on page 13 for each particular address. Please note that some addresses are read only.

Figure 4: SEL = high: parallel encoder mode

Figure 5: SEL = PRE: I<sup>2</sup>C slave mode

Figure 6: SEL = low: serial interface chain mode.

Note: Chain Mode can only be used in specific system setups. Extended system requirements apply.

Rev F2, Page 16/39

| <b>OPERATING</b>                           | G MODE SELECTION                                                                                 | N              |                                         |                                        |                                      |                                                                      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------|----------------|-----------------------------------------|----------------------------------------|--------------------------------------|----------------------------------------------------------------------|

| Operating<br>Mode                          | Description                                                                                      | Pin SEL        | Parameter<br>INT_MODE<br>(see Table 16) | Parameter<br>I2C_POS<br>(see Table 27) | I <sup>2</sup> C Slave<br>Function   | I <sup>2</sup> C Master<br>Function<br>(Read E2P cfg)                |

| SSI Mode<br>(Fig. 3)                       | Battery buffered counter with serial readout.                                                    | low            | 0                                       | 0                                      | yes<br>(without position<br>readout) | only after preset<br>pulse* or I <sup>2</sup> C<br>command<br>REBOOT |

| I <sup>2</sup> C Slave<br>mode<br>(Fig. 5) | iC-PVL operates<br>as I <sup>2</sup> C slave, ID =<br>0b1100 001.                                | Shorted to PRE | 0                                       | 1                                      | yes<br>(with position<br>readout)    | only after I <sup>2</sup> C<br>command<br>REBOOT                     |

| Parallel<br>Mode<br>(Fig. 4)               | 3 bit Parallel<br>Encoder Mode,<br>complementary<br>output.                                      | high           | -                                       | -                                      | -                                    | -                                                                    |

| Chain<br>Mode<br>(Fig. 6)                  | Battery buffered counter with serial readout.                                                    | low            | 1                                       | 0                                      | no                                   | only after preset pulse                                              |

|                                            | Note: Chain Mode can only be used in specific system setups. Extended system requirements apply. |                |                                         |                                        |                                      |                                                                      |

Table 8: Operating mode selection, configuration settings, available functions

<sup>\*</sup> For iC-PVL W4 or newer: Please refer to the design review on p. 35.

Rev F2, Page 17/39

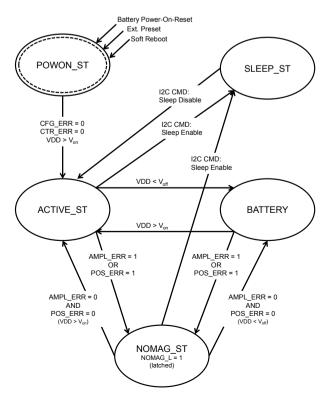

#### **DEVICE WORKING STATES**

The iC-PVL operates in different working states according to its configuration and the environmental conditions, especially regarding power supply and magnetic field strength. Table 9 and Figure 7 show their main characteristics and the transitions between the states. These working states do not apply to the Parallel Encoder Operating Mode.

| Working<br>State | VDD<br>Supply | Description                                                                                             | Position<br>Tracking    | Position<br>Readout | Status<br>Indication | I(VDD) | I(VBAT)                 |

|------------------|---------------|---------------------------------------------------------------------------------------------------------|-------------------------|---------------------|----------------------|--------|-------------------------|

| PowerOn          | Off           | Security state after reset/preset                                                                       | Off                     | No                  |                      | 0 mA   | typ. 300nA,<br>max. 3µA |

| PowerOn          | On            | Security state after reset/preset                                                                       | Off                     | No                  | Error                | 1 mA   | 0 mA                    |

| Active           | On            | Normal operation using VDD supply, backup battery is connected                                          | High speed Yes 4 mA 0 n |                     | 0 mA                 |        |                         |

| Battery          | Off           | Backup operation using VBAT supply, current consumption depends on rotational speed and parameter A_MAX | High speed capable      | Not<br>possible     |                      | 0 mA   | 1-800 μΑ                |

| NoMagnet         | On            | Low magnetic field amplitude detected                                                                   | Low speed               | Yes                 | Error                | 1 mA   | 0 mA                    |

| NoMagnet         | Off           | Low magnetic field amplitude detected, current consumption defined by parameter A_MAX                   | Low speed No 0 mA       |                     | 1-50 μΑ              |        |                         |

| Sleep            | On            | Sleep state activated via command                                                                       | Off                     | No                  | Error                | 1 mA   | 0 mA                    |

| Sleep            | Off           | Sleep state activated via command                                                                       | Off                     | No                  |                      | 0 mA   | typ. 300nA,<br>max. 3µA |

Table 9: Definition of device working states

In states were position readout is marked with <no>, the read action via serial interface SSI/I2C is possible, but the read position is invalid. I.e. the interfaces answers with all position bits = '1'. I2C communication for register operation is possible in all states when VDD supply is on (VDD >  $V_{on}$ ). For values of  $V_{on}$  and  $V_{off}$  refer to Elec. Char. No. 401 and 402.

Figure 7: State Diagram

Rev F2, Page 18/39

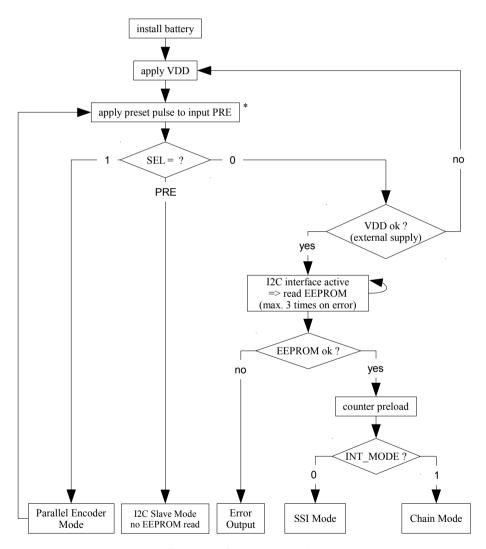

#### **STARTUP BEHAVIOR**

As shown in chapter OPERATING MODE SELECTION, iC-PVL can be booted up in four distinct operating modes. These are the SSI Mode, the Parallel Encoder Mode, the I<sup>2</sup>C Slave Mode and the Chain Mode, respectively. Via SEL, the operating mode is selected according to Table 8. In case of a faulty startup procedure, an error is indicated at pin NERR.

Figure 8 shows the startup procedure of iC-PVL. The procedure starts when a battery supply is available. This would be the case if a battery is newly attached to the encoder system or the battery supply is switched on by an external microcontroller. Alternatively VDD can be connected first followed by connecting the battery. Active battery errors can be removed using the SCLR command.

Figure 8: Startup behavior

#### SSI Mode (SEL = low)

For V(VDD) >  $V_{on}$  during the initial startup in SSI mode, a preset pulse is mandatory\* and triggers EEPROM readout. VDD supply has to remain above  $V_{on}$  for at least  $t_{config}$ . The I<sup>2</sup>C multimaster tries to read the configuration data from an EEPROM connected to SCL and SDA. When the data is read without errors, the iC-PVL

operates in SSI Mode or Chain Mode according to the configuration bit INT\_MODE and stays in this operating mode as long as the battery supply is above  $V_{off}$ . After a third faulty attempt, EEPROM readout is stopped and an error is indicated at pin NERR. Both serial interface modes are further explained on Page 23.

<sup>\*</sup> For iC-PVL W4 or newer: Please refer to the design review on p. 35

Rev F2, Page 19/39

$I^2C$  communication is possible in this operating mode, but position readout via SSI or  $I^2C$  is exclusive (refer to  $I^2C$  SLAVE MODE on Page 27).

#### $I^2C$ slave mode (SEL = PRE)

For V(VDD) >  $V_{on}$  during the initial startup in I<sup>2</sup>C mode, a preset pulse applied simultaneously to the SEL and PRE pin (refer to Figure 5) will set position readout to I<sup>2</sup>C (setting of I<sup>2</sup>C\_POS is ignored in this case) and suppress a potential EEPROM readout. If this function-

ality is not required, the preset pulse can be omitted. iC-PVL responds to the  $I^2C$  device ID = 0b1100001.

#### Parallel Encoder Mode (SEL = high)

In Parallel Encoder Mode, an external microcontroller can activate the iC-PVL via the PRE pin in distinct intervals to acquire the current position. The encoded position is valid when all complementary bits have changed their logic value (see Figure 14). After successful position readout, iC-PVL is in ultra low power idle mode. The battery supply may then be switched off.

Rev F2, Page 20/39

#### **MAGNETIC SCALE SELECTION**

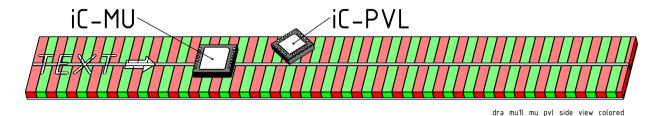

Figure 9: Positioning of iC-PVL on a linear scale (iC-MU nonius type)

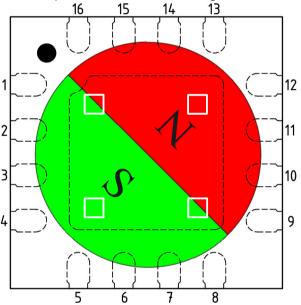

iC-PVL is able to scan magnetic pole wheels or linear scales with a pole width of 1 mm to 5 mm. This corresponds to a magnetic period (N-S sequence) of 2 to 10 mm. Due to the diagonal sensor array, iC-PVL is rotated 45° in relation to the magnetic code (see Figures 9, 10, 11).

With the recommended differential scanning mode (POLEWID = 0x00), the measurement is highly tolerant to external common mode magnetic stray fields. The ideal pole width in this operating mode is 1.5 mm, but the device is functional with a pole width range of about 1 to 3 mm. This enables iC-PVL to use the same magnetic scale as a linear or off-axis singleturn sensor (e.g. iC-MU (1.28 mm), iC-MU150 (1.5 mm), iC-MHL200 (2 mm)).

| POLEWID | Addr      | . 0x04; bit 1: | 0                      |

|---------|-----------|----------------|------------------------|

| Code    | Pole size | Ideal size     | Scanning               |

| 0x00    | 1-3 mm    | 1.5 mm         | Off-axis, differential |

| 0x01    | 4-5 mm    | 4.5 mm         | Off-axis, single-ended |

| 0x02    | 2-4 mm    | 3.0 mm         | Off-axis, single-ended |

| 0x03    | 1-3 mm    | 1.5 mm         | Off-axis, single-ended |

Table 10: Pole size of magnetic scale

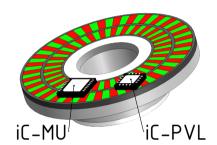

Figure 10: Positioning of iC-PVL on a pole wheel (iC-MU nonius type)

Figure 11: Positioning of iC-PVL on a pole wheel (iC-MU nonius type).

Together with the iC-MU off-axis nonius encoder, a magnetic multiturn encoder can be realized (see iC-PVL AN2) The iC-PVL Hall sensor array is placed over the center line of a magnetic track, e.g. at a radius of 13.375 mm to scan the master track of the MU18S 30-32N magnetic target (see Figure 11). In this case, the corresponding PCR value for 32 magnetic periods (PCR = 0x1F) has to be applied (see Table 11).

In these applications, a certain number of magnetic periods (i.e., north-south pole pairs) may be interpreted as one mechanical revolution. The FlexCount® logic offers this functionality. By electrically emulating the characteristics of a gear box, the gear transmission is freely programmable. 1 to 256 pole pairs can be interpreted as one mechanical revolution. The configuration parameter PCR, period counts per (mechanical) revolution, is used as defined in Table 11.

Rev F2, Page 21/39

| PCR  | Addr. 0x02; bit 7:0          |

|------|------------------------------|

| Code | Period counts per revolution |

| 0x00 | 1                            |

| 0x01 | 2                            |

| 0x02 | 3                            |

|      | Code + 1                     |

| 0xFE | 255                          |

| 0xFF | 256                          |

Table 11: Period counts per (mechanical) revolution

By way of example, assume a magnetic code disc with 32 periods. iC-PVL will make a multiturn count every 32 periods. The synchronization bits are distributed evenly over these 32 periods, i.e. the disc is divided in eight sectors. Therefore, one sector consists of 8 periods. While reading the position information, it looks like the iC-PVL would be placed above a normal diametrically polarized magnet. This scheme is also valid for non-binary, decimal or odd counts per revolution.

| PCR_OUT | Addr. 0x05; bit 6                                             |  |  |

|---------|---------------------------------------------------------------|--|--|

| Code    | Mode                                                          |  |  |

| 0       | No output of PCR in serial data stream                        |  |  |