# RENESAS

## DATASHEET

## ISL12022M

Low Power RTC with Battery Backed SRAM, Integrated ±5ppm Temperature Compensation and Auto Daylight Saving

FN6668 Rev.10.00 Oct 24, 2019

The ISL12022M device is a low power Real Time Clock (RTC) with an embedded temperature sensor and crystal. Device functions include oscillator compensation, clock/calendar, power fail and low battery monitors, brownout indicator, one-time, periodic or polled alarms, intelligent battery backup switching, Battery Reseal<sup>TM</sup> function, and 128 bytes of battery-backed user SRAM. Backup battery current draw is less than 1.6µA over the temperature range. The device is offered in a 20 Ld SOIC module that contains the RTC and an embedded 32.768kHz quartz crystal. The calibrated oscillator provides less than ±5ppm drift across the full -40°C to +85°C temperature range.

The RTC tracks time with separate registers for hours, minutes, and seconds. The calendar registers track date, month, year, and day of the week and are accurate through 2099, with automatic leap year correction.

Daylight Savings time adjustment is done automatically, using parameters entered by the user. Power fail and battery monitors offer user-selectable trip levels. The time stamp function records the time and date of switchover from V<sub>DD</sub> to V<sub>BAT</sub> power, and also from V<sub>BAT</sub> to V<sub>DD</sub> power.

## **Related Literature**

For a full list of related documents, visit our website:

ISL12022M device page

### **Features**

- Embedded 32.768kHz quartz crystal in the package

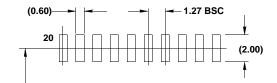

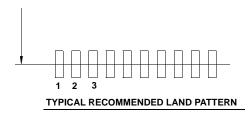

- 20 Ld SOIC package (for DFN version, see the ISL12020M)

- Calendar

- On-chip oscillator temperature compensation

- 10-bit digital temperature sensor output

- 15 selectable frequency outputs

- · Interrupt for alarm or 15 selectable frequency outputs

- · Automatic backup to battery or supercapacitor

- V<sub>DD</sub> and battery status monitors

- · Battery Reseal function to extend battery shelf life

- · Power status brownout monitor

- Time stamp for battery switchover

- 128 bytes battery-backed user SRAM

- 1.6µA maximum battery current

- I<sup>2</sup>C Bus

- RoHS compliant

### Applications

- · Utility meters

- POS equipment

- · Printers and copiers

- Digital cameras

## **Table of Contents**

| Block Diagram                                                              | . 4 |

|----------------------------------------------------------------------------|-----|

| Pin Configuration                                                          | . 4 |

| Pin Descriptions                                                           |     |

| Ordering Information                                                       | . 5 |

| Absolute Maximum Ratings                                                   | . 6 |

| Thermal Information                                                        | . 6 |

| DC Operating Characteristics RTC                                           | . 6 |

| Power-Down Timing                                                          | . 7 |

| I <sup>2</sup> C Interface Specifications                                  | 7   |

| SDA vs SCL Timing                                                          | . 9 |

| Symbol Table                                                               | . 9 |

| Typical Performance Curves                                                 | 10  |

| General Description                                                        | 11  |

| Functional Description                                                     | 12  |

| Power Control Operation                                                    |     |

| Normal Mode (V <sub>DD</sub> ) to Battery Backup Mode (V <sub>BAT</sub> )  |     |

| Battery Backup Mode (V <sub>BAT</sub> ) to Normal Mode (V <sub>DD</sub> ). |     |

| Power Failure Detection                                                    |     |

| Brownout Detection                                                         |     |

| Battery Level Monitor                                                      |     |

| Real Time Clock Operation                                                  |     |

| Single Event and Interrupt                                                 |     |

| Frequency Output Mode                                                      |     |

| General Purpose User SRAM.                                                 |     |

| I <sup>2</sup> C Serial Interface                                          |     |

| Oscillator Compensation                                                    |     |

| Register Descriptions                                                      |     |

| Real Time Clock Registers                                                  |     |

| Addresses [00h to 06h]                                                     |     |

| Control and Status Registers (CSR)                                         |     |

| Addresses [07h to 0Fh]                                                     |     |

| Interrupt Control Register (INT).                                          |     |

| Power Supply Control Register (PWR_VDD)                                    |     |

| Battery Voltage Trip Voltage Register (PWR_VBAT)                           |     |

| Initial AT and DT Setting Register (ITRO)                                  |     |

| BETA Register (BETA)                                                       |     |

| Final Analog Trimming Register (FATR).                                     |     |

| Final Digital Trimming Register (FDTR).                                    |     |

| ALARM Registers (10h to 15h).                                              |     |

| Time Stamp VDD to Battery Registers (TSV2B)                                |     |

| Time Stamp Battery to VDD Registers (TSB2V)                                |     |

| DST Control Registers (DSTCR).                                             |     |

| TEMP Registers (TEMP)                                                      |     |

| NPPM Registers (NPPM)                                                      | .23 |

| XTO Registers (XTO)                                       | 24 |

|-----------------------------------------------------------|----|

| ALPHA Hot Register (ALPHAH)                               | 24 |

| User Registers (Accessed by Using Slave Address 1010111x) | 25 |

| Addresses [00h to 7Fh]                                    | 25 |

| <sup>2</sup> C Serial Interface                           | 25 |

| Protocol Conventions                                      |    |

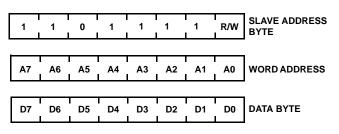

| Device Addressing                                         | 26 |

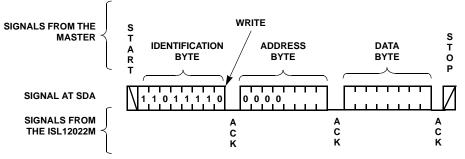

| Write Operation                                           | 26 |

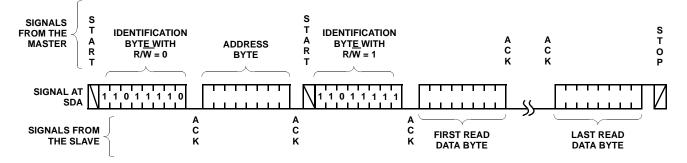

| Read Operation                                            | 26 |

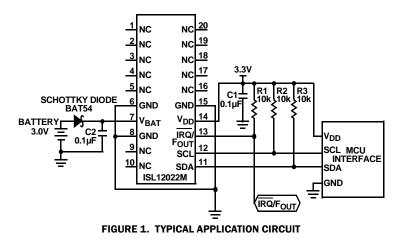

| Application Section                                       | 27 |

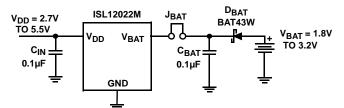

| Power Supply Considerations                               | 27 |

| Battery Backup Details                                    |    |

| Layout Considerations                                     |    |

| Measuring Oscillator Accuracy                             |    |

| Temperature Compensation Operation                        |    |

| Daylight Savings Time (DST) Example                       | 28 |

| Revision History                                          | 29 |

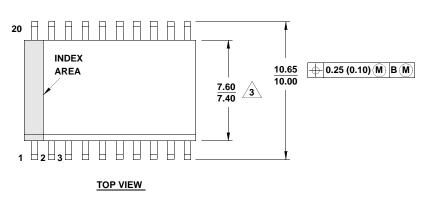

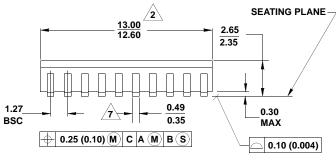

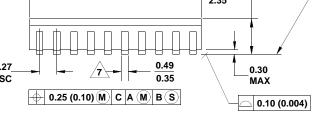

| Package Outline Drawing                                   | 32 |

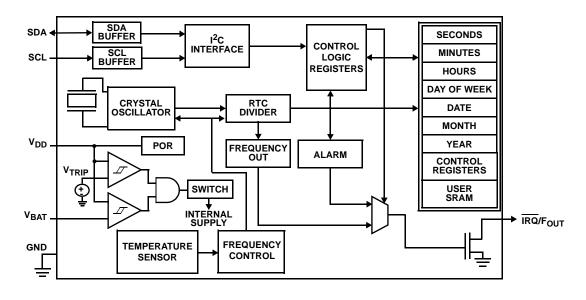

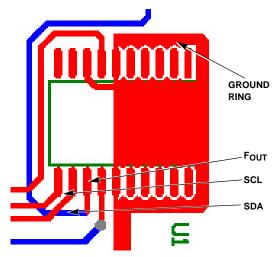

## **Block Diagram**

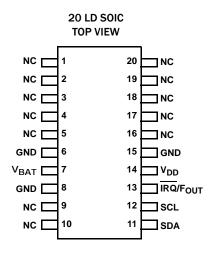

## **Pin Configuration**

## **Pin Descriptions**

| PIN NUMBER                                     | SYMBOL           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4, 5, 9,<br>10, 16, 17, 18,<br>19, 20 | NC               | No Connection. Do not connect to a signal or supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7                                              | V <sub>BAT</sub> | <b>Backup Supply</b> . This input provides a backup supply voltage to the device. V <sub>BAT</sub> supplies power to the device in the event that the V <sub>DD</sub> supply fails. This pin can be connected to a battery, a supercapacitor or tied to ground if not used. See the Battery Monitor parameter in <u>"DC Operating Characteristics RTC" on page 6</u> . This pin should be tied to ground if not used.                                                                                                                                                                                     |

| 11                                             | SDA              | <b>Serial Data</b> . SDA is a bi-directional pin used to transfer data into and out of the device. It has an open drain output and may be OR'ed with other open drain or open collector outputs. The input buffer is always active (not gated) in normal mode.<br>An open drain output requires the use of a pull-up resistor. The output circuitry controls the fall time of the output signal with the use of a slope controlled pull-down. The circuit is designed for 400kHz I <sup>2</sup> C interface speeds. It is disabled when the backup power supply on the V <sub>BAT</sub> pin is activated. |

### Pin Descriptions (Continued)

| PIN NUMBER | SYMBOL               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12         | SCL                  | <b>Serial Clock</b> . The SCL input is used to clock all serial data into and out of the device. The input buffer on this pin is always active (not gated). It is disabled when the backup power supply on the V <sub>BAT</sub> pin is activated to minimize power consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13         | ĪRQ/F <sub>OUT</sub> | <b>Interrupt Output/Frequency Output</b> (Default 32.768kHz frequency output). This dual function pin can be used as an interrupt or frequency output pin. The IRQ/FOUT mode is selected via the frequency out control bits of the control/status register. <b>Interrupt Mode</b> . The pin provides an interrupt signal output. This signal notifies a host processor that an alarm has occurred and requests action. It is an open drain active low output. <b>Frequency Output Mode</b> . The pin outputs a clock signal, which is related to the crystal frequency. The frequency output is user selectable and enabled via the I <sup>2</sup> C bus. It is an open drain output. The output is open drain and requires a pull-up resistor. |

| 14         | V <sub>DD</sub>      | <b>Power Supply</b> . Chip power supply and ground pins. The device will operate with a power supply from $V_{DD}$ = 2.7V to 5.5VDC. A 0.1µF capacitor is recommended on the $V_{DD}$ pin to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6, 8, 15   | GND                  | Ground Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3) | PART<br>MARKING | V <sub>DD</sub> RANGE<br>(V) | TEMP RANGE<br>(°C) | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | PACKAGE<br>(RoHS COMPLIANT) | PKG.<br>DWG. # |

|-----------------------------|-----------------|------------------------------|--------------------|--------------------------------------------|-----------------------------|----------------|

| ISL12022MIBZ                | ISL12022MIBZ    | 2.7 to 5.5                   | -40 to +85         | -                                          | 20 Ld SOIC                  | M20.3          |

| ISL12022MIBZ-T              | ISL12022MIBZ    | 2.7 to 5.5                   | -40 to +85         | 1k                                         | 20 Ld SOIC                  | M20.3          |

NOTES:

1. See TB347 for details about reel specifications.

2. These plastic packaged products employ special material sets, molding compounds and 100% matter tin plate plus anneal (e3) termination finish. These products do contain Pb but they are RoHS compliant by exemption 7 (lead in high melt temp solder for internal connections) and exemption 5 (lead in piezoelectric elements). These RoHS compliant products are compatible with both SnPb and Pb-free soldering operations. These RoHS compliant products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

3. For Moisture Sensitivity Level (MSL), see the ISL12022M device page. For more information about MSL, see TB363.

#### **Absolute Maximum Ratings**

| Voltage on V <sub>DD</sub> | , V <sub>BAT</sub> and IRQ | /F <sub>OUT</sub> pins |

|----------------------------|----------------------------|------------------------|

|----------------------------|----------------------------|------------------------|

| (Respect to Ground)                                       |

|-----------------------------------------------------------|

| Voltage on SCL and SDA pins                               |

| (Respect to Ground)                                       |

| ESD Rating                                                |

| Human Body Model (Per MIL-STD-883 Method 3014)>3kV        |

| Machine Model>300V                                        |

| Charged Device Model>2200V                                |

| Latch-up (Tested per JESD-78B, Class 2, Level A 100mA     |

| Shock Resistance                                          |

| Vibration (Ultrasound Cleaning Not Advised) 20g/10-2000Hz |

#### **Thermal Information**

| Thermal Resistance (Typical)               | θ <sub>JA</sub> (°C∕W) | θ <sub>JC</sub> (°C/W) |

|--------------------------------------------|------------------------|------------------------|

| 20 Lead SOIC ( <u>Notes 4</u> , <u>5</u> ) | 70                     | 35                     |

| Storage Temperature                        |                        | 40°C to +85°C          |

| Pb-Free Reflow Profile ( <u>Note 6</u> )   |                        | see <u>TB493</u>       |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- 4.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See <u>TB379</u> for details.

- 5. For  $\theta_{JC}$ , the case temperature location is on top of the package and measured in the center of the package between pins 6 and 15.

- 6. The ISL12022M Oscillator Initial Accuracy can change after solder reflow attachment. The amount of change will depend on the reflow temperature and length of exposure. A general rule is to use only one reflow cycle and keep the temperature and time as short as possible. Changes on the order of ±1ppm to ±3ppm can be expected with typical reflow profiles.

**DC Operating Characteristics RTC** Test Conditions:  $V_{DD} = +2.7$  to +5.5V,  $T_A = -40$  °C to +85 °C, unless otherwise stated. Boldface limits apply over the operating temperature range, -40 °C to +85 °C.

| SYMBOL               | PARAMETER                                                                                                       | CONDITIONS                                       | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS | NOTES         |

|----------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|---------------|

| V <sub>DD</sub>      | Main Power Supply                                                                                               | ( <u>Note 15</u> )                               | 2.7                      |                          | 5.5                      | v     |               |

| V <sub>BAT</sub>     | Battery Supply Voltage                                                                                          | ( <u>Note 15</u> )                               | 1.8                      |                          | 5.5                      | v     | 9             |

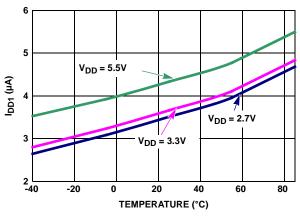

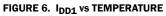

| I <sub>DD1</sub>     | Supply Current. (I <sup>2</sup> C Not Active,                                                                   | V <sub>DD</sub> = 5V                             |                          | 4.1                      | 15                       | μΑ    | <u>10, 11</u> |

|                      | Temperature Conversion Not Active, F <sub>OUT</sub><br>Not Active)                                              | V <sub>DD</sub> = 3V                             |                          | 3.5                      | 14                       | μΑ    | <u>10, 11</u> |

| I <sub>DD2</sub>     | Supply Current. (I <sup>2</sup> C Active, Temperature<br>Conversion Not Active, F <sub>out</sub> Not Active)    | V <sub>DD</sub> = 5V                             |                          | 200                      | 500                      | μA    | <u>10, 11</u> |

| I <sub>DD3</sub>     | Supply Current. (I <sup>2</sup> C Not Active,<br>Temperature Conversion Active, F <sub>OUT</sub> Not<br>Active) | V <sub>DD</sub> = 5V                             |                          | 120                      | 400                      | μΑ    | <u>10, 11</u> |

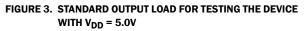

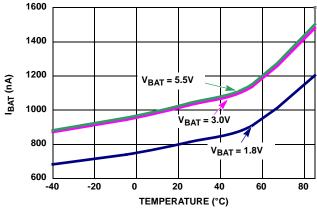

| IBAT                 | Battery Supply Current                                                                                          | $V_{DD} = 0V, V_{BAT} = 3V, T_A = +25 ^{\circ}C$ |                          | 1.0                      | 1.6                      | μΑ    | <u>10</u>     |

|                      |                                                                                                                 | $V_{DD} = 0V, V_{BAT} = 3V$                      |                          | 1.0                      | 5.0                      | μΑ    | <u>10</u>     |

| IBATLKG              | Battery Input Leakage                                                                                           | V <sub>DD</sub> = 5.5V, V <sub>BAT</sub> = 1.8V  |                          |                          | 100                      | nA    |               |

| ILI                  | Input Leakage Current on SCL                                                                                    | $V_{IL} = OV, V_{IH} = V_{DD}$                   | -1.0                     | ±0.1                     | 1.0                      | μΑ    |               |

| ILO                  | I/O Leakage Current on SDA                                                                                      | $V_{IL} = OV, V_{IH} = V_{DD}$                   | -1.0                     | ±0.1                     | 1.0                      | μΑ    |               |

| V <sub>BATM</sub>    | Battery Level Monitor Threshold                                                                                 |                                                  | -100                     |                          | +100                     | mV    |               |

| V <sub>PBM</sub>     | Brownout Level Monitor Threshold                                                                                |                                                  | -100                     |                          | +100                     | mV    |               |

| V <sub>TRIP</sub>    | V <sub>BAT</sub> Mode Threshold                                                                                 | ( <u>Note 15</u> )                               | 2.0                      | 2.2                      | 2.4                      | v     |               |

| V <sub>TRIPHYS</sub> | V <sub>TRIP</sub> Hysteresis                                                                                    |                                                  |                          | 30                       |                          | mV    | <u>13</u>     |

| VBATHYS              | V <sub>BAT</sub> Hysteresis                                                                                     |                                                  |                          | 50                       |                          | mV    | <u>13</u>     |

**DC Operating Characteristics RTC** Test Conditions:  $V_{DD}$  = +2.7 to +5.5V,  $T_A$  = -40 °C to +85 °C, unless otherwise stated. Boldface limits apply over the operating temperature range, -40 °C to +85 °C. (Continued)

| SYMBOL                              | PARAMETER                              | CONDITIONS                                    | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS | NOTES                |

|-------------------------------------|----------------------------------------|-----------------------------------------------|--------------------------|--------------------------|--------------------------|-------|----------------------|

| OSCILLATO                           | RACCURACY                              |                                               | 1                        |                          |                          |       |                      |

| $\Delta \mathbf{Fout}_{\mathbf{I}}$ | Oscillator Initial Accuracy            | V <sub>DD</sub> = 3.3V                        | -2                       |                          | +8                       | ppm   | <u>6</u> , <u>17</u> |

| $\Delta \mathbf{Fout}_{\mathbf{R}}$ | Oscillator Accuracy after Reflow Cycle | V <sub>DD</sub> = 3.3V                        |                          | ±5                       |                          | ppm   | <u>6</u> , <u>17</u> |

| $\Delta \mathbf{Fout}_{\mathbf{T}}$ | Oscillator Stability vs Temperature    | V <sub>DD</sub> = 3.3V                        |                          | ±2                       |                          | ppm   | <u>6</u> , <u>18</u> |

| $\Delta \textbf{Fout}_{\textbf{V}}$ | Oscillator Stability vs Voltage        | $2.7V \le V_{DD} \le 5.5V$                    | -3                       |                          | +3                       | ppm   | <u>19</u>            |

| Temp                                | Temperature Sensor Accuracy            | $V_{DD} = V_{BAT} = 3.3V$                     |                          | ±2                       |                          | °C    | <u>13</u>            |

| IRQ/FOUT                            | OPEN DRAIN OUTPUT)                     | -                                             |                          |                          |                          |       |                      |

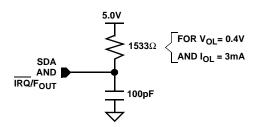

| V <sub>OL</sub>                     | Output Low Voltage                     | $V_{DD} = 5V, I_{OL} = 3mA$                   |                          |                          | 0.4                      | v     |                      |

|                                     |                                        | V <sub>DD</sub> = 2.7V, I <sub>OL</sub> = 1mA |                          |                          | 0.4                      | v     |                      |

**Power-Down Timing** Test Conditions: V<sub>DD</sub> = +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise stated.

| SYMBOL             | PARAMETER                                   | CONDITIONS | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS | NOTES     |

|--------------------|---------------------------------------------|------------|--------------------------|--------------------------|--------------------------|-------|-----------|

| V <sub>DDSR-</sub> | V <sub>DD</sub> Negative Slew Rate          |            |                          |                          | 10                       | V/ms  | <u>12</u> |

| V <sub>DDSR+</sub> | V <sub>DD</sub> Positive Slew Rate, minimum |            |                          | 0.05                     |                          | V/ms  | <u>16</u> |

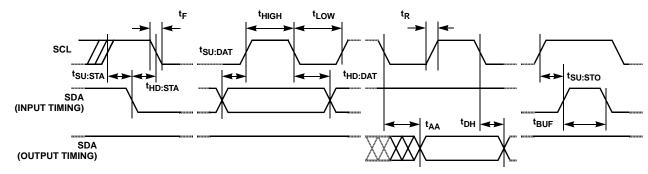

**I<sup>2</sup>C Interface Specifications** Test Conditions: V<sub>DD</sub> = +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| SYMBOL            | PARAMETER                                                           | TEST CONDITIONS                                                                                                             | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS | NOTES                 |

|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|-----------------------|

| V <sub>IL</sub>   | SDA and SCL Input Buffer LOW<br>Voltage                             |                                                                                                                             | -0.3                     |                          | 0.3 x V <sub>DD</sub>    | V     |                       |

| V <sub>IH</sub>   | SDA and SCL Input Buffer HIGH<br>Voltage                            |                                                                                                                             | 0.7 x V <sub>DD</sub>    |                          | V <sub>DD</sub> + 0.3    | v     |                       |

| Hysteresis        | SDA and SCL Input Buffer<br>Hysteresis                              |                                                                                                                             |                          | 0.05 x V <sub>DD</sub>   |                          | v     | <u>13</u> , <u>14</u> |

| V <sub>OL</sub>   | SDA Output Buffer LOW Voltage,<br>Sinking 3mA                       | V <sub>DD</sub> = 5V, I <sub>OL</sub> = 3mA                                                                                 | 0                        | 0.02                     | 0.4                      | v     |                       |

| C <sub>PIN</sub>  | SDA and SCL Pin Capacitance                                         | $T_{A} = +25 \text{ °C, } f = 1 \text{MHz,}$<br>$V_{DD} = 5 \text{V, } V_{IN} = 0 \text{V, } V_{OUT} = 0 \text{V}$          |                          |                          | 10                       | pF    | <u>13,</u> 14         |

| fscl              | SCL Frequency                                                       |                                                                                                                             |                          |                          | 400                      | kHz   |                       |

| t <sub>IN</sub>   | Pulse Width Suppression Time at SDA and SCL Inputs                  | Any pulse narrower than the max spec is suppressed.                                                                         |                          |                          | 50                       | ns    |                       |

| t <sub>AA</sub>   | SCL Falling Edge to SDA Output<br>Data Valid                        | SCL falling edge crossing 30% of $V_{DD}$ , until SDA exits the 30% to 70% of $V_{DD}$ window.                              |                          |                          | 900                      | ns    |                       |

| t <sub>BUF</sub>  | Time the Bus Must be Free Before<br>the Start of a New Transmission | SDA crossing 70% of $V_{DD}$ during a STOP condition, to SDA crossing 70% of $V_{DD}$ during the following START condition. | 1300                     |                          |                          | ns    |                       |

| tLOW              | Clock LOW Time                                                      | Measured at the 30% of $\ensuremath{V_{DD}}$ crossing.                                                                      | 1300                     |                          |                          | ns    |                       |

| <sup>t</sup> HIGH | Clock HIGH Time                                                     | Measured at the 70% of V <sub>DD</sub> crossing.                                                                            | 600                      |                          |                          | ns    |                       |

| SYMBOL              | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                                                                                                                                          | MIN<br>( <u>Note 7</u> ) | TYP<br>( <u>Note 8</u> ) | MAX<br>( <u>Note 7</u> ) | UNITS | NOTES                 |

|---------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|-----------------------|

| <sup>t</sup> su:sta | START Condition Setup Time                   | SCL rising edge to SDA falling<br>edge. Both crossing 70% of<br>V <sub>DD</sub> .                                                                                                                                                                                                                        | 600                      |                          |                          | ns    |                       |

| <sup>t</sup> hd:sta | START Condition Hold Time                    | From SDA falling edge<br>crossing 30% of V <sub>DD</sub> to SCL<br>falling edge crossing 70% of<br>V <sub>DD</sub> .                                                                                                                                                                                     | 600                      |                          |                          | ns    |                       |

| <sup>t</sup> su:dat | Input Data Setup Time                        | From SDA exiting the 30% to 70% of $V_{DD}$ window, to SCL rising edge crossing 30% of $V_{DD}$ .                                                                                                                                                                                                        | 100                      |                          |                          | ns    |                       |

| <sup>t</sup> HD:DAT | Input Data Hold Time                         | From SCL falling edge<br>crossing 30% of V <sub>DD</sub> to SDA<br>entering the 30% to 70% of<br>V <sub>DD</sub> window.                                                                                                                                                                                 | 20                       |                          | 900                      | ns    |                       |

| <sup>t</sup> su:sto | STOP Condition Setup Time                    | From SCL rising edge<br>crossing 70% of V <sub>DD</sub> , to SDA<br>rising edge crossing 30% of<br>V <sub>DD</sub> .                                                                                                                                                                                     | 600                      |                          |                          | ns    |                       |

| <sup>t</sup> hd:sto | STOP Condition Hold Time                     | From SDA rising edge to SCL falling edge. Both crossing 70% of V <sub>DD</sub> .                                                                                                                                                                                                                         | 600                      |                          |                          | ns    |                       |

| <sup>t</sup> DH     | Output Data Hold Time                        | From SCL falling edge<br>crossing 30% of V <sub>DD</sub> , until<br>SDA enters the 30% to 70%<br>of V <sub>DD</sub> window.                                                                                                                                                                              | 0                        |                          |                          | ns    |                       |

| t <sub>R</sub>      | SDA and SCL Rise Time                        | From 30% to 70% of V <sub>DD.</sub>                                                                                                                                                                                                                                                                      | 20 + 0.1 x Cb            |                          | 300                      | ns    | <u>13</u> , <u>14</u> |

| t <sub>F</sub>      | SDA and SCL Fall Time                        | From 70% to 30% of V <sub>DD.</sub>                                                                                                                                                                                                                                                                      | 20 + 0.1 x Cb            |                          | 300                      | ns    | <u>13</u> , <u>14</u> |

| Cb                  | Capacitive Loading of SDA or SCL             | Total on-chip and off-chip                                                                                                                                                                                                                                                                               | 10                       |                          | 400                      | pF    | <u>13, 14</u>         |

| R <sub>PU</sub>     | SDA and SCL Bus Pull-up Resistor<br>Off-chip | $\label{eq:maximum} \begin{array}{l} \mbox{Maximum is determined by} \\ t_R \mbox{ and } t_F. \\ \mbox{For } Cb = 400 \mbox{pF}, \mbox{max is about} \\ 2k\Omega \sim 2.5 \mbox{k}\Omega. \\ \mbox{For } Cb = 40 \mbox{pF}, \mbox{max is about} \\ 15 \mbox{k}\Omega \sim 20 \mbox{k}\Omega \end{array}$ | 1                        |                          |                          | kΩ    | <u>13, 14</u>         |

**I<sup>2</sup>C Interface Specifications** Test Conditions: V<sub>DD</sub> = +2.7 to +5.5V, Temperature = -40 °C to +85 °C, unless otherwise specified. Boldface limits apply over the operating temperature range, -40 °C to +85 °C. (Continued)

NOTES:

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 8. Specified at +25°C.

- 9. Temperature Conversion is inactive below  $V_{BAT}$  = 2.7V. Device operation is not guaranteed at  $V_{BAT}$  <1.8V.

- 10. IRQ/FOUT inactive.

- 11.  $V_{DD} > V_{BAT} + V_{BATHYS}$

- 12. In order to ensure proper timekeeping, the  $V_{\mbox{DD}\mbox{SR-}}$  specification must be followed.

- 13. Limits should be considered typical and are not production tested.

- 14. These are  $I^2C$  specific parameters and are not tested, however, they are used to set conditions for testing devices to validate specification.

- 15. Minimum  $V_{DD}$  and/or  $V_{BAT}$  of 1V to sustain the SRAM. The value is based on characterization and it is not tested.

- 16. To avoid EEPROM recall issues, it is advised to use this minimum power up slew rate. Not tested, shown as typical only.

- 17. Defined as the deviation from a target oscillator frequency of 32,768.0Hz at room temperature.

- 18. Defined as the deviation from the room temperature measured 1Hz frequency,  $V_{DD}$  = 3.3V, at  $T_A$  = -40 °C to +85 °C.

- 19. Defined as the deviation at room temperature from the measured 1Hz frequency (or equivalent) at  $V_{DD}$  = 3.3, over the range of  $V_{DD}$  = 2.7V to  $V_{DD}$  = 5.5V.

## **SDA vs SCL Timing**

## **Symbol Table**

EQUIVALENT AC OUTPUT LOAD CIRCUIT FOR V<sub>DD</sub> = 5V

| WAVEFORM | INPUTS                            | OUTPUTS                            |

|----------|-----------------------------------|------------------------------------|

|          | Must be steady                    | Will be steady                     |

|          | May change<br>from LOW<br>to HIGH | Will change<br>from LOW<br>to HIGH |

|          | May change<br>from HIGH<br>to LOW | Will change<br>from HIGH<br>to LOW |

|          | Don't Care:<br>Changes Allowed    | Changing:<br>State Not Known       |

|          | N/A                               | Center Line is<br>High Impedance   |

|          |                                   |                                    |

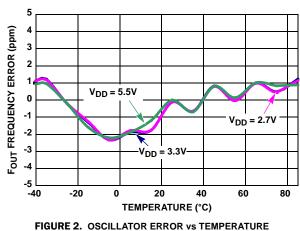

### Typical Performance Curves Temperature is +25°C unless otherwise specified.

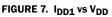

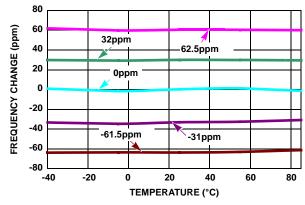

FIGURE 8. OSCILLATOR ERROR vs TEMPERATURE

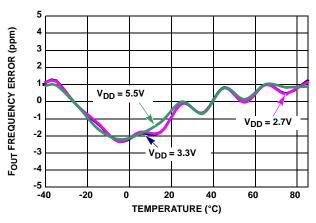

FIGURE 9. FOUT vs IDD

#### Typical Performance Curves Temperature is +25°C unless otherwise specified. (Continued)

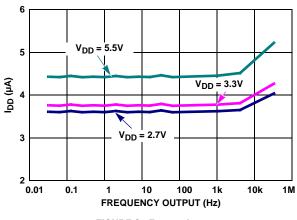

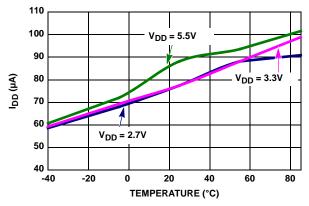

FIGURE 10. IDD vs TEMPERATURE, 3 DIFFERENT FOUT

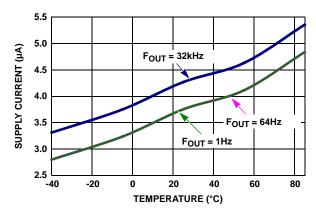

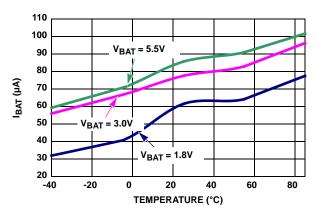

FIGURE 11. IBAT WITH TSE = 1, BTSE = 1 vs TEMPERATURE

FIGURE 12. I<sub>DD</sub> WITH TSE = 1 vs TEMPERATURE

FIGURE 13. OSCILLATOR CHANGE vs TEMPERATURE AT DIFFERENT AGING SETTINGS (IATR) (BETA SET FOR 1ppm STEPS)

## **General Description**

The ISL12022M device is a low power real time clock (RTC) with embedded temperature sensor and crystal. It contains crystal frequency compensation circuitry over the operating temperature range good to ±5ppm accuracy. It also contains a clock/calendar with Daylight Savings Time (DST) adjustment, power fail and low battery monitors, brownout indicator, 1 periodic or polled alarm, intelligent battery backup switching and 128 Bytes of batterybacked user SRAM.

The oscillator uses an internal 32.768kHz crystal. The real time clock tracks time with separate registers for hours, minutes and seconds. The device has calendar registers for date, month, year and day of the week. The calendar is accurate through 2099, with automatic leap year correction. In addition, the ISL12022M can be programmed for automatic Daylight Saving Time (DST) adjustment by entering local DST information.

The ISL12022M's alarm can be set to any clock/calendar value for a match. For example, every minute, every Tuesday or at 5:23 AM on March 21. The alarm status is available by checking the Status Register, or the device can be configured to provide a hardware interrupt via the  $\overline{IRQ}/F_{OUT}$  pin. There is a repeat mode for

the alarm allowing a periodic interrupt every minute, every hour, every day, etc.

The device also offers a backup power input pin. This  $V_{BAT}$  pin allows the device to be backed up by battery or supercapacitor with automatic switchover from  $V_{DD}$  to  $V_{BAT}$ . The ISL12022M device is specified for  $V_{DD}$  = 2.7V to 5.5V and the clock/calendar portion of the device remains fully operational in battery backup mode down to 1.8V (Standby Mode). The  $V_{BAT}$  level is monitored and reported against preselected levels. The first report is registered when the  $V_{BAT}$  level falls below 85% of nominal level; the second level is set for 75%. Battery levels are stored in PWR\_VBAT registers.

The ISL12022M offers a "Brownout" alarm once the V<sub>DD</sub> falls below a pre-selected trip level. This allows system Micro to save vital information to memory before complete power loss. There are six V<sub>DD</sub> levels that could be selected for initiation of the Brownout alarm.

## **Functional Description**

#### **Power Control Operation**

The power control circuit accepts a V<sub>DD</sub> and a V<sub>BAT</sub> input. Many types of batteries can be used with Renesas RTC products. For example, 3.0V or 3.6V Lithium batteries are appropriate, and battery sizes are available that can power the ISL12022M for up to 10 years. Another option is to use a supercapacitor for applications where V<sub>DD</sub> is interrupted for up to a month. See the <u>"Application Section" on page 27</u> for more information.

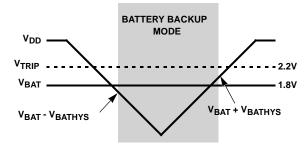

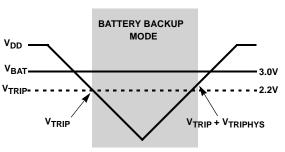

# Normal Mode (V<sub>DD</sub>) to Battery Backup Mode (V<sub>BAT</sub>)

To transition from the  $V_{\mbox{DD}}$  to  $V_{\mbox{BAT}}$  mode,  $\underline{both}$  of the following conditions must be met:

#### **Condition 1:**

V<sub>DD</sub> < V<sub>BAT</sub> - V<sub>BATHYS</sub> where V<sub>BATHYS</sub> ≈ 50mV

#### **Condition 2:**

$\label{eq:VDD} \begin{array}{l} v_{DD} < v_{TRIP} \\ \text{where } v_{TRIP} \approx 2.2 V \end{array}$

# Battery Backup Mode (V<sub>BAT</sub>) to Normal Mode (V<sub>DD</sub>)

The ISL12022M device will switch from the  $\rm V_{BAT}$  to  $\rm V_{DD}$  mode when one of the following conditions occurs:

#### **Condition 1:**

$\label{eq:VDD} \begin{array}{l} \mathsf{V}_{DD} > \mathsf{V}_{BAT} + \mathsf{V}_{BATHYS} \\ \text{where } \mathsf{V}_{BATHYS} \approx 50 m \mathsf{V} \end{array}$

#### **Condition 2:**

$$\label{eq:VDD} \begin{split} V_{DD} &> V_{TRIP} + V_{TRIPHYS} \\ where & V_{TRIPHYS} \approx 30mV \end{split}$$

These power control situations are illustrated in  $\underline{Figures 14}$  and  $\underline{15}.$

The I<sup>2</sup>C bus is deactivated in battery backup mode to reduce power consumption. Aside from this, all RTC functions are operational during battery backup mode. Except for SCL and SDA, all the inputs and outputs of the ISL12022M are active during battery backup mode unless disabled via the control register.

FIGURE 15. BATTERY SWITCHOVER WHEN VBAT > VTRIP

The device Time Stamps the switchover from V<sub>DD</sub> to V<sub>BAT</sub> and V<sub>BAT</sub> to V<sub>DD</sub>, and the time is stored in t<sub>SV2B</sub> and t<sub>SB2V</sub> registers respectively. If multiple V<sub>DD</sub> power-down sequences occur before the status is read, the earliest V<sub>DD</sub> to V<sub>BAT</sub> power-down time is stored and the most recent V<sub>BAT</sub> to V<sub>DD</sub> time is stored.

Temperature conversion and compensation can be enabled in battery backup mode. Bit BTSE in the BETA register controls this operation, as described in <u>"BETA Register (BETA)" on page 19</u>.

#### **Power Failure Detection**

The ISL12022M provides a Real Time Clock Failure Bit (RTCF) to detect total power failure. It allows users to determine if the device has powered up after having lost all power to the device (both  $V_{DD}$  and  $V_{BAT}$ ).

#### **Brownout Detection**

The ISL12022M monitors the V<sub>DD</sub> level continuously and provides warning if the V<sub>DD</sub> level drops below prescribed levels. There are six (6) levels that can be selected for the trip level. These values are 85% below popular V<sub>DD</sub> levels. The LVDD bit in the Status Register will be set to "1" when brownout is detected. Note that the I<sup>2</sup>C serial bus remains active unless the Battery V<sub>TRIP</sub> levels are reached.

#### **Battery Level Monitor**

The ISL12022M has a built-in warning feature once the backup battery level drops first to 85% and then to 75% of the battery's nominal V<sub>BAT</sub> level. When the battery voltage drops to between 85% and 75%, the LBAT85 bit is set in the status register. When the level drops below 75%, both LBAT85 and LBAT75 bits are set in the status register.

The battery level monitor is not functional in battery backup mode. In order to read the monitor bits after powering up  $V_{DD}$ , instigate a battery level measurement by setting the TSE bit to "1" (BETA register), and then read the bits.

There is a Battery Time Stamp Function available. Once the  $V_{DD}$  is low enough to enable switchover to the battery, the RTC time/date are written into the TSV2B register. This information can be read from the TSV2B registers to discover the point in time of the  $V_{DD}$ power-down. If there are multiple power-down cycles before reading these registers, the first values stored in these registers will be retained. These registers will hold the original power-down value until they are cleared by setting CLRTS = 1 to clear the registers.

The normal power switching of the ISL12022M is designed to switch into battery backup mode only if the  $V_{DD}$  power is lost.

This will ensure that the device can accept a wide range of backup voltages from many types of sources while reliably switching into backup mode.

Note that the ISL12022M is not guaranteed to operate with  $V_{BAT} < 1.8V$ . If the battery voltage is expected to drop lower than this minimum, correct operation of the device, (especially after a  $V_{DD}$  power-down cycle) is not guaranteed.

The minimum  $V_{BAT}$  to insure SRAM is stable is 1.0V. Below that, the SRAM may be corrupted when  $V_{DD}$  power resumes.

## **Real Time Clock Operation**

The Real Time Clock (RTC) uses an integrated 32.768kHz quartz crystal to maintain an accurate internal representation of second, minute, hour, day of week, date, month, and year. The RTC also has leap-year correction. The clock also corrects for months having fewer than 31 days and has a bit that controls 24-hour or AM/PM format. When the ISL12022M powers up after the loss of both  $V_{DD}$  and  $V_{BAT}$ , the clock will not begin incrementing until at least one byte is written to the clock register.

#### **Single Event and Interrupt**

The alarm mode is enabled via the MSB bit. Choosing single event or interrupt alarm mode is selected via the IM bit. Note that when the frequency output function is enabled, the alarm function is disabled.

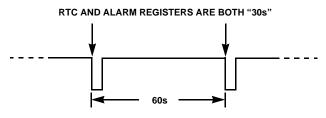

The standard alarm allows for alarms of time, date, day of the week, month, and year. When a time alarm occurs in single event mode, the  $\overline{IRQ}/F_{OUT}$  pin will be pulled low and the alarm status bit (ALM) will be set to "1".

The pulsed interrupt mode allows for repetitive or recurring alarm functionality. Hence, once the alarm is set, the device will continue to alarm for each occurring match of the alarm and present time. Thus, it will alarm as often as every minute (if only the nth second is set) or as infrequently as once a year (if at least the nth month is set). During pulsed interrupt mode, the  $\overline{IRQ}/F_{OUT}$  pin will be pulled low for 250ms and the alarm status bit (ALM) will be set to "1".

The ALM bit can be reset by the user or cleared automatically using the auto reset mode (see ARST bit). The alarm function can be enabled/disabled during battery backup mode using the FOBATB bit. For more information on the alarm, please see <u>"ALARM Registers (10h to 15h)" on page 21</u>.

#### **Frequency Output Mode**

The ISL12022M has the option to provide a clock output signal using the  $\overline{IRQ}/F_{OUT}$  open drain output pin. The frequency output mode is set by using the FO bits to select 15 possible output frequency values from 1/32Hz to 32kHz. The frequency output can be enabled/disabled during Battery Backup mode using the FOBATB bit.

#### **General Purpose User SRAM**

The ISL12022M provides 128 bytes of user SRAM. The SRAM will continue to operate in battery backup mode. However, it should be noted that the  $I^2C$  bus is disabled in battery backup mode.

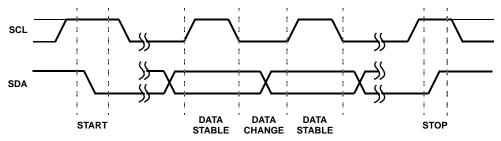

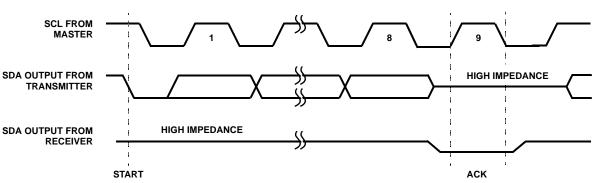

### I<sup>2</sup>C Serial Interface

The ISL12022M has an I<sup>2</sup>C serial bus interface that provides access to the control and status registers and the user SRAM. The I<sup>2</sup>C serial interface is compatible with other industry I<sup>2</sup>C serial bus protocols using a bi-directional data signal (SDA) and a clock signal (SCL).

#### **Oscillator Compensation**

The ISL12022M provides both initial timing correction and temperature correction due to variation of the crystal oscillator. Analog and digital trimming control is provided for initial adjustment, and a temperature compensation function is provided to automatically correct for temperature drift of the crystal. Initial values for the initial AT and DT settings (ITRO), temperature coefficient (ALPHA), crystal capacitance (BETA), as well as the crystal turn-over temperature (XTO), are preset internally and recalled to RAM registers on power-up. The compensation function can be enabled/disabled at any time and can be used in battery mode as well.

## **Register Descriptions**

The battery-backed registers are accessible following a slave byte of "1101111x" and reads or writes to addresses [00h:2Fh]. The defined addresses and default values are described in Table <u>1</u>. The battery backed general purpose SRAM has a different slave address (1010111x), so it is not possible to read/write that section of memory while accessing the registers.

#### **REGISTER ACCESS**

The contents of the registers can be modified by performing a byte or a page write operation directly to any register address.

The registers are divided into 8 sections. They are:

- 1. Real Time Clock (7 bytes): Address 00h to 06h.

- 2. Control and Status (9 bytes): Address 07h to 0Fh.

- 3. Alarm (6 bytes): Address 10h to 15h.

- 4. Time Stamp for Battery Status (5 bytes): Address 16h to 1Ah.

- 5. Time Stamp for V<sub>DD</sub> Status (5 bytes): Address 1Bh to 1Fh.

- 6. Day Light Saving Time (8 bytes): 20h to 27h.

- 7. TEMP (2 bytes): 28h to 29h.

- 8. Crystal Net PPM Correction, NPPM (2 bytes): 2Ah, 2Bh

- 9. Crystal Turnover Temperature, XTO (1 byte): 2Ch

- 10. Crystal ALPHA at high temperature, ALPHA\_H (1 byte): 2Dh

- 11. Scratch Pad (2 bytes): Address 2Eh and 2Fh

Write capability is allowable into the RTC registers (00h to 06h) only when the WRTC bit (bit 6 of address 08h) is set to "1". A multi-byte read or write operation should be limited to one section per operation for best RTC time keeping performance.

A register can be read by performing a random read at any address at any time. This returns the contents of that register location. Additional registers are read by performing a sequential read. For the RTC and Alarm registers, the read instruction latches all clock registers into a buffer, so an update of the clock does not change the time being read. At the end of a read, the master supplies a stop condition to end the operation and free

FN6668 Rev.10.00 Oct 24, 2019

SECTION

ADDR.

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

ALARM

TSV2B

TSB2V

the bus. After a read, the address remains at the previous address +1 so the user can execute a current address read and continue reading the next register. When the previous address is 2Fh, the next address will wrap around to 00h.

7

6

BTSE

0

0

SCA022

MNA022

D

D

D

D

VSC22

BTSR

FFATR5

0

SCA021

MNA021

HRA021

DTA021

D

D

VSC21

5

REG

NAME

BETA

FATR

FDTR

SCA0

**MNAO**

HRA0

DTA0

MOA0

DWA0

VSC

TSE

0

0

ESCA0

EMNA0

EHRA0

EDTA0

EMOA00

EDWA0

0

It is not necessary to set the WRTC bit prior to writing into the control and status, alarm, and user SRAM registers.

1

0

RANGE DEFAULT

N/A

N/A

N/A

00 to 59

00 to 59

0 to 23

01 to 31

01 to 12

0 to 6

0 to 59

00h

00h

00h

01h

01h

00h

00h

01h

01h 00h

00h

XXh

XXh

XXh

00h

| RTC | SC       | 0      | SC22    | SC21    | SC20    | SC13    | SC12                  | SC11                  | SC10                  | 0 to 59 |

|-----|----------|--------|---------|---------|---------|---------|-----------------------|-----------------------|-----------------------|---------|

|     | MN       | 0      | MN22    | MN21    | MN20    | MN13    | MN12                  | MN11                  | MN10                  | 0 to 59 |

|     | HR       | MIL    | 0       | HR21    | HR20    | HR13    | HR12                  | HR11                  | HR10                  | 0 to 23 |

|     | DT       | 0      | 0       | DT21    | DT20    | DT13    | DT12                  | DT11                  | DT10                  | 1 to 31 |

|     | МО       | 0      | 0       | 0       | M020    | M013    | M012                  | M011                  | M010                  | 1 to 12 |

|     | YR       | YR23   | YR22    | YR21    | YR20    | YR13    | YR12                  | YR11                  | YR10                  | 0 to 99 |

|     | DW       | 0      | 0       | 0       | 0       | 0       | DW2                   | DW1                   | DW0                   | 0 to 6  |

| CSR | SR       | BUSY   | OSCF    | DSTADJ  | ALM     | LVDD    | LBAT85                | LBAT75                | RTCF                  | N/A     |

|     | INT      | ARST   | WRTC    | IM      | FOBATB  | F03     | F02                   | F01                   | F00                   | N/A     |

|     | PWR_VDD  | CLRTS  | D       | D       | D       | D       | V <sub>DD</sub> Trip2 | V <sub>DD</sub> Trip1 | V <sub>DD</sub> Trip0 | N/A     |

|     | PWR_VBAT | D      | RESEALB | VB85Tp2 | VB85Tp1 | VB85Tp0 | VB75Tp2               | VB75Tp1               | VB75Tp0               | N/A     |

|     | ITRO     | IDTR01 | IDTR00  | IATR05  | IATR04  | IATR03  | IATR02                | IATR01                | IATR00                | N/A     |

|     | ALPHA    | D      | ALPHA6  | ALPHA5  | ALPHA4  | ALPHA3  | ALPHA2                | ALPHA1                | ALPHA0                | N/A     |

**BETA4**

FATR4

FDTR4

SCA020

MNA020

HRA020

DTA020

M0A020

D

VSC20

**BETA3**

FATR3

FDTR3

SCA013

MNA013

HRA013

DTA013

MOA013

D

VSC13

BETA2

FATR2

FDTR2

SCA012

MNA012

HRA012

DTA012

MOA012

DWA02

VSC12

BETA1

FATR1

FDTR1

SCA011

MNA011

HRA011

DTA011

MOA011

DWA01

VSC11

**BETAO**

FATR0

FDTR0

SCA010

MNA010

HRA010

DTA010

MOA010

DWA00

VSC10

TABLE 1. REGISTER MEMORY MAP (YELLOW SHADING INDICATES READ-ONLY BITS)

4

BIT

3

2

| VMN | 0    | VMN22 | VMN21 | VMN20 | VMN13 | VMN12 | VMN11 | VMN10 | 0 to 59 |

|-----|------|-------|-------|-------|-------|-------|-------|-------|---------|

| VHR | VMIL | 0     | VHR21 | VHR20 | VHR13 | VHR12 | VHR11 | VHR10 | 0 to 23 |

| VDT | 0    | 0     | VDT21 | VDT20 | VDT13 | VDT12 | VDT11 | VDT10 | 1 to 31 |

| VMO | 0    | 0     | 0     | VM020 | VM013 | VM012 | VMO11 | VMO10 | 1 to 12 |

| BSC | 0    | BSC22 | BSC21 | BSC20 | BSC13 | BSC12 | BSC11 | BSC10 | 0 to 59 |

| BMN | 0    | BMN22 | BMN21 | BMN20 | BMN13 | BMN12 | BMN11 | BMN10 | 0 to 59 |

| BHR | BMIL | 0     | BHR21 | BHR20 | BHR13 | BHR12 | BHR11 | BHR10 | 0 to 23 |

| BDT | 0    | 0     | BDT21 | BDT20 | BDT13 | BDT12 | BDT11 | BDT10 | 1 to 31 |

| BMO | 0    | 0     | 0     | BM020 | BM013 | BM012 | BM011 | BM010 | 1 to 12 |

|     |      |       |       |       |       |       |       |       |         |

|     |      |       |       |       |       |       |       |       |         |

|     |      |       |       |       |       |       |       |       |         |

|       |         |               |       |          |           | 1         | зіт       |           |           |           |          |         |

|-------|---------|---------------|-------|----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|---------|

|       |         | REG<br>N NAME |       |          | 1         | •         |           |           | 1         | 1         |          |         |

| ADDR. | SECTION |               | 7     | 6        | 5         | 4         | 3         | 2         | 1         | 0         | RANGE    | DEFAULT |

| 20h   | DSTCR   | DstMoFd       | DSTE  | D        | D         | DstMoFd20 | DstMoFd13 | DstMoFd12 | DstMoFd11 | DstMoFd10 | 1 to 12  | 00h     |

| 21h   |         | DstDwFd       | D     | DstDwFdE | DstWkFd12 | DstWkFd11 | DstWkFd10 | DstDwFd12 | DstDwFd11 | DstDwFd10 | 0 to 6   | 00h     |

| 22h   |         | DstDtFd       | D     | D        | DstDtFd21 | DstDtFd20 | DstDtFd13 | DstDtFd12 | DstDtFd11 | DstDtFd10 | 1 to 31  | 00h     |

| 23h   |         | DstHrFd       | D     | D        | DstHrFd21 | DstHrFd20 | DstHrFd13 | DstHrFd12 | DstHrFd11 | DstHrFd10 | 0 to 23  | 00h     |

| 24h   |         | DstMoRv       | D     | D        | D         | DstMoRv20 | DstMoRv13 | DstMoR12v | DstMoRv11 | DstMoRv10 | 01 to 12 | 00h     |

| 25h   |         | DstDwRv       | D     | DstDwRvE | DstWkrv12 | DstWkRv11 | DstWkRv10 | DstDwRv12 | DstDwRv11 | DstDwRv10 | 0 to 6   | 00h     |

| 26h   |         | DstDtRv       | D     | D        | DstDtRv21 | DstDtRv20 | DstDtRv13 | DstDtRv12 | DstDtRv11 | DstDtRv10 | 01 to 31 | 00h     |

| 27h   |         | DstHrRv       | D     | D        | DstHrRv21 | DstHrRv20 | DstHrRv13 | DstHrRv12 | DstHrRv11 | DstHrRv10 | 0 to 23  | 00h     |

| 28h   | TEMP    | TKOL          | тк07  | TK06     | TK05      | TK04      | ткоз      | TK02      | TK01      | ткоо      | 00 to FF | 00h     |

| 29h   |         | тком          | 0     | 0        | 0         | 0         | 0         | 0         | TK09      | TK08      | 00 to 03 | 00h     |

| 2Ah   | NPPM    | NPPML         | NPPM7 | NPPM6    | NPPM5     | NPPM4     | NPPM3     | NPPM2     | NPPM1     | NPPM0     | 00 to FF | 00h     |

| 2Bh   |         | NPPMH         | 0     | 0        | 0         | 0         | 0         | NPPM10    | NPPM9     | NPPM8     | 00 to 07 | 00h     |

| 2Ch   | ХТО     | хто           | D     | D        | D         | XT4       | ХТЗ       | XT2       | XT1       | хто       | 00 to FF | XXh     |

| 2Dh   | ALPHAH  | ALPHAH        | D     | ALP_H6   | ALP_H5    | ALP_H4    | ALP_H3    | ALP_H2    | ALP_H1    | ALP_HO    | 00 to 7F | XXh     |

| 2Eh   | GPM     | GPM1          | GPM17 | GPM16    | GPM15     | GPM14     | GPM13     | GPM12     | GPM11     | GPM10     | 00 to FF | 00h     |

| 2Fh   |         | GPM2          | GPM27 | GPM26    | GPM25     | GPM24     | GPM23     | GPM22     | GPM21     | GPM20     | 00 to FF | 00h     |

#### TABLE 1. REGISTER MEMORY MAP (YELLOW SHADING INDICATES READ-ONLY BITS) (Continued)

## **Real Time Clock Registers**

#### Addresses [00h to 06h]

#### RTC REGISTERS (SC, MN, HR, DT, MO, YR, DW)

These registers depict BCD representations of the time. As such, SC (Seconds) and MN (Minutes) range from 0 to 59, HR (Hour) can either be a 12-hour or 24-hour mode, DT (Date) is 1 to 31, MO (Month) is 1 to 12, YR (Year) is 0 to 99, and DW (Day of the Week) is 0 to 6.

The DW register provides a Day of the Week status and uses three bits (DW2 to DW0) to represent the seven days of the week. The counter advances in the cycle 0-1-2-3-4-5-6-0-1-2-... The assignment of a numerical value to a specific day of the

week is arbitrary and may be decided by the system software designer. The default value is defined as "0".

#### 24-HOUR TIME

If the MIL bit of the HR register is "1", the RTC uses a 24-hour format. If the MIL bit is "0", the RTC uses a 12-hour format and HR21 bit functions as an AM/PM indicator with a "1" representing PM. The clock defaults to 12-hour format time with HR21 = "0".

#### LEAP YEARS

Leap years add the day February 29 and are defined as those years that are divisible by 4. Years divisible by 100 are not leap years, unless they are also divisible by 400. This means that the year 2000 is a leap year and the year 2100 is not. The ISL12022M does not correct for the leap year in the year 2100.

# Control and Status Registers (CSR)

#### Addresses [07h to 0Fh]

The Control and Status Registers consist of the Status Register, Interrupt and Alarm Register, Analog Trimming and Digital Trimming Registers.

#### **STATUS REGISTER (SR)**

The Status Register is located in the memory map at address 07h. This is a volatile register that provides either control or status of RTC failure (RTCF), Battery Level Monitor (LBAT85, LBAT75), alarm trigger, Daylight Saving Time, crystal oscillator enable and temperature conversion in progress bit.

| ADDR | 7    | 6    | 5     | 4   | 3    | 2      | 1      | 0    |

|------|------|------|-------|-----|------|--------|--------|------|

| 07h  | BUSY | OSCF | DSTDJ | ALM | LVDD | LBAT85 | LBAT75 | RTCF |

#### **BUSY BIT (BUSY)**

Busy Bit indicates temperature sensing is in progress. In this mode, Alpha, Beta and ITRO registers are disabled and cannot be accessed.

#### **OSCILLATOR FAIL BIT (OSCF)**

Oscillator Fail Bit indicates that the oscillator has failed. The oscillator frequency is either zero or very far from the desired 32.768kHz due to failure, PC board contamination or mechanical issues.

#### DAYLIGHT SAVING TIME CHANGE BIT (DSTADJ)

DSTADJ is the Daylight Saving Time Adjusted Bit. It indicates the daylight saving time forward adjustment has happened. If a DST Forward event happens, DSTADJ will be set to "1". The DSTADJ bit will stay high when a DSTFD event happens, and will be reset to "0" when the DST Reverse event happens. It is read-only and cannot be written. Setting time during a DST forward period will not set this bit to "1".

The DSTE bit must be enabled when the RTC time is more than one hour before the DST Forward or DST Reverse event time setting, or the DST event correction will not happen.

DSTADJ is reset to "0" upon power-up. It will reset to "0" when the DSTE bit in Register 15h is set to "0" (DST disabled), but no time adjustment will happen.

#### ALARM BIT (ALM)

This bit announces if the alarm matches the real time clock. If there is a match, the respective bit is set to "1". This bit can be manually reset to "0" by the user or automatically reset by enabling the auto-reset bit (see ARST bit). A write to this bit in the SR can only set it to "0", not "1". An alarm bit that is set by an alarm occurring during an SR read operation will remain set after the read operation is complete.

#### LOW V<sub>DD</sub> INDICATOR BIT (LVDD)

This bit indicates when V<sub>DD</sub> has dropped below the pre-selected trip level (Brownout Mode). The trip points for the brownout levels are selected by three bits: V<sub>DD</sub> Trip2, V<sub>DD</sub> Trip1 and V<sub>DD</sub> Trip0 in PWR\_V<sub>DD</sub> registers. The LVDD detection is only enabled in V<sub>DD</sub> mode and the detection happens in real time. The LVDD bit is set whenever the V<sub>DD</sub> has dropped below the pre-selected trip level, and self clears whenever the V<sub>DD</sub> is above the pre-selected trip level.

#### LOW BATTERY INDICATOR 85% BIT (LBAT85)

In Normal Mode (V<sub>DD</sub>), this bit indicates when the battery level has dropped below the pre-selected trip levels. The trip points are selected by three bits: VB85Tp2, VB85Tp1 and VB85Tp0 in the PWR\_VBAT registers. The LBAT85 detection happens automatically once every minute when seconds register reaches 59. The detection can also be manually triggered by setting the TSE bit in BETA register to "1". The LBAT85 bit is set when the V<sub>BAT</sub> has dropped below the pre-selected trip level, and will self clear when the V<sub>BAT</sub> is above the pre-selected trip level at the next detection cycle either by manual or automatic trigger.

In Battery Mode ( $V_{BAT}$ ), this bit indicates the device has entered into battery mode by polling once every 10 minutes. The LBAT85 detection happens automatically once when the minute register reaches x9h or x0h minutes.

#### Example - When the LBAT85 is Set To "1" In Battery Mode:

The minute the register changes to 19h when the device is in battery mode, the LBAT85 is set to "1" the next time the device switches back to Normal Mode.

#### Example - When the LBAT85 Remains at "0" In Battery Mode:

If the device enters into battery mode after the minute register reaches 20h and switches back to Normal Mode before the minute register reaches 29h, then the LBAT85 bit will remain at "0" the next time the device switches back to Normal Mode.

#### LOW BATTERY INDICATOR 75% BIT (LBAT75)

In Normal Mode (V<sub>DD</sub>), this bit indicates when the battery level has dropped below the pre-selected trip levels. The trip points are selected by three bits: VB75Tp2, VB75Tp1 and VB75Tp0 in the PWR\_VBAT registers. The LBAT75 detection happens automatically once every minute when seconds register reaches 59. The detection can also be manually triggered by setting the TSE bit in BETA register to "1". The LBAT75 bit is set when the V<sub>BAT</sub> has dropped below the pre-selected trip level, and will self clear when the V<sub>BAT</sub> is above the pre-selected trip level at the next detection cycle either by manual or automatic trigger.

In Battery Mode ( $V_{BAT}$ ), this bit indicates the device has entered into battery mode by polling once every 10 minutes. The LBAT85 detection happens automatically once when the minute register reaches x9h or x0h minutes.

#### Example - When the LBAT75 is Set to "1" in Battery Mode:

The minute register changes to 30h when the device is in battery mode, the LBAT75 is set to "1" the next time the device switches back to Normal Mode.

#### Example - When the LBAT75 Remains at "0" in Battery Mode:

If the device enters into battery mode after the minute register reaches 49h and switches back to Normal Mode before minute register reaches 50h, then the LBAT75 bit will remain at "0" the next time the device switches back to Normal Mode.

#### **REAL TIME CLOCK FAIL BIT (RTCF)**

This bit is set to a "1" after a total power failure. This is a read only bit that is set by hardware (ISL12022M internally) when the device powers up after having lost all power (defined as  $V_{DD} = 0V$  and  $V_{BAT} = 0V$ ). The bit is set regardless of whether  $V_{DD}$  or  $V_{BAT}$  is applied first. The loss of only one of the supplies does not set the RTCF bit to "1". The first valid write to the RTC section after a complete power failure resets the RTCF bit to "0" (writing one byte is sufficient).

#### **Interrupt Control Register (INT)**

TABLE 3. INTERRUPT CONTROL REGISTER (INT)

| ADDR | 7    | 6    | 5  | 4      | 3   | 2   | 1   | 0   |

|------|------|------|----|--------|-----|-----|-----|-----|

| 08h  | ARST | WRTC | IM | FOBATB | F03 | F02 | F01 | F00 |

#### **AUTOMATIC RESET BIT (ARST)**

This bit enables/disables the automatic reset of the ALM, LVDD, LBAT85, and LBAT75 status bits only. When ARST bit is set to "1", these status bits are reset to "0" after a valid read of the respective status register (with a valid STOP condition). When the ARST is cleared to "0", the user must manually reset the ALM, LVDD, LBAT85, and LBAT75 bits.

#### WRITE RTC ENABLE BIT (WRTC)

The WRTC bit enables or disables write capability into the RTC Timing Registers. The factory default setting of this bit is "0". Upon initialization or power-up, the WRTC must be set to "1" to enable the RTC. Upon the completion of a valid write (STOP), the RTC starts counting. The RTC internal 1Hz signal is synchronized to the STOP condition during a valid write cycle.

#### **INTERRUPT/ALARM MODE BIT (IM)**

This bit enables/disables the interrupt mode of the alarm function. When the IM bit is set to "1", the alarm will operate in the interrupt mode, where an active low pulse width of 250ms will appear at the  $\overline{IRQ}/F_{OUT}$  pin when the RTC is triggered by the alarm, as defined by the alarm registers (OCh to 11h). When the IM bit is cleared to "0", the alarm will operate in standard mode, where the  $\overline{IRQ}/F_{OUT}$  pin will be set low until the ALM status bit is cleared to "0".

#### TABLE 4.

| IM BIT | INTERRUPT/ALARM FREQUENCY                    |

|--------|----------------------------------------------|

| 0      | Single Time Event Set By Alarm               |

| 1      | Repetitive/Recurring Time Event Set By Alarm |

#### FREQUENCY OUTPUT AND INTERRUPT BIT (FOBATB)

This bit enables/disables the  $\overline{IRQ}/F_{OUT}$  pin during battery backup mode (i.e.,  $V_{BAT}$  power source active). When the FOBATB is set to "1", the  $\overline{IRQ}/F_{OUT}$  pin is disabled during battery backup mode. This means that both the frequency output and alarm output functions are disabled. When the FOBATB is cleared to "0", the  $\overline{IRQ}/F_{OUT}$  pin is enabled during battery backup mode. Note that the open drain  $\overline{IRQ}/F_{OUT}$  pin will need a pull-up to the battery voltage to operate in battery backup mode.

#### FREQUENCY OUT CONTROL BITS (FO <3:0>)

These bits enable/disable the frequency output function and select the output frequency at the  $\overline{IRQ}/F_{OUT}$  pin. See Table 5 for frequency selection. Default for the ISL12022M is FO<3:0> = 1h, or 32.768kHz output ( $F_{OUT}$  is **ON**). When the frequency mode is enabled, it will override the alarm mode at the  $\overline{IRQ}/F_{OUT}$  pin.

TABLE 5. FREQUENCY SELECTION OF  $\overline{IRQ}/F_{OUT}$  PIN

| Frequency,<br>F <sub>out</sub> | UNITS | F03 | F02 | F01 | F00 |

|--------------------------------|-------|-----|-----|-----|-----|

| 0                              | Hz    | 0   | 0   | 0   | 0   |

| 32768                          | Hz    | 0   | 0   | 0   | 1   |

| 4096                           | Hz    | 0   | 0   | 1   | 0   |

| 1024                           | Hz    | 0   | 0   | 1   | 1   |

| 64                             | Hz    | 0   | 1   | 0   | 0   |

| 32                             | Hz    | 0   | 1   | 0   | 1   |

| 16                             | Hz    | 0   | 1   | 1   | 0   |

| 8                              | Hz    | 0   | 1   | 1   | 1   |

| 4                              | Hz    | 1   | 0   | 0   | 0   |

| 2                              | Hz    | 1   | 0   | 0   | 1   |

| 1                              | Hz    | 1   | 0   | 1   | 0   |

| 1/2                            | Hz    | 1   | 0   | 1   | 1   |

| 1/4                            | Hz    | 1   | 1   | 0   | 0   |

| 1/8                            | Hz    | 1   | 1   | 0   | 1   |

| 1/16                           | Hz    | 1   | 1   | 1   | 0   |

| 1/32                           | Hz    | 1   | 1   | 1   | 1   |

#### **Power Supply Control Register (PWR\_VDD)**

#### **CLEAR TIME STAMP BIT (CLRTS)**

| ADDR | 7     | 6 | 5 | 4 | 3 | 2                     | 1                     | 0                     |

|------|-------|---|---|---|---|-----------------------|-----------------------|-----------------------|

| 09h  | CLRTS | 0 | 0 | 0 | 0 | V <sub>DD</sub> Trip2 | V <sub>DD</sub> Trip1 | V <sub>DD</sub> Trip0 |

This bit clears Time Stamp  $V_{DD}$  to Battery (TSV2B) and Time Stamp Battery to  $V_{DD}$  Registers (TSB2V). The default setting is 0 (CLRTS = 0) and the Enabled setting is 1 (CLRTS = 1).

#### V<sub>DD</sub> BROWNOUT TRIP VOLTAGE BITS (V<sub>DD</sub>TRIP<2:0>)

These bits set the trip level for the  $V_{DD}$  alarm, indicating that  $V_{DD}$  has dropped below a preset level. In this event, the LVDD bit in the Status Register is set to "1". See <u>Table 6</u>.

| TABLE | 6. | VDD | TRIP | LEVELS |

|-------|----|-----|------|--------|

| V <sub>DD</sub> Trip2 | V <sub>DD</sub> Trip1 | V <sub>DD</sub> Trip0 | TRIP VOLTAGE<br>(V) |

|-----------------------|-----------------------|-----------------------|---------------------|

| 0                     | 0                     | 0                     | 2.295               |

| 0                     | 0                     | 1                     | 2.550               |

| 0                     | 1                     | 0                     | 2.805               |

| 0                     | 1                     | 1                     | 3.060               |

| 1                     | 0                     | 0                     | 4.250               |

| 1                     | 0                     | 1                     | 4.675               |

# Battery Voltage Trip Voltage Register (PWR\_VBAT)

This register controls the trip points for the two  $V_{BAT}$  alarms, with levels set to approximately 85% and 75% of the nominal battery level.