# Compact Smart Card Interface IC

The NCN6001 is an integrated circuit dedicated to the smart card interface applications. The device handles any type of smart card through a simple and flexible microcontroller interface. On top of that, thanks to the built—in chip select pin, several couplers can be connected in parallel.

The device is particularly suited for low cost, low power applications, with high extended battery life coming from extremely low quiescent current.

#### **Features**

- 100% Compatible with ISO 7816–3, EMV and GIE–CB Standards

- Fully GSM Compliant

- Wide Battery Supply Voltage Range: 2.7 < V<sub>CC</sub> < 5.5 V

- Programmable CRD\_VCC Supply Handles 1.8 V, 3.0 V or 5.0 V Card Operation

- Programmable Rise and Fall Card Clock Slopes

- Programmable Card Clock Divider

- Built-in Chip Select Logic Allows Parallel Coupling Operation

- ESD Protection on Card Pins (8.0 kV, Human Body Model)

- Supports up to 40 MHz Input Clock

- Built-in Programmable CRD\_CLK Stop Function Handles Run or Low State

- Programmable CRD\_CLK Slopes to Cope with Wide Operating Frequency Range

- Fast CRD VCC Turn-on and Turn-off Sequence

- These are Pb–Free Devices

#### **Typical Applications**

- E-Commerce Interface

- Automatic Teller Machine (ATM) Smart Card

- Point of Sales (POS) System

- Pay TV System

# ON Semiconductor®

www.onsemi.com

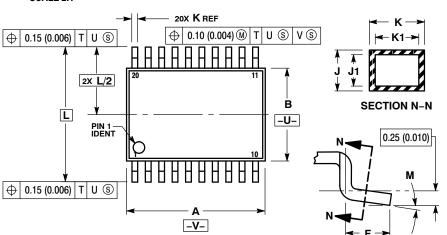

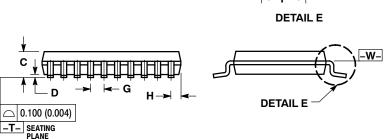

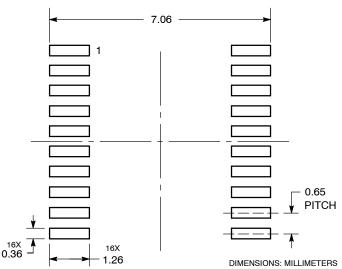

TSSOP-20 DTB SUFFIX CASE 948E

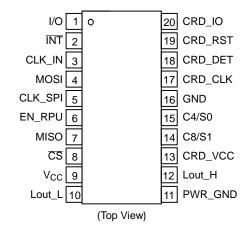

#### PIN CONNECTIONS

# **MARKING DIAGRAM**

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 32 of this data sheet.

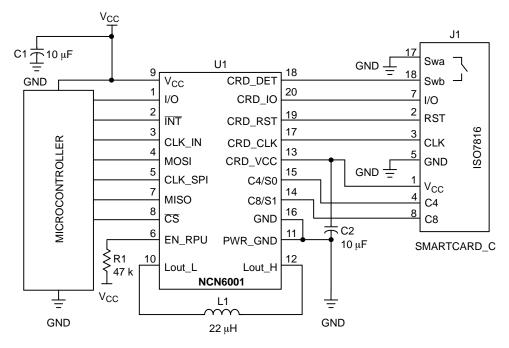

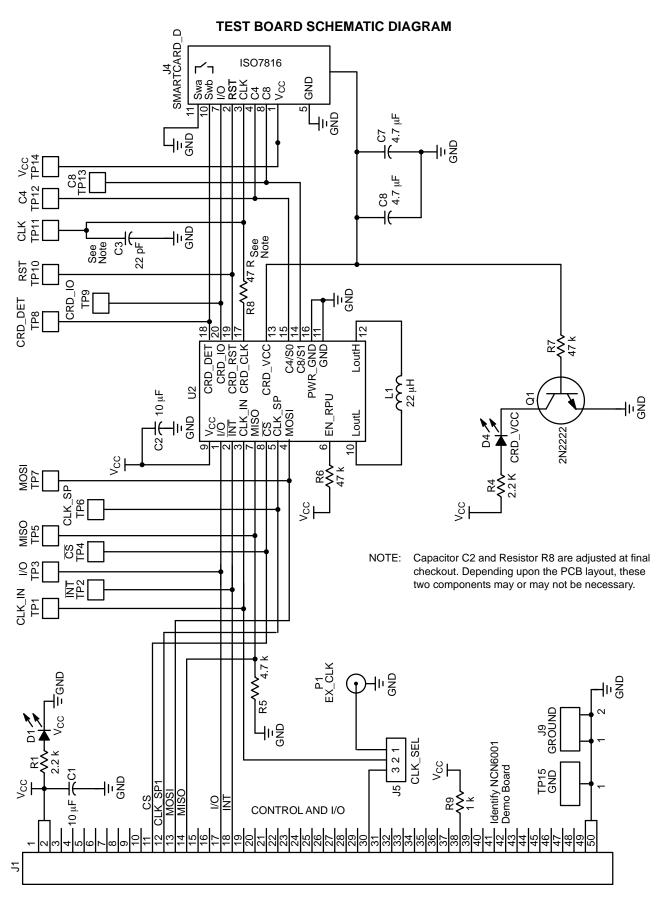

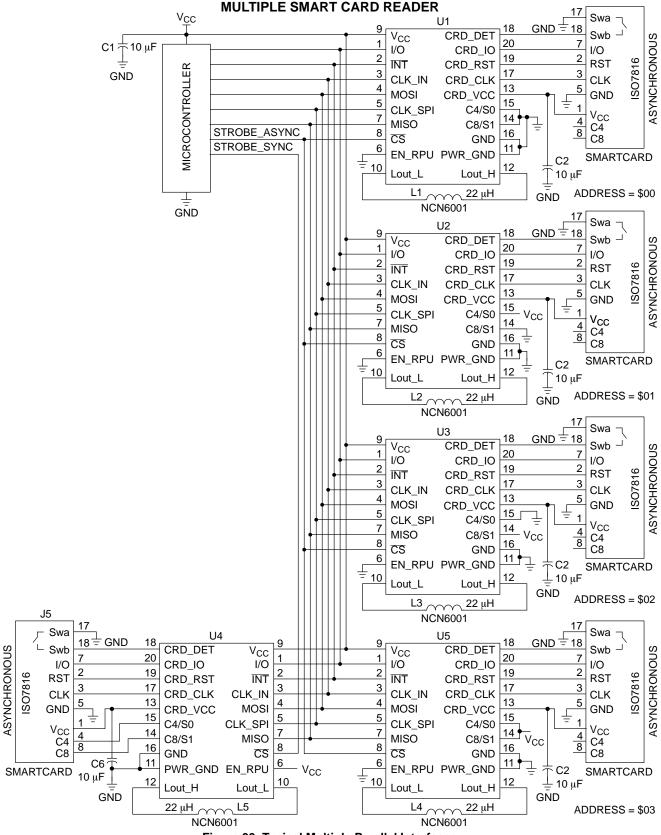

Figure 1. Typical Application

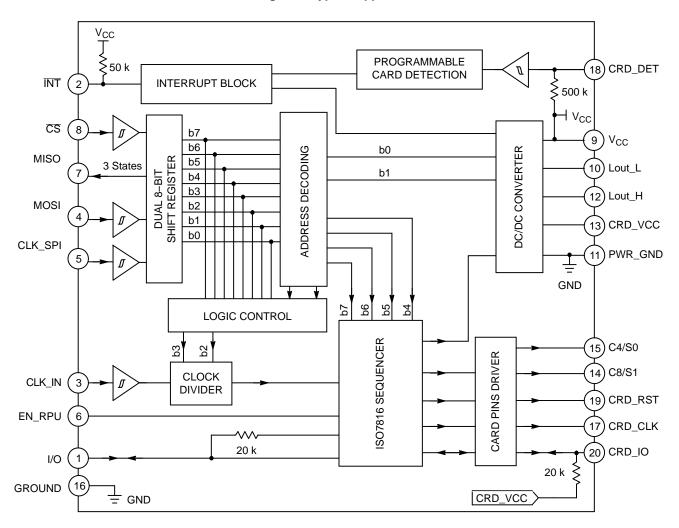

Figure 2. Block Diagram

# PIN FUNCTIONS AND DESCRIPTION

| TSSOP | Name            | Type                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | I/O             | Input/Output<br>Pullup              | This pin is connected to an external microcontroller interface. A bidirectional level translator adapts the serial I/O signal between the smart card and the microcontroller. The level translator is enabled when $\overline{CS} = L$ , the sub address has been selected and the system operates in the Asynchronous mode. When a Synchronous card is in use, this pin is disconnected and the data and the transaction take place with the MISO b3 register.                                    |

| ļ     |                 |                                     | The internal pullup resistor connected on the $\mu\text{C}$ side is activated and visible by the selected chip only.                                                                                                                                                                                                                                                                                                                                                                               |

| 2     | ĪNT             | OUTPUT<br>Pullup                    | This pin is activated LOW when a card has been inserted and detected by CRD_DET pin. Similarly, an interrupt is generated when the CRD_VCC output is overloaded, or when the card has been extracted whatever be the transaction status (running or standby).                                                                                                                                                                                                                                      |

|       |                 |                                     | The $\overline{\text{INT}}$ signal is reset to High according to Table 7 and Figure 10. On the other hand, the pin is forced to a logic High when the input voltage $V_{CC}$ drops below 2.0 V.                                                                                                                                                                                                                                                                                                    |

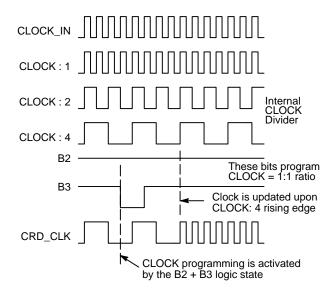

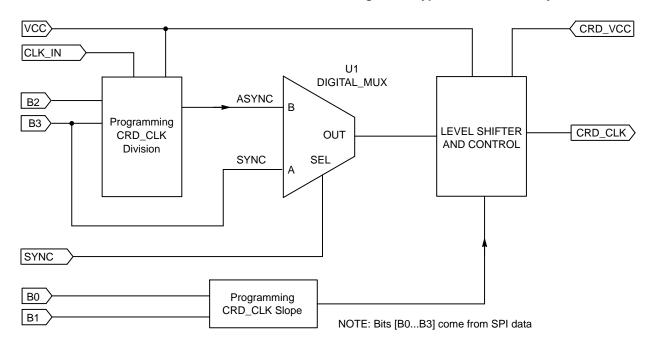

| 3     | CLK_IN          | CLOCK<br>INPUT<br>High<br>impedance | The built–in Schmitt trigger receiver makes this pin suitable for a large type of clock signal (Figure 29). This pin can be connected to either the microcontroller master clock, or to a crystal signal, to drive the external smart cards. The signal is fed to the internal clock selector circuit and translated to the CRD_CLK pin at either the same frequency, or divided by 2 or 4, depending upon the programming mode.                                                                   |

| ļ     |                 |                                     | Note: The chip guarantees the EMV 50% Duty Cycle when the clock divider ratio is 1/2 or 1/4, even when the CLK_IN signal is out of the 45% to 55% range specified by ISO and EMV specifications.                                                                                                                                                                                                                                                                                                   |

|       |                 |                                     | Care must be observed, at PCB level, to minimize the pick-up noise coming from the CLK_IN line.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4     | MOSI            | INPUT                               | Master Out Slave In: SPI Data Input from the external microcontroller. This byte contents the address of the selected chip among the four possible, together with the programming code for a given interface.                                                                                                                                                                                                                                                                                      |

| 5     | CLK_SPI         | INPUT                               | Clock Signal to synchronize the SPI data transfer. The built–in Schmitt trigger receiver makes this pin compatible with a wide range of input clock signal (Figure 29). This clock is fully independent from the CLK_IN signal and does not play any role with the data transaction.                                                                                                                                                                                                               |

| 6     | EN_RPU          | INPUT, Logic                        | This pin is used to activate the I/O internal pullup resistor according to the here below true table:  EN_RPU = Low → I/O Pullup resistor disconnected  EN_RPU = High → I/O Pullup resistor connected                                                                                                                                                                                                                                                                                              |

|       |                 |                                     | When two or more NCN6001 chips shares the same I/O bus, one chip only shall have the internal pullup resistor enabled to avoid any overload of the I/O line.                                                                                                                                                                                                                                                                                                                                       |

|       |                 |                                     | Moreover, when Asynchronous and Synchronous cards are handled by the interfaces, the activated I/O pullup resistor must preferably be the one associated with the Asynchronous circuit.                                                                                                                                                                                                                                                                                                            |

|       |                 |                                     | On the other hand, since no internal pullup bias resistor is built in the chip, pin 6 must be connected to the right voltage level to make sure the logic function is satisfied.                                                                                                                                                                                                                                                                                                                   |

| 7     | MISO            | OUTPUT                              | Master In Slave Out: SPI Data Output from the NCN6001. This byte carries the state of the interface, the serial transfer being achieved according to the programmed mode (Table 2), using the same CLK_SPI signal and during the same MOSI time frame. The three high bits [b7:b5] have no meaning and shall be discarded by the microcontroller. An external 4.7 k $\Omega$ Pull down resistor might be necessary to avoid misunderstanding of the pin 7 voltage during the High Z state.         |

| 8     | CS              | INPUT                               | This pin synchronizes the SPI communication and provides the chip address and selected functions.                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                 |                                     | All the NCN6001 functions, both programming and card transaction, are disabled when $\overline{\text{CS}} = \text{H.}$                                                                                                                                                                                                                                                                                                                                                                             |

| 9     | V <sub>CC</sub> | POWER                               | This pin is connected to the NCN6001 supply voltage and must be bypassed to ground by a 10 $\mu$ F/6.0 V capacitor. Since tantalum capacitors have relative high ESR, using low ESR ceramic type (MURATA X5R, Resr < 100 m $\Omega$ ) is highly recommended.                                                                                                                                                                                                                                       |

| 10    | Lout_L          | POWER                               | The Low Side of the external inductor is connected between this pin and pin 12 to provide the DC/DC function. The current flowing into this inductor is internally sensed and no external shunt resistor is used. Typically, Lout = 22 $\mu$ H, with DSR < 2.0 $\Omega$ , yields a good efficiency performance for a maximum 65 mA DC output load. Note: The inductor shall be sized to handle the 450 mA peak current flowing during the DC/DC operation (see CoilCraft manufacturer data sheet). |

# PIN FUNCTIONS AND DESCRIPTION (continued)

| TSSOP | Name    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|-------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 11    | PWR_GND | POWER  | This pin is the Power Ground associated with the built–in DC/DC converter and must be connected to the system ground together with GROUND pin 16. Using good quality ground plane is recommended to avoid spikes on the logic signal lines.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 12    | Lout_H  | POWER  | The High Side of the external inductor is connected between this pin and pin 10 to activate DC/DC function. The built–in NMOS and PMOS devices provide the switching function together with the CRD_VCC voltage rectification (Figure 16).  This pin provides the power to the external card. It is the logic level "1" for CRD_IO.                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 13    | CRD_VCC | POWER  | This pin provides the power to the external card. It is the logic level "1" for CRD_IO, CRD_RST, CRD_C4, CRD_C8 and CRD_CLK signals.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|       |         |        | The energy stored by the DC/DC external inductor Lout must be smoothed by a 10 $\mu F/Low$ ESR capacitor, connected across CRD_VCC and GND. Using ceramic type of capacitor (MURATA X5R, ESR < 50 m $\Omega$ ) is strongly recommended. In the event of a CRD_VCC U <sub>VLOW</sub> voltage, the NCN6001 detects the situation and feedback the information in the STATUS bit. The device does not take any further action, particularly the DC/DC converter is neither stopped nor re programmed by the NCN6001. It is up to the external MPU to handle the situation. |  |  |  |  |  |  |  |

|       |         |        | However, when the CRD_VCC is overloaded, the NCN6001 shuts off the DC/DC converter, runs a Power Down ISO sequence and reports the fault in the STATUS register.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

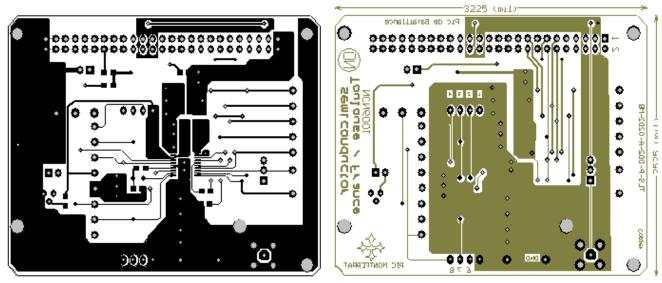

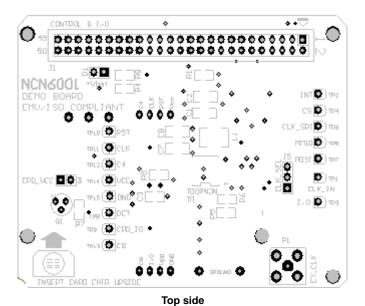

|       |         |        | Since high transient current flows from this pin to the load, care must be observed, at PCB level, to minimize the series ESR and ESL parasitic values. The NCN6001 demo board provides an example of a preferred PCB layout.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 14    | C8/S1   | I/O    | Auxiliary mixed analog/digital line to handle either a synchronous card, or as Chip Select Identification (MISO, Bit 0): see Figure 8. The pin is driven by an open drain stage, the pullup resistor being connected to the CRD_VCC supply. When the pin is used as a logic input (asynchronous cards), the positive logic condition applies:  Connected to GND → Logic = Zero                                                                                                                                                                                          |  |  |  |  |  |  |  |

|       |         |        | Connected to V <sub>CC</sub> or left Open → Logic = One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|       |         |        | A built–in accelerator circuit makes sure the output positive going rise time is fully within the ISO/EMV specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|       |         |        | NOTE: The pin is capable of reading the logic level when the chip operates an asynchronous interface, but is not intended to read the data from the external card when operated in the synchronous mode. It merely returns the logic state forced during a write instruction to the card.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 15    | C4/S0   | I/O    | Auxiliary mixed analog/digital line to handle either a synchronous card, or as Chip Select Identification (MISO, Bit 1): see Figure 8. The pin is driven by an open drain stage, the pullup resistor being connected to the CRD_VCC supply. When the pin is used as a logic input (asynchronous cards), the positive logic condition applies:                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|       |         |        | Connected to GND $\rightarrow$ Logic = Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|       |         |        | Connected to $V_{CC}$ or left Open $\rightarrow$ Logic = One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|       |         |        | A built–in accelerator circuit makes sure the output positive going rise time is fully within the ISO/EMV specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|       |         |        | NOTE: The pin is capable of reading the logic level when the chip operates an asynchronous interface, but is not intended to read the data from the external card when operated in the synchronous mode. It merely returns the logic state forced during a write instruction to the card.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 16    | GND     | SIGNAL | The logic and low level analog signals shall be connected to this ground pin. This pin must be externally connected to the PWR_GND pin 12. The designer must make sure no high current transients are shared with the low signal currents flowing into this pin.                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 17    | CRD_CLK | OUTPUT | This pin is connected to the CLK pin of the card connector. The CRD_CLK signal comes from the clock selector circuit output. An internal active pull down NMOS device forces this pin to Ground during either the CRD_VCC startup sequence, or when CRD_VCC = 0 V.  The rise and fall slopes, either FAST or SLOW, of this signal can be programmed by the MOSI message (Table 2).                                                                                                                                                                                      |  |  |  |  |  |  |  |

|       |         |        | Care must be observed, at PCB level, to minimize the pick–up noise coming from the CRD_CLK line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

# PIN FUNCTIONS AND DESCRIPTION (continued)

| TSSOP | Name    | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18    | CRD_DET | INPUT         | The signal coming from the external card connector is used to detect the presence of the card. A built–in pullup low current source biases this pin High, making it active LOW, assuming one side of the external switch is connected to ground. A built–in digital filter protect the system against voltage spikes present on this pin.                                        |

|       |         |               | The polarity of the signal is programmable by the MOSI message, according to the logic state depicted Table 2. On the other hand, the meaning of the feedback message contained in the MISO register bit b4, depends upon the SPI mode of operation as defined here below:                                                                                                       |

|       |         |               | SPI Normal Mode: The MISO bit b4 is High when a card is inserted, whatever be the polarity of the card detect switch.                                                                                                                                                                                                                                                            |

|       |         |               | SPI Special Mode: The MISO bit b4 copies the logic state of the Card detect switch as depicted here below, whatever be the polarity of the switch used to handle the detection:                                                                                                                                                                                                  |

|       |         |               | CRD_DET = Low → MISO/b4 = Low                                                                                                                                                                                                                                                                                                                                                    |

|       |         |               | CRD_DET = High → MISO/b4 = High                                                                                                                                                                                                                                                                                                                                                  |

|       |         |               | In both cases, the chip must be programmed to control the right logic state (Table 2). Since the bias current supplied by the chip is very low, typically 5.0 $\mu$ A, care must be observed to avoid low impedance or cross coupling when this pin is in the Open state.                                                                                                        |

| 19    | CRD_RST | OUTPUT        | This pin is connected to the RESET pin of the card connector. A level translator adapts the RESET signal from the microcontroller to the external card. The output current is internally limited to 15 mA.                                                                                                                                                                       |

|       |         |               | The CRD_RST is validated when $\overline{\text{CS}}$ = Low and hard wired to Ground when the card is deactivated, by and internal active pull down circuit.                                                                                                                                                                                                                      |

|       |         |               | Care must be observed, at PCB design level, to avoid cross coupling between this signal and the CRD_CLK clock.                                                                                                                                                                                                                                                                   |

| 20    | CRD_IO  | I/O<br>Pullup | This pin handles the connection to the serial I/O pin of the card connector. A bidirectional level translator adapts the serial I/O signal between the card and the microcontroller. An internal active pull down MOS device forces this pin to Ground during either the CRD_VCC startup sequence, or when CRD_VCC = 0 V. The CRD_IO pin current is internally limited to 15 mA. |

|       |         |               | Care must be observed, at PCB design level, to avoid cross coupling between this signal and the CRD_CLK clock.                                                                                                                                                                                                                                                                   |

# $\textbf{MAXIMUM RATINGS} \ (T_A = +25^{\circ}C \ unless \ otherwise \ noted)$

| Rating                                                                                                                                | Symbol                              | Value                                                                                                       | Unit           |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|

| Power Supply Voltage                                                                                                                  | V <sub>CC</sub>                     | 6.0                                                                                                         | V              |

| Power Supply Current Note: This current represents the maximum peak current the pin can sustain, not the NCN6001 average consumption. | I <sub>bat</sub>                    | 500                                                                                                         | mA             |

| Power Supply Current                                                                                                                  | I <sub>CC</sub>                     | 150 (Internally Limited)                                                                                    | mA             |

| Digital Input Pins                                                                                                                    | V <sub>in</sub>                     | $-0.5 \text{ V} < \text{V}_{\text{in}} < \text{V}_{\text{CC}} + 0.5 \text{ V}, \text{ but} < 6.0 \text{ V}$ | V              |

| Digital Input Pins                                                                                                                    | l <sub>in</sub>                     | ±5.0                                                                                                        | mA             |

| Digital Output Pins                                                                                                                   | V <sub>out</sub>                    | $-0.5 \text{ V} < \text{V}_{\text{in}} < \text{V}_{\text{CC}} + 0.5 \text{ V}, \text{ but} < 6.0 \text{ V}$ | V              |

| Digital Output Pins                                                                                                                   | I <sub>out</sub>                    | ±10                                                                                                         | mA             |

| Card Interface Pins                                                                                                                   | V <sub>card</sub>                   | -0.5 V < V <sub>card</sub> < CRD_VCC +0.5 V                                                                 | V              |

| Card Interface Pins, excepted CRD_CLK                                                                                                 | I <sub>card</sub>                   | 15 (Internally Limited)                                                                                     | mA             |

| Inductor Current                                                                                                                      | I <sub>Lout</sub>                   | 500 (Internally Limited)                                                                                    | mA             |

| ESD Capability (Note 1) Standard Pins Card Interface Pins CRD_DET                                                                     | V <sub>ESD</sub>                    | 2.0<br>8.0<br>4.0                                                                                           | kV<br>kV<br>kV |

| Power Dissipation @ Tamb = $+85^{\circ}$ C Thermal Resistance, Junction–to–Air ( $R_{\theta JA}$ )                                    | P <sub>DS</sub><br>R <sub>θJA</sub> | 320<br>125                                                                                                  | mW<br>°C/W     |

| Operating Ambient Temperature Range                                                                                                   | T <sub>A</sub>                      | -25 to +85                                                                                                  | °C             |

| Operating Junction Temperature Range                                                                                                  | TJ                                  | -25 to +125                                                                                                 | °C             |

| Maximum Junction Temperature (Note 2)                                                                                                 | T <sub>Jmax</sub>                   | +150                                                                                                        | °C             |

| Storage Temperature Range                                                                                                             | T <sub>stg</sub>                    | -65 to +150                                                                                                 | °C             |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Human Body Model, R = 1500 Ω, C = 100 pF.

2. Absolute Maximum Rating beyond which damage to the device may occur.

**DIGITAL PARAMETERS** @  $2.7 \text{ V} < \text{V}_{CC} < 5.5 \text{ V}$  ( $-25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  ambient temperature, unless otherwise noted). Note: Digital inputs undershoot < - 0.3 V to ground, Digital inputs overshoot < 0.3 V to  $V_{CC}$ .

| Rating                                                                                                                                                | Pin                 | Symbol                                     | Min                    | Тур    | Max                   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|------------------------|--------|-----------------------|------|

| Input Asynchronous Clock Duty Cycle = 50%  © V <sub>CC</sub> = 3.0 V Over the Temperature Range  © V <sub>CC</sub> = 5.0 V Over the Temperature Range | 3                   | F <sub>CLKIN</sub>                         | -<br>-                 | -<br>- | 30<br>40              | MHz  |

| Input Clock Rise Time                                                                                                                                 | 3                   | F <sub>tr</sub>                            | 2.5                    | _      | -                     | ns   |

| Input Clock Fall Time                                                                                                                                 |                     | F <sub>tf</sub>                            | 2.5                    | -      | _                     | ns   |

| Input SPI Clock                                                                                                                                       | 5                   | F <sub>CLKSPI</sub>                        | _                      | -      | 15                    | MHz  |

| Input CLK_SPI Rise/Fall Time @ Cout = 30 pF                                                                                                           | 5                   | tr <sub>spi</sub> , tf <sub>spi</sub>      | _                      | -      | 12                    | ns   |

| Input MOSI Rise/Fall Time @ Cout = 30 pF                                                                                                              | 4                   | tr <sub>mosi</sub> ,<br>tf <sub>mosi</sub> | -                      | -      | 12                    | ns   |

| Output MISO Rise/Fall Time @ Cout = 30 pF                                                                                                             | 7                   | tr <sub>miso</sub> ,<br>tf <sub>miso</sub> | -                      | _      | 12                    | ns   |

| Input CS Rise/Fall Time                                                                                                                               | 8                   | tr <sub>str</sub> , tf <sub>str</sub>      | _                      | -      | 12                    | ns   |

| I/O Data Transfer Switching Time, both directions (I/O and CRD_IO), @ Cout = 30 pF                                                                    | 1, 20               |                                            |                        |        |                       |      |

| I/O Rise Time * (Note 4)                                                                                                                              |                     | t <sub>RIO</sub>                           | _                      | _      | 0.8                   | μS   |

| I/O Fall Time                                                                                                                                         |                     | t <sub>FIO</sub>                           | _                      | -      | 0.8                   | μs   |

| INT Pullup Resistance                                                                                                                                 | 2                   | R <sub>ITA</sub>                           | 20                     | 50     | 80                    | kΩ   |

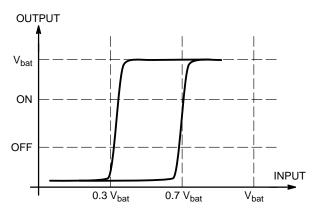

| Positive Going Input High Voltage Threshold (CLK_IN, MOSI, CLK_SPI, EN_RPU, $\overline{CS}$ )                                                         | 2, 3, 4, 5,<br>6, 8 | V <sub>IA</sub>                            | 0.70 * V <sub>CC</sub> | _      | V <sub>CC</sub>       | V    |

| Negative Going Input High Voltage Threshold (CLK_IN, MOSI, CLK_SPI, EN_RPU, CS)                                                                       | 2, 3, 4, 5,<br>6, 8 | V <sub>ILLA</sub>                          | 0                      | _      | 0.3 * V <sub>CC</sub> | V    |

| Output High Voltage $\overline{\text{INT}}$ , MISO @ O <sub>H</sub> = -10 $\mu$ A                                                                     | 2, 7                | V <sub>OH</sub>                            | V <sub>CC</sub> -1.0 V | _      | V <sub>CC</sub>       | V    |

| Output Low Voltage $\overline{\text{INT}}$ , MISO @ O <sub>H</sub> = 200 $\mu$ A                                                                      | 2, 7                | V <sub>OL</sub>                            | _                      | _      | 0.4                   | V    |

| Delay Between Two Consecutive CLK_SPI Sequence                                                                                                        | 5                   | td <sub>clk</sub>                          | 33                     | -      | -                     | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

<sup>performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Since a 20 kΩ (typical) pullup resistor is provided by the NCN6001, the external MPU can use an Open Drain connection. On the other hand, NMOS smart cards can be used straightforward.</sup>

**POWER SUPPLY** @  $2.7 \text{ V} < \text{V}_{CC} < 5.5 \text{ V}$  ( $-25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  ambient temperature, unless otherwise noted).

| Rating                                                                                                                                                                                                 | Pin | Symbol                                                       | Min                  | Тур                  | Max                  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| Input Power Supply                                                                                                                                                                                     | 9   | V <sub>CC</sub>                                              | 2.70                 | -                    | 5.50V                | V    |

| Standby Supply Current Conditions:                                                                                                                                                                     | 9   | ICC <sub>sb</sub>                                            | -<br>-               | 25<br>35             | 50<br>60             | μА   |

| DC Operating Current  CLK_IN = Low, All Card Pins Unloaded  @ V <sub>CC</sub> = 3.3 V, CRD_VCC = 5.0 V  @ V <sub>CC</sub> = 5.5 V, CRD_VCC = 5.0 V                                                     | 9   | ICC <sub>op</sub>                                            | -<br>-               | -<br>-               | 0.5<br>1.5           | mA   |

| V <sub>CC</sub> Under Voltage Detection <sub>High</sub> V <sub>CC</sub> Under Voltage Detection <sub>Low</sub> V <sub>CC</sub> Under Voltage (Note 6)                                                  | 9   | VCC <sub>LH</sub><br>VCC <sub>LL</sub><br>VCC <sub>POR</sub> | 2.20<br>2.00<br>1.50 | -<br>-<br>-          | 2.70<br>2.60<br>2.20 | V    |

| Output Card Supply Voltage  @ 2.7 V < V <sub>CC</sub> < 5.5 V  CRD_VCC = 1.8 V @ Iload = 35 mA  CRD_VCC = 3.0 V @ Iload = 60 mA  CRD_VCC = 5.0 V @ Iload = 65 mA                                       | 13  | V <sub>С2</sub> н<br>V <sub>С3</sub> н<br>V <sub>С5</sub> н  | 1.65<br>2.75<br>4.75 | 1.80<br>3.00<br>5.00 | 1.95<br>3.25<br>5.25 | V    |

| Maximum Continuous Output Current  @ CRD_VCC = 1.8 V  @ CRD_VCC = 3.0 V  @ CRD_VCC = 5.0 V                                                                                                             | 13  | ICC                                                          | 35<br>60<br>65       | _<br>_<br>_          | -<br>-<br>-          | mA   |

| Output Over Current Limit  V <sub>CC</sub> = 3.3 V, CRD_VCC = 1.8 V, 3.0 V or 5.0 V  V <sub>CC</sub> = 5.0 V, CRD_VCC = 1.8 V, 3.0 V or 5.0 V                                                          | 13  | Iccov                                                        | -<br>-               | 100<br>150           | -<br>-               | mA   |

| Output Dynamic Peak Current<br>@ CRD_VCC = 1.8 V, 3.0 V or 5.0 V, Cout = 10 $\mu$ F (Notes 4 and 5)                                                                                                    | 13  | Iccd                                                         | 100                  | _                    | _                    | mA   |

| Output Card Supply Voltage Ripple<br>@ $V_{CC} = 3.6$ V, Lout = 22 $\mu$ H, Cout1 = Cout2 = 4.7 $\mu$ F<br>Ceramic X7R, lout = 55 mA<br>CRD_VCC = 5.0 V<br>CRD_VCC = 3.0 V (Note 4)<br>CRD_VCC = 1.8 V | 13  | -                                                            | -<br>-<br>-          | 35<br>35<br>35       | -<br>-<br>-          | mV   |

| Output Card Supply Turn On Time @ Lout = 22 $\mu$ F, Cout1 = 10 $\mu$ F Ceramic $V_{CC}$ = 2.7 V, CRD_VCC = 5.0 V                                                                                      | 13  | VCC <sub>TON</sub>                                           | -                    | _                    | 500                  | μs   |

| Output Card Supply Shut Off Time @ Cout1 = 10 $\mu$ F, Ceramic V <sub>CC</sub> = 2.7 V, CRD_VCC = 5.0 V, VCC <sub>OFF</sub> < 0.4 V                                                                    | 13  | VCC <sub>TOFF</sub>                                          | -                    | 100                  | 250                  | μs   |

<sup>4.</sup> Ceramic X7R, SMD type capacitors are mandatory to achieve the CRD\_VCC specifications. When an electrolytic capacitor is used, the external filter must include a 220 nF, max 50 m $\Omega$  ESR capacitor in parallel, to reduce both the high frequency noise and ripple to a minimum. Depending upon the PCB layout, it might be necessary to use two 4.7  $\mu$ F/6.0 V/ceramic/X5R/SMD 0805 in parallel, yielding an improved CRD\_VCC ripple over the temperature range.

<sup>5.</sup> Pulsed current, according to ISO7816–3, paragraph 4.3.2.

6. No function externally available during the V<sub>CC</sub> POR sequence.

**SMART CARD INTERFACE** @  $2.7 \text{ V} < V_{CC} < 5.5 \text{ V}$  ( $-25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  ambient temperature, unless otherwise noted). Note: Digital inputs undershoot < -0.3 V to ground, Digital inputs overshoot < 0.3 V to  $V_{CC}$ .

| Rating                                                                                                                                                                                                                                  | Pin    | Symbol                                                                                        | Min                          | Тур                     | Max                               | Unit                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------|------------------------------|-------------------------|-----------------------------------|---------------------------|

| CRD_RST @ CRD_VCC = 1.8 V, 3.0 V, 5.0 V Output RESET $V_{OH}$ @ Irst = $-200 \mu A$ Output RESET $V_{OL}$ @ Irst = $200 \mu A$ Output RESET Rise Time @ Cout = $30 pF$ Output RESET Fall Time @Cout = $30 pF$                           | 19     | V <sub>OH</sub><br>V <sub>OL</sub><br>t <sub>R</sub><br>t <sub>F</sub>                        | CRD_VCC - 0.5<br>0<br>-<br>- |                         | CRD_VCC<br>0.4<br>100<br>100      | V<br>V<br>ns<br>ns        |

| CRD_CLK as a function of CRD_VCC                                                                                                                                                                                                        | 17     |                                                                                               |                              |                         |                                   |                           |

| CRD_VCC = +5.0 V or 3.0 V or 1.8V Output Frequency Output $V_{OH}$ @ Icrd_clk = -200 $\mu$ A Output $V_{OL}$ @ Icrd_clk = 200 $\mu$ A                                                                                                   |        | F <sub>CRDCLK</sub><br>V <sub>OH</sub><br>V <sub>OL</sub>                                     | CRD_VCC - 0.5                |                         | 20<br>CRD_VCC<br>+0.4             | MHz<br>V<br>V             |

| CRD_CLK Output Duty Cycle CRD_VCC = 5.0 V CRD_VCC = 3.0 V CRD_VCC = 1.8 V (Note 7)                                                                                                                                                      |        | F <sub>CRDDC</sub>                                                                            | 45<br>40<br>40               |                         | 55<br>60<br>60                    | %<br>%<br>%               |

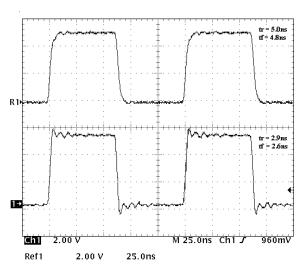

| Rise & Fall time @ CRD_VCC = 1.80 V to 5.0 V Fast Mode Output CRD_CLK Rise time @ Cout = 30 pF Output CRD_CLK Fall time @ Cout = 30 pF  Rise & Fall time @ CRD_VCC = 1.80 V to 5.0 V Slow Mode                                          |        | t <sub>ress</sub> t <sub>fcs</sub>                                                            | -<br>-                       | 2.1<br>1.9              | 4 4                               | ns<br>ns                  |

| Output CRD_CLK Rise time @ Cout = 30 pF<br>Output CRD_CLK Fall time @ Cout = 30 pF                                                                                                                                                      |        | t <sub>rills</sub><br>t <sub>ulsa</sub>                                                       | -<br>-                       | 11.5<br>10.8            | 16<br>16                          | ns<br>ns                  |

| CRD_IO @ CRD_VCC = 1.8 V 3.0 V, 5.0 V CRD_IO Data Transfer Frequency CRD_IO Rise time @ Cout = 30 pF CRD_IO Fall time @ Cout = 30 pF Output $V_{OH}$ @ Icrd_clk = $-20 \mu A$ Output $V_{OL}$ @ Icrd_clk = $500 \mu A$ , $V_{IL}$ = 0 V | 20     | F <sub>IO</sub><br>t <sub>RIO</sub><br>t <sub>FIO</sub><br>V <sub>OH</sub><br>V <sub>OL</sub> | -<br>-<br>-<br>CRD_VCC - 0.5 | 400<br>-<br>-<br>-<br>- | -<br>0.8<br>0.8<br>CRD_VCC<br>0.4 | kHz<br>μs<br>μs<br>V<br>V |

| CRD_IO Pullup Resistor                                                                                                                                                                                                                  | 20     | R <sub>CRDPU</sub>                                                                            | 14                           | 20                      | 26                                | kΩ                        |

| CRD_C8 Output Rise and Fall Time @ Cout = 30 pF                                                                                                                                                                                         | 14     | t <sub>RC8</sub> , t <sub>FC8</sub>                                                           | _                            | _                       | 100                               | ns                        |

| CRD_C4 Output Rise and Fall Time @ Cout = 30 pF                                                                                                                                                                                         | 15     | t <sub>RC4</sub> , t <sub>FC4</sub>                                                           | _                            | _                       | 100                               | ns                        |

| CRD_C4 and CRD_C8 Data Transfer Frequency                                                                                                                                                                                               | 14, 15 | F <sub>C48</sub>                                                                              | _                            | 400                     | -                                 | kHz                       |

| CRD_C8, CRD_C4 Output Voltages High Level @ Irst = -200 μA Low Level @ Irst = +200 μA                                                                                                                                                   | 14, 15 | V <sub>OH</sub> , V <sub>OL</sub>                                                             | CRD_VCC - 0.5                |                         | _<br>0.4                          | V                         |

| C8/S0 and C4/S0 Address Bias Current (Note 8)                                                                                                                                                                                           | 14, 15 | I <sub>bc4c8</sub>                                                                            | _                            | 1.0                     | -                                 | μΑ                        |

| Card Detection Digital Filter Delay:<br>Card Insertion<br>Card Extraction                                                                                                                                                               | 18     | T <sub>CRDIN</sub><br>T <sub>CRDOFF</sub>                                                     | 25<br>25                     | 50<br>50                | 150<br>150                        | μ <b>s</b><br>μ <b>s</b>  |

| Card Insertion or Extraction Positive Going Input High Voltage                                                                                                                                                                          | 18     | V <sub>IHDET</sub>                                                                            | 0.70 * V <sub>CC</sub>       | -                       | V <sub>CC</sub>                   | V                         |

| Card Insertion or Extraction Negative Going Input Low Voltage                                                                                                                                                                           | 18     | V <sub>ILDET</sub>                                                                            | 0                            | -                       | 0.30 * V <sub>CC</sub>            | V                         |

| Card Detection Bias Pullup Current @ V <sub>CC</sub> = 5.0 V                                                                                                                                                                            | 18     | I <sub>DET</sub>                                                                              | -                            | 10                      | -                                 | μΑ                        |

| Output Peak Max Current Under Card Static Operation Mode @ CRD_VCC = 3.0 V or = 5.0 V CRD_RST, CRD_IO, CRD_C4, CRD_C8                                                                                                                   | 1, 20  | lcrd_iorst                                                                                    | -                            | -                       | 15                                | mA                        |

| Output Peak Max Current Under Card Static Operation Mode @ CRD_VCC = 3.0 V or = 5.0 V CRD_CLK                                                                                                                                           | 17     | lcrd_clk                                                                                      | -                            | -                       | 70                                | mA                        |

Parameter guaranteed by design, function 100% production tested.

Depending upon the environment, using and external pullup resistor might be necessary to cope with PCB surface leakage current.

# **PROGRAMMING**

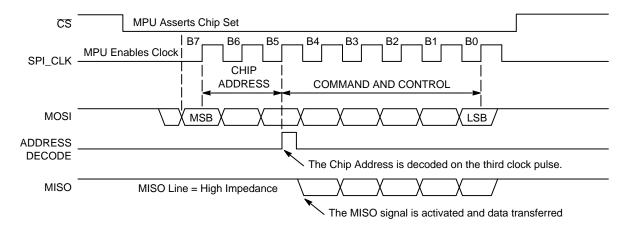

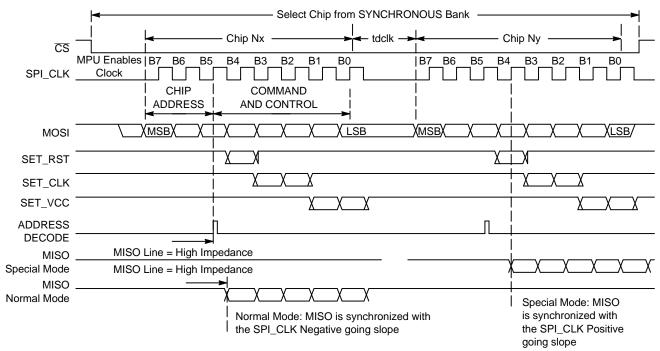

#### Write Register → WRT\_REG

The WRT\_REG register handles three command bits [b5:b7] and five data bits [b0:b4] as depicted in Table 1. These bits are concatenated into a single byte to accelerate the programming sequence. The register can be updated when  $\overline{\text{CS}}$  is low only.

The CRD\_RST pin reflects the content of the MOSI WRT\_REG[b4] during the chip programming sequence. Since this bit shall be Low to address the internal register of the chip, care must be observed as this signal will be immediately transferred to the CRD\_RST pin.

Table 1. WRT\_REG BITS DEFINITIONS

```

If (b7 + b6 + b5) <> 110 and (b7 + b6 + b5) <> 101 and (b7 + b6 + b5) <> 111 then

b1

Case 00

CRD VCC = 0 V

Case 01

CRD_VCC = 1.8 V

Case 10

CRD_VCC = 3.0 V

Case 11

CRD_VCC = 5.0 V

Else if (b7 + b6 + b5) = 110 then

b1 drives C4

b0 drives C8

Else if (b7 + b6 + b5) = 101 then

Case (b4 + b3 + b2 + b1 + b0) = 0000

CRD_DET = NO

Case (b4 + b3 + b2 + b1 + b0) = 0001

CRD_DET = NC

Case (b4 + b3 + b2 + b1 + b0) = 0010

SPI_MODE = Special

Case (b4 + b3 + b2 + b1 + b0) = 0011

SPI_MODE = Normal

b2.

If (b7 + b6 + b5) <> 110 and (b7 + b6 + b5) <> 101 and (b7 + b6 + b5) <> 111 then

b3

Case 00

CRD\_CLK = L

Case 01

CRD_CLK = CLK_IN

Case 10

CRD\_CLK = CLK\_IN/2

Case 11

CRD_CLK = CLK_IN/4

Else if (b7 + b6 + b5) = 110 then

b3 drives CRD_CLK

b2 drives CRD IO

Else if (b7 + b6 + b5) = 101 then

Case (b4 + b3 + b2 + b1 + b0) = 0000

CRD_DET = NO

Case (b4 + b3 + b2 + b1 + b0) = 0001

CRD_DET = NC

Case (b4 + b3 + b2 + b1 + b0) = 0010

SPI_MODE = Special

Case (b4 + b3 + b2 + b1 + b0) = 0011

SPI_MODE = Normal

End if

b4

Drives CRD_RST pin (Note 10)

b5,

000

Select Asynchronous Card #0 (Note 9), four chips bank CS signal

001

b6

Select Asynchronous Card #1 (Note 9), four chips bank CS signal

010

Select Asynchronous Card #2 (Note 9), four chips bank CS signal

b7

011

Select Asynchronous Card #3 (Note 9), four chips bank CS signal

100

Select External Asynchronous Card, dedicated CS signal

110

Select External Synchronous Card, dedicated CS signal

101

Set Card Detection Switch polarity, Set SPI_MODE normal or special. Set CRD_CLK slopes Fast or Slow.

111

Reserved for future use

```

When operating in Asynchronous mode, [b5:b7] are compared with the external voltage levels present pins C4/S0 and C8/S1 (respectively pins 15 and 14).

<sup>10.</sup> The CRD\_RST pin reflects the content of the MOSI WRT\_REG[b4] during the chip programming sequence. Since this bit shall be Low to address the internal register of the chip, care must be observed as this signal will be immediately transferred to the CRD\_RST pin.

Table 2. WRT\_REG BITS DEFINITIONS AND FUNCTIONS

| Δ            | DDRES | SS |    |     | PARAI | METER | S  |    |                      |                      |                      |

|--------------|-------|----|----|-----|-------|-------|----|----|----------------------|----------------------|----------------------|

| CHIP<br>BANK |       |    |    |     |       |       |    |    | MOSI bits<br>[b3:b2] | MOSI bits<br>[b1:b0] | MOSI bits<br>[b7:b0] |

| 1            | b7    | b6 | b5 | b4  | b3    | b2    | b1 | b0 | CRD_CLK              | CRD_VCC              | CRD_DET              |

| 1            | 0     | Х  | Х  | RST | 0     | 0     | 0  | 0  | Low                  | 0                    | -                    |

| 1            | 0     | Х  | Х  | RST | 0     | 1     | 0  | 1  | 1/1                  | 1.8 V                | -                    |

| 1            | 0     | Х  | Х  | RST | 1     | 0     | 1  | 0  | 1/2                  | 3.0 V                | -                    |

| 1            | 0     | Х  | Х  | RST | 1     | 1     | 1  | 1  | 1/4                  | 5.0 V                | -                    |

| 1            | 1     | 0  | 1  | 0   | 0     | 0     | 0  | 0  | _                    | -                    | NO                   |

| 1            | 1     | 0  | 1  | 0   | 0     | 0     | 0  | 1  | _                    | -                    | NC                   |

| 1            | 1     | 0  | 1  | 0   | 0     | 0     | 1  | 0  | -                    | -                    | Special              |

| 1            | 1     | 0  | 1  | 0   | 0     | 0     | 1  | 1  | -                    | -                    | Normal               |

| 1            | 1     | 0  | 1  | 0   | 0     | 1     | 0  | 0  | -                    | -                    | SLO_SLP              |

| 1            | 1     | 0  | 1  | 0   | 0     | 1     | 0  | 1  | -                    | -                    | FST_SLP              |

| 1            | 1     | 1  | 1  | -   | _     | _     | _  | _  | -                    | -                    | RFU                  |

| 2            | 1     | 0  | 0  | RST | 0     | 0     | 0  | 0  | Low                  | 0                    | -                    |

| 2            | 1     | 0  | 0  | RST | 0     | 1     | 0  | 1  | 1/1                  | 1.8 V                | -                    |

| 2            | 1     | 0  | 0  | RST | 1     | 0     | 1  | 0  | 1/2                  | 3.0 V                | -                    |

| 2            | 1     | 0  | 0  | RST | 1     | 1     | 1  | 1  | 1/4                  | 5.0 V                | -                    |

| 2            | 1     | 1  | 0  | RST | CLK   | I/O   | C4 | C8 | -                    | -                    | Data to Sync. Card   |

| 2            | 1     | 0  | 1  | 0   | 0     | 0     | 0  | 0  | -                    | -                    | NO                   |

| 2            | 1     | 0  | 1  | 0   | 0     | 0     | 0  | 1  | -                    | -                    | NC                   |

| 2            | 1     | 0  | 1  | 0   | 0     | 0     | 1  | 0  | -                    | -                    | Special              |

| 2            | 1     | 0  | 1  | 0   | 0     | 0     | 1  | 1  | -                    | -                    | Normal               |

| 2            | 1     | 0  | 1  | 0   | 0     | 1     | 0  | 0  | -                    | -                    | SLO_SLP              |

| 2            | 1     | 0  | 1  | 0   | 0     | 1     | 0  | 1  | -                    | -                    | FST_SLP              |

| 2            | 1     | 1  | 1  | _   | _     | _     | -  | -  | -                    | -                    | RFU                  |

<sup>11.</sup> Chip Bank 1 = Asynchronous cards, four slots addresses 1 to 4. Chip Bank 2 = Asynchronous or synchronous card, single slot.

Although using the %111XXXXX code is harmless from a NCN6001 silicon standpoint, care must be observed to avoid uncontrolled operation of the interface sharing the same digital bus. When this code is presented on the digital bus, the CRD\_RST signal of any interface sharing the CS signal, immediately reflects the digital content of the MOSI bit b4 register. Similarly, the MISO register of the shared interface is presented on the SPI port. Consequently, data collision, at MISO level, and uncontrolled card operation are

likely to happen if the system uses a common Chip Select line. It is strongly recommended to run a dedicated  $\overline{CS}$  bit to any external circuit intended to use the \$111xxxxx code.

On the other hand, the CRD\_RST signal will be forced to Low when the internal register of the chip is programmed to accommodate different hardware conditions (NO/NC, Special/Normal, SLO\_SLP/FST\_SLP). Generally speaking, such a configuration shall take place during the Power On Reset to avoid CRD\_RST activation.

<sup>12.</sup> Address 101 and bits [b0 : b4] not documented in the table are reserved for future use. Address 111 is reserved for future use.

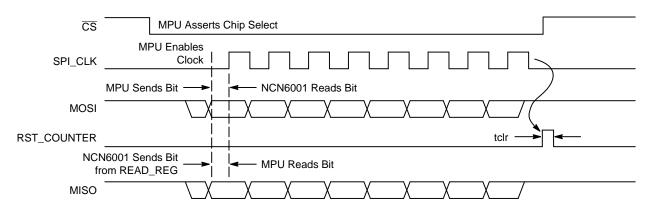

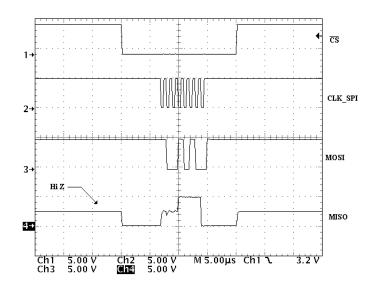

## Read Register → READ\_REG

The READ\_REG register contains the data read from the interface and from the external card. The selected register is transferred to the MISO pin during the MOSI sequence  $(\overline{CS} = \text{Low})$ . Table 3 gives the bits definition.

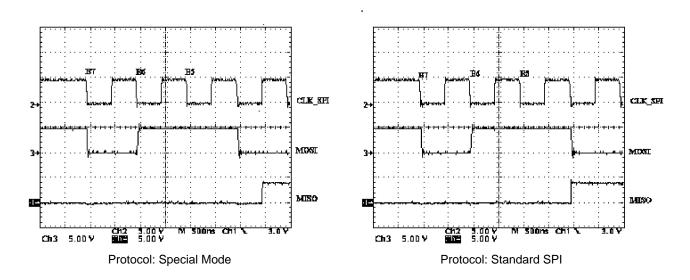

Depending upon the programmed SPI\_MODE, the content of READ\_REG is transferred on the MISO line

either on the Positive going (SPI\_MODE = Special) or upon the Negative going slope (SPI\_MODE = Normal) of the CLK\_SPI signal. The external microcontroller shall discard the three high bytes since they carry no valid data.

Table 3. MOSI AND MISO BITS IDENTIFICATIONS AND FUNCTIONS

| MOSI | b7 | b6 | b5 | b4          | b3  | b2  | b1              | b0              | Operating Mode              |

|------|----|----|----|-------------|-----|-----|-----------------|-----------------|-----------------------------|

|      | 0  | 0  | 0  | RST         | CLK | CLK | V <sub>CC</sub> | V <sub>CC</sub> | Asynchronous, Program Chip  |

|      | 0  | 0  | 1  | RST         | CLK | CLK | $V_{CC}$        | $V_{CC}$        | Asynchronous, Program Chip  |

|      | 0  | 1  | 0  | RST         | CLK | CLK | $V_{CC}$        | $V_{CC}$        | Asynchronous, Program Chip  |

|      | 0  | 1  | 1  | RST         | CLK | CLK | $V_{CC}$        | $V_{CC}$        | Asynchronous, Program Chip  |

|      | 1  | 0  | 0  | RST         | CLK | CLK | $V_{CC}$        | $V_{CC}$        | Asynchronous, Program Chip  |

|      | 1  | 1  | 0  | RST         | CLK | I/O | C4              | C8              | Synchronous, Sets Card Bits |

| MISO | z  | z  | z  | Card Detect | I/O | C4  | C8              | PWR Monitor     | Read Back Data              |

#### **ASYNCHRONOUS MODE**

In this mode, the CRD\_C4 and CRD\_C8 pins are used to define the physical addresses of the interfaces when a bank of up to four NCN6001 share the same digital bus.

#### SYNCHRONOUS MODE

In this mode, CRD\_C4 and CRD\_C8 are connected to the smart card and it is no longer possible to share the  $\overline{CS}$  signal with other device. Consequently, a dedicated Chip Select signal must be provided when the interfaces operate in a multiple operation mode (Figure 33).

On the other hand, since bits [b4 - b0] of the MOSI register contain the smart card data, programming the

STAA MOSI

CRD\_VCC output voltage shall be done by sending a previous MOSI message according to Table 1 and Table 2.

The CRD\_RST pin reflects the content of the MOSI WRT\_REG[b4] during the chip programming sequence. Since this bit shall be Low to address the internal register of the chip, care must be observed as this signal will be immediately transferred to the CRD\_RST pin.

Since no physical address can exist when the chip operates in this mode, the MOSI register must use the format %100XXXXX to program the chip (%100 prefix, XXXXX data).

### Example:

LDAA #% 10010111 ;set RST = H, CLK = 1/1, VCC = 5.0 V STAA MOSI LDAA #% 11010011 ;SYNC. Card: set RST = H, CLK = L, IO = L, C4 = H, C8= H STAA MOSI LDAA #%00111110 ;ASYNC. Card: set RST = H, CLK =  $\frac{1}{4}$ , VCC = 3.0 V

#### STARTUP DEFAULT CONDITIONS

At startup, when the  $V_{CC}$  power supply is turned on, the internal POR circuit sets the chip in the default conditions as defined in Table 4.

**Table 4. STARTUP DEFAULT CONDITIONS**

| CRD_DET  | Normally Open          |

|----------|------------------------|

| CRD_VCC  | Off                    |

| CRD_CLK  | $t_r$ and $t_f = SLOW$ |

| CRD_CLK  | Low                    |

| Protocol | Special Mode           |

#### **CARD DETECTION**

The card is detected by the external switch connected pin 18. The internal circuit provides a positive bias of this pin and the polarity of the insertion/extraction is programmable by the MOSI protocol as depicted in Table 2.

The bias current is  $1.0\,\mu A$  typical and care must be observed to avoid leakage to ground from this pin to maintain the logic function. In particular, using a low impedance probe (<  $1.0\,M\Omega$ ) may lead to uncontrolled operation during the debug.

Depending upon the programmed condition, the card can be detected either by a Normally Open (default condition) or a Normally Close switch (Table 2). On the other hand, the meaning of the feedback message contained in the MISO register bit b4, depends upon the SPI mode of operation as defined here below:

SPI Normal Mode: the MISO bit b4 is High when a card is inserted, whatever be the polarity of the card detect switch. SPI Special Mode: the MISO bit b4 copies the logic state of

*SPI Special Mode:* the MISO bit b4 copies the logic state of the Card detect switch as depicted here below, whatever be the polarity of the switch used to handle the detection:

$$CRD\_DET = Low \rightarrow MISO/b4 = Low$$

$CRD\_DET = High \rightarrow MISO/b4 = High$

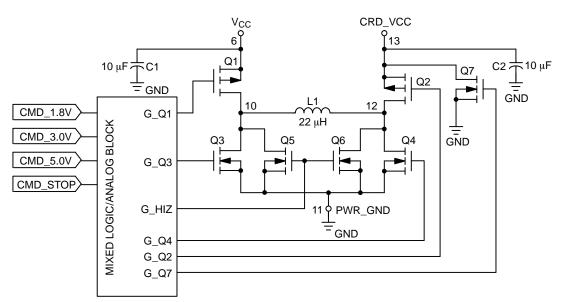

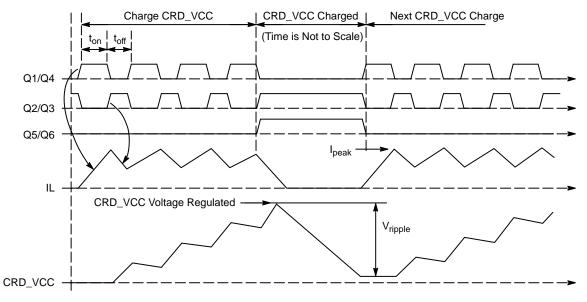

#### **CRD VCC OPERATION**

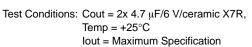

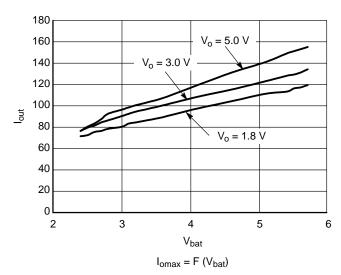

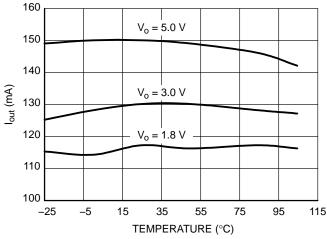

The built–in DC/DC converter provides the CRD\_VCC voltage and can be programmed to run one of the three possible values, 1.8 V, 3.0 V or 5.0 V, assuming the input voltage  $V_{CC}$  is within the 2.7 V to 5.5 V range. In any case, CRD\_VCC is voltage regulated, together with a current overload detection. On the other hand, the power conversion is automatically switched to handle either a boost or a buck mode of operation, depending upon the difference between the input voltage  $V_{CC}$  and the output supply CRD\_VCC.

The CRD\_VCC output current is a function of the  $V_{CC}$  input value as depicted in Table 5.

Table 5. CRD VCC OUTPUT VOLTAGE RANGE

| CRD_VCC | Comments                          |

|---------|-----------------------------------|

| 1.80 V  | Maximum Output DC Current = 35 mA |

| 3.0 V   | Maximum Output DC Current = 60 mA |

| 5.0 V   | Maximum Output DC Current = 65 mA |

Whatever the CRD\_VCC output voltage may be, a built—in comparator makes sure the voltage is within the ISO7816–3/EMV specifications. If the voltage is no longer within the minimum/maximum values, the DC/DC is switched Off, the Power Down sequence takes place and an interrupt is presented at the INT pin 2.

# **POWERUP SEQUENCE**

The Powerup Sequence makes sure all the card related signals are Low during the CRD\_VCC positive going slope. These lines are validated when CRD\_VCC is above the minimum specified voltage (depending upon the programmed CRD\_VCC value).

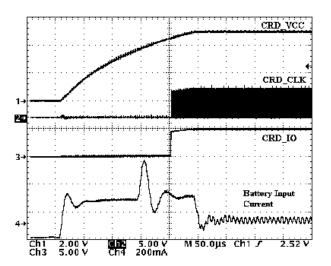

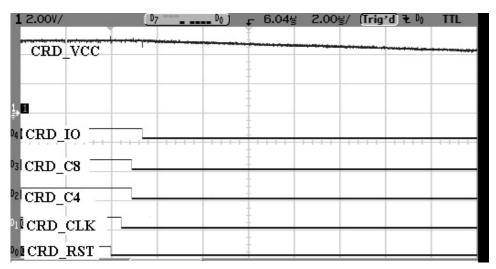

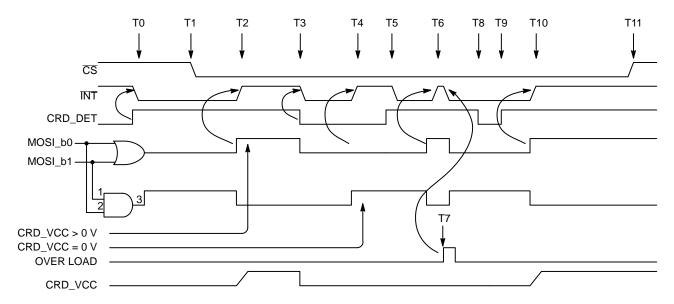

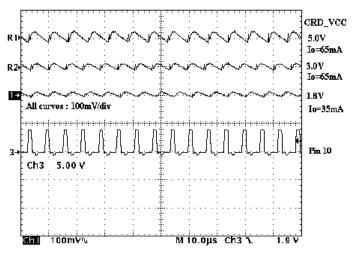

Figure 3. Typical Startup CRD\_VCC Sequence

At powerup, the CRD\_VCC voltage rise time depends upon the current capability of the DC/DC converter associated with the external inductor L1 and the reservoir capacitor connected across CRD\_VCC and GROUND. During this sequence, the average input current is 300 mA typical (Figure 3), assuming the system is fully loaded during the startup. Finally, the application software is responsible for the smart card signal sequence.

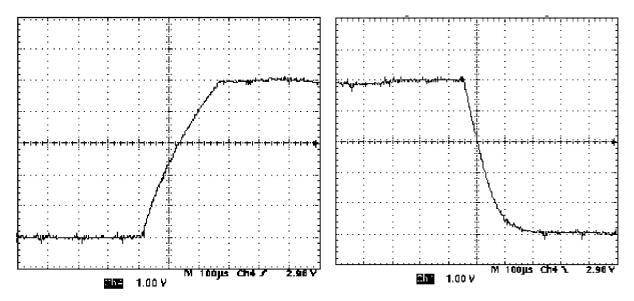

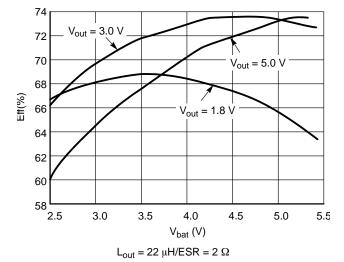

On the other hand, at turn off, the CRD\_VCC fall time depends upon the external reservoir capacitor and the peak

current absorbed by the internal NMOS transistor built across CRD\_VCC and GROUND. These behaviors are depicted in Figure 4.

Since these parameters have finite values, depending upon the external constraints, the designer must take care of these limits if the  $t_{\rm ON}$  or the  $t_{\rm OFF}$  provided by the data sheets does not meet his requirements.

Figure 4. CRD\_VCC Typical Rise and Fall Time

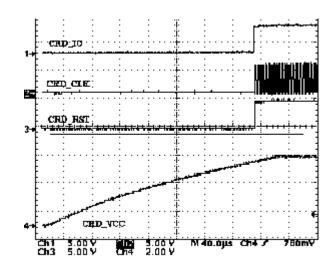

Figure 5. Startup Sequence with ATR

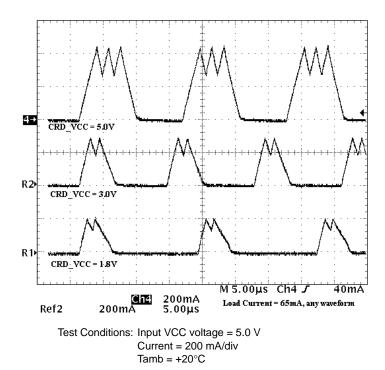

#### **POWER DOWN SEQUENCE**

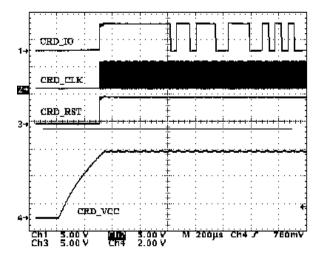

The NCN6001 provides an automatic Power Down sequence, according to the ISO7816–3 specifications, and the communication session terminates immediately. The sequence is launched when the card is extracted, or when the CRD\_VCC voltage is overloaded as described by the ISO/CEI 7816–3 sequence depicted hereafter:

ISO7816–3 sequence:

- →Force RST to Low

- →Force CLK to Low, unless it is already in this state

- →Force C4 & C8 to Low

- →Force CRD IO to Low

- →Shut Off the CRD VCC supply

Since the internal digital filter is activated for any card insertion or extraction, the physical power sequence will be activated 50  $\mu s$  (typical) after the card has been extracted. Of course, such a delay does not exist when the MPU intentionally launches the power down. Figure 6 shows the oscillogram captured in the NCN6001 demo board.

The internal active pull down NMOS connected across CRD\_VCC and GND discharges the external reservoir capacitor in 100  $\mu$ s (typical), assuming Cout = 10  $\mu$ F.

Typical delay between each signal is 500 ns

Figure 6. Typical Power Down Sequence

The internal active pull down NMOS connected across CRD\_VCC and GND discharges the external reservoir capacitor in  $100 \,\mu s$  (typical), assuming Cout =  $10 \,\mu F$ .

#### **DATA I/O LEVEL SHIFTER**

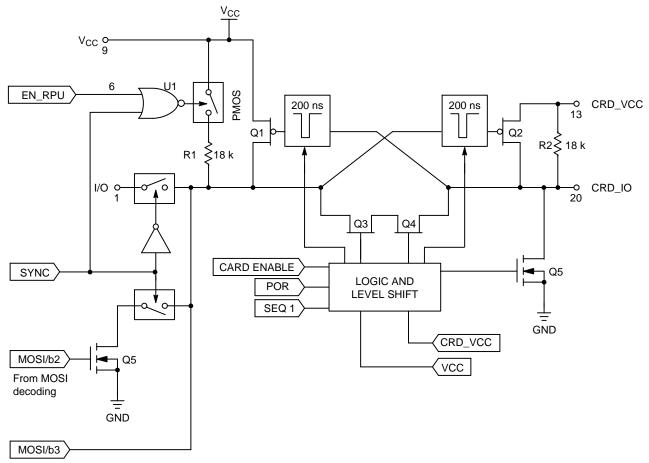

The level shifter accommodates the voltage difference that might exist between the microcontroller and the smart card. A pulsed accelerator built—in circuit provides the fast positive going transient according to the ISO7816–3 specifications. The basic I/O level shifter is depicted in Figure 7.

Figure 7. Basic I/O Internal Circuit

The transaction is valid when the Chip Select pin is Low, the I/O signal being Open Drain or Totem Pole on either sides.

Since the device can operate either in a single or a multiple card system, provisions have been made to avoid CRD\_IO current overload. Depending upon the selected mode of operation (ASYNC. or Sync), the card I/O line is respectively connected to either I/O pin 1, or to the MOSI register byte bit 2. On the other hand, the logic level present at the card I/O is feedback to the  $\mu$ C via the MISO register bit 3. The logic level present at pin 6 controls the connection of the internal pullup as depicted in Table 6.

Table 6. I/O PULLUP RESISTOR TRUE TABLE

| EN_RPU | I/O Pullup Resistor          | Device<br>Operation |

|--------|------------------------------|---------------------|

| Low    | Open, 18 kΩ disconnected     | Parallel Mode       |

| High   | Internal 18 kΩ pullup active | Single Device       |

NOTE: 18 kΩ typical value

NOTE: Both sides of the interface run with open drain load (worst case condition).

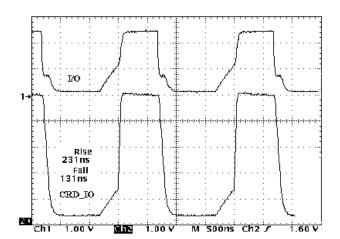

Figure 8. Typical I/O Rise and Fall Time

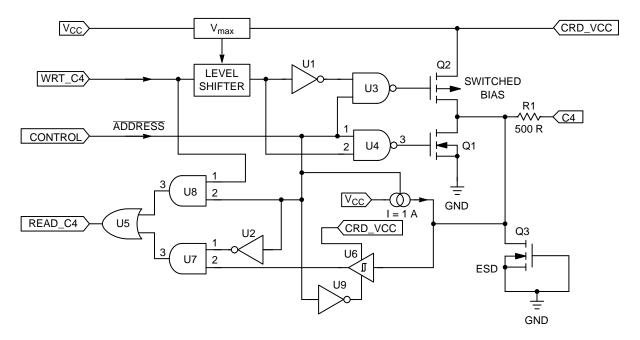

#### **GENERAL PURPOSE CRD C4 AND CRD C8**

These two pins can be used as a logic input to define the address of a given interface (in the range \$00 to \$11), or as a standard C4/C8 access to the smart card's channels. Since

these pins can be directly connected to the V<sub>CC</sub> power supply, both output stages are built with switched NMOS/PMOS totem pole as depicted in Figure 9.

Figure 9. Typical CRD\_C4 Output Drive and Logic Control

The C4 and C8 pins are biased by an internal current source to provide a logic one when the pin is left open. In this case, care must be observed to avoid relative low impedance to ground to make sure the pin is at a High logic level. However, it is possible to connect the pin to  $V_{CC}$  (battery supply) to force the logic input to a High level, regardless of the input bias. Thanks to the CONTROL internal signal, the system automatically adapts the mode of operation (chip address or data communication) and, except the leakage, no extra current is drawn from the battery to bias these pins when the logic level is High.

When any of these pins is connected to GND, a continuous  $1~\mu A$  typical sink current will be absorbed from the battery supply.

The switched Totem Pole structure provides the fast positive going transient when the related pin is forced to the High state during a data transfer. In the event of a low impedance connected across C4 or C8 to ground, the current flow is limited to 15 mA, according to the ISO7816–3 specification.

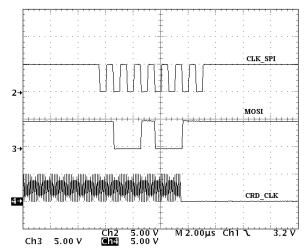

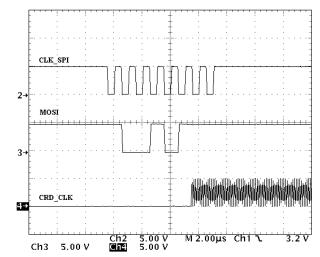

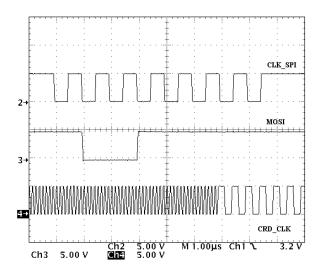

The two general purpose pins can transfer data from the external microcontroller to the card and read back the logic state, but none of these pins can read the data coming from the external smart card. On the other hand, both C4 and C8 can read input logic, hence the physical address of a given chip.