# P240FZ4QLA

# Power MOSFETs 40V, 240A, N-channel

#### **Feature**

- N-channel

- SMD

- Super Large Current

- · Low Ron

- 4.5V Gate Drive

- Low Capacitance

- Halogen free

- · Pb free terminal

- RoHS:Yes

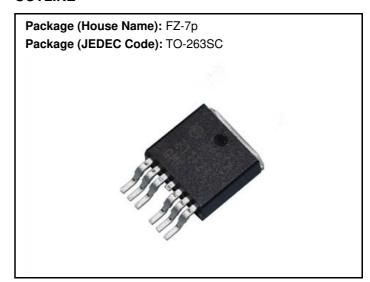

## **OUTLINE**

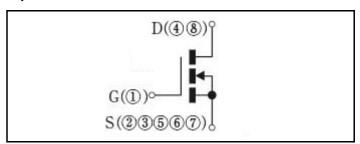

# **Equivalent circuit**

Absolute Maximum Ratings (unless otherwise specified : Tc=25°C)

| Item                           | Symbol          | Conditions                   | Ratings    | Unit |

|--------------------------------|-----------------|------------------------------|------------|------|

| Storage temperature            | Tstg            |                              | -55 to 175 | °C   |

| Channel tempertature           | Tch             |                              | -55 to 175 | °C   |

| Drain-source voltage           | $V_{DSS}$       |                              | 40         | V    |

| Gate-source voltage            | $V_{GSS}$       |                              | ±20        | V    |

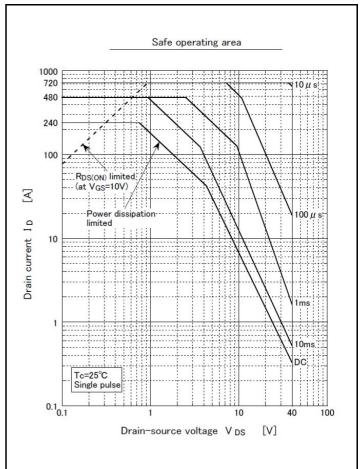

| Continuous drain current(DC)   | I <sub>D</sub>  |                              | 240        | Α    |

| Continuous drain current(Peak) | I <sub>DP</sub> | Pulse width 10µs, duty=1/100 | 720        | Α    |

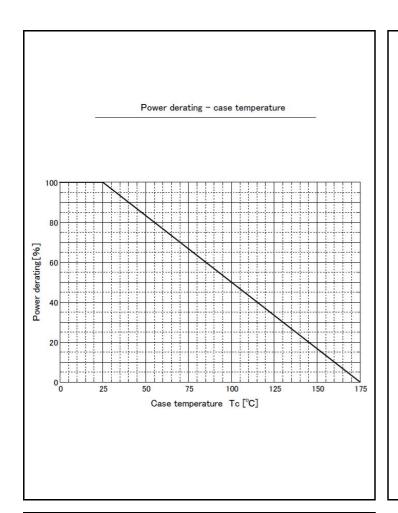

| Total power dissipation        | P <sub>T</sub>  |                              | 178        | W    |

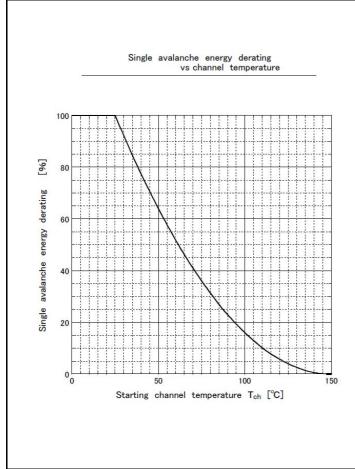

| Single avalanche current       | I <sub>AS</sub> | Starting Tch=25°C Tch≦150°C  | 80         | Α    |

| Single avalanche energy        | E <sub>AS</sub> | Starting Tch=25°C Tch≦150°C  | 320        | mJ   |

<sup>\* :</sup>See the original Specifications

# **Electrical Characteristics** (unless otherwise specified : Tc=25°C)

| Item                                    | Symbol               | Conditions                                                                |     | Ratings |         |      |

|-----------------------------------------|----------------------|---------------------------------------------------------------------------|-----|---------|---------|------|

|                                         |                      |                                                                           | MIN | TYP     | MAX     | Unit |

| Drain-Source breakdown voltage          | V <sub>(BR)DSS</sub> | ID=1mA, VGS=0V                                                            | 40  |         |         | V    |

| Zero gate voltage drain current         | I <sub>DSS</sub>     | VDS=40V, VGS=0V                                                           |     |         | 1       | μΑ   |

| Gate-source leakage current             | I <sub>GSS</sub>     | VGS=±20V, VDS=0V                                                          |     |         | ±0.1    | μΑ   |

| Forward transconductance                | 9fs                  | ID=60A, VDS=10V                                                           | 40  |         |         | S    |

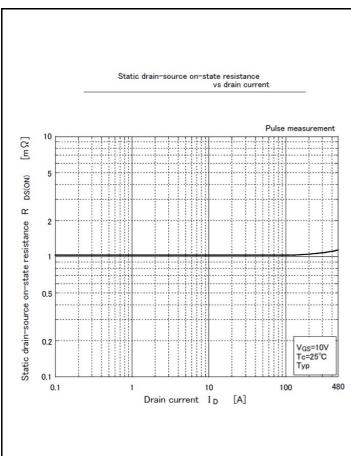

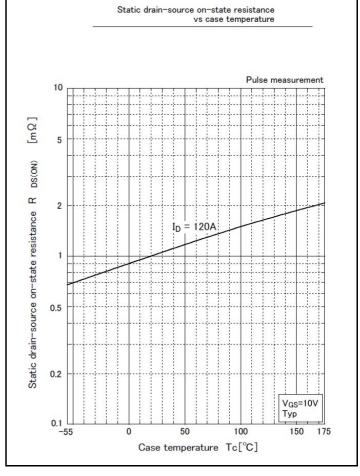

| Static drain-source on-state resistance | R <sub>DS(ON)</sub>  | ID=120A, VGS=10V                                                          |     | 0.00103 | 0.00129 | Ω    |

| Static drain-source on-state resistance | R <sub>DS(ON)</sub>  | ID=120A, VGS=4.5V                                                         |     | 0.00147 | 0.00196 | Ω    |

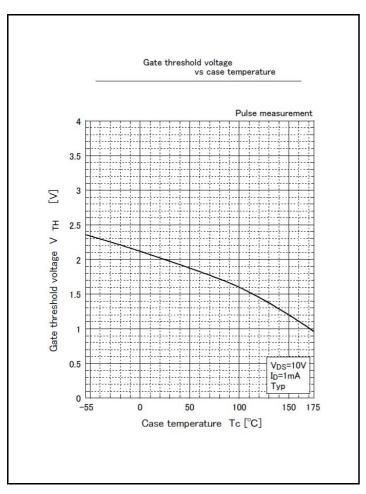

| Gate threshold voltage                  | Vth                  | ID=1mA, VDS=10V                                                           | 1.5 | 2       | 2.5     | V    |

| Source-drain diode forward voltage      | $V_{SD}$             | IS=120A, VGS=0V                                                           |     |         | 1.5     | V    |

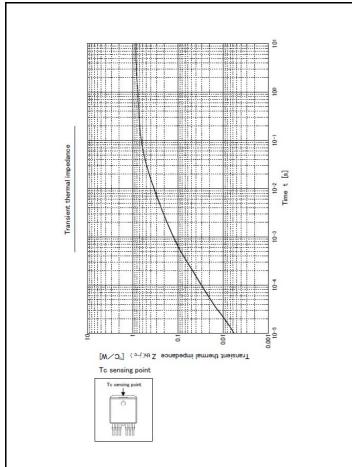

| Thermal resistance                      | Rth(j-c)             | Junction to case, with heatsink                                           |     |         | 0.84    | °C/W |

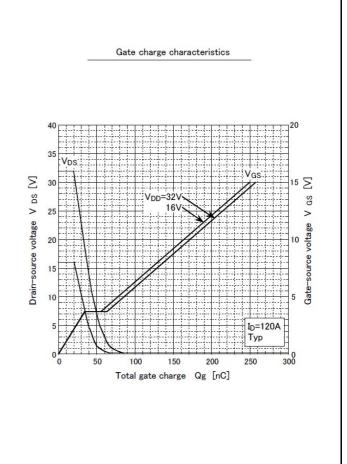

| Total gate charge                       | Qg                   | VDD=32V, VGS=10V, ID=120A                                                 |     | 171     |         | nC   |

| Gate to source charge                   | Qgs                  | VDD=32V, VGS=10V, ID=120A                                                 |     | 32      |         | nC   |

| Gate to drain charge                    | Qgd                  | VDD=32V, VGS=10V, ID=120A                                                 |     | 43      |         | nC   |

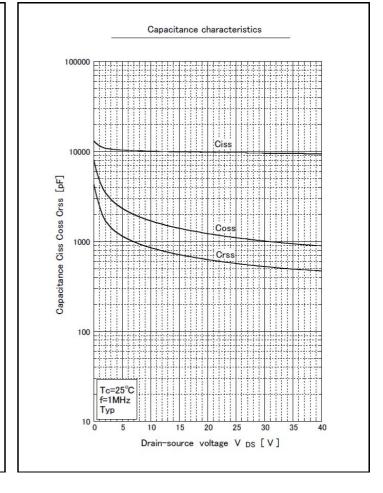

| Input capacitance                       | Ciss                 | VDS=25V, VGS=0V, f=1MHz                                                   |     | 9675    |         | pF   |

| Reverce transfer capacitnce             | Crss                 | VDS=25V, VGS=0V, f=1MHz                                                   |     | 570     |         | pF   |

| Output capacitance                      | Coss                 | VDS=25V, VGS=0V, f=1MHz                                                   |     | 1102    |         | pF   |

| Turn-on delay time                      | td(on)               | ID=50A, RL=0.40 $\Omega$ , VDD=20V, Rg=0 $\Omega$ , VGS(+)=10V, VGS(-)=0V |     | 13.5    |         | ns   |

| Rise time                               | tr                   | ID=50A, RL=0.40Ω, VDD=20V, Rg=0Ω, VGS(+)=10V, VGS(-)=0V                   |     | 32      |         | ns   |

| Turn-off delay time                     | td(off)              | ID=50A, RL=0.40Ω, VDD=20V, Rg=0Ω, VGS(+)=10V, VGS(-)=0V                   |     | 152     |         | ns   |

| Fall time                               | tf                   | ID=50A, RL=0.40Ω, VDD=20V, Rg=0Ω, VGS(+)=10V, VGS(-)=0V                   |     | 47      |         | ns   |

| Diode reverse recovery time             | trr                  | IF=120A, VGS=0V, di/dt=100A/μs                                            |     | 47      |         | ns   |

| Diode reverse recovery charge           | Qrr                  | IF=120A, VGS=0V, di/dt=100A/μs                                            |     | 60      |         | nC   |

<sup>\*</sup> :See the original Specifications

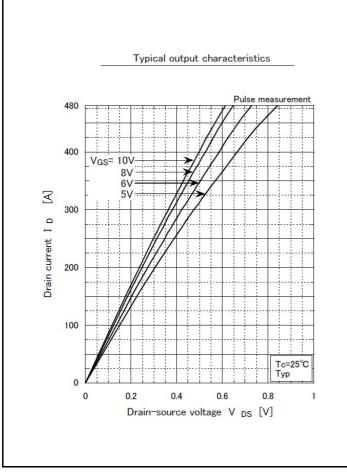

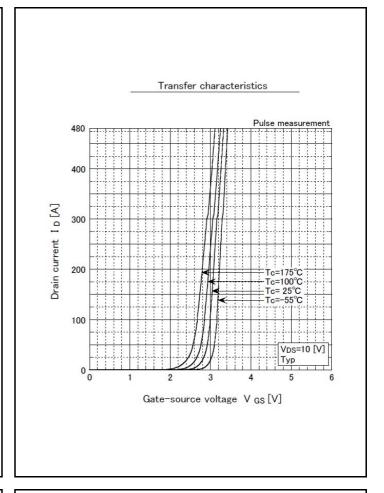

# **CHARACTERISTIC DIAGRAMS**

**H7**

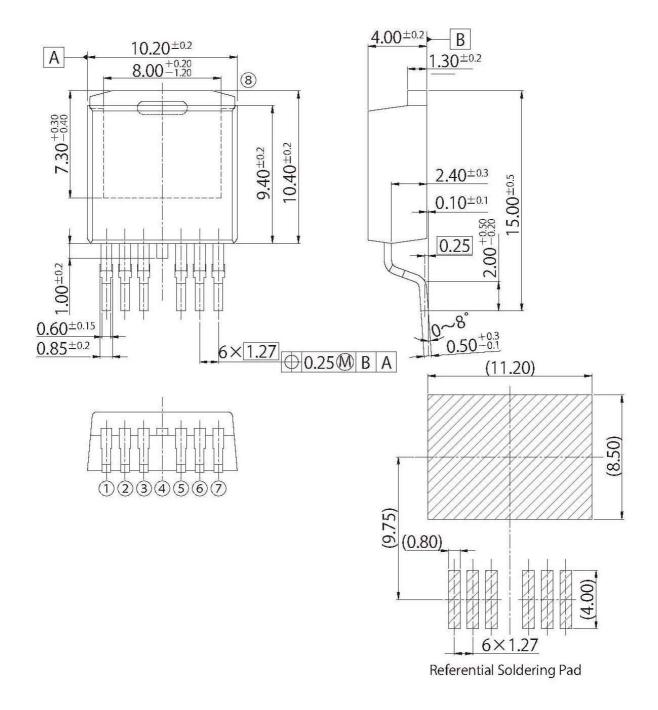

| JEDEC Code | TO-263SC |  |

|------------|----------|--|

| JEITA Code | —        |  |

| House Name | FZ-7p    |  |

<sup>•</sup> Optimize soldering pad to the board design and soldering condition

#### **Notes**

- 1. If you wish to use any such product, please be sure to refer to the specifications issued by Shindengen.

- 2. All products described or contained herein are designed with a quality level intended for use in standard applications requiring an ordinary level of reliability. If these products are to be used in equipment or devices for special or specific applications requiring an extremely high grade of quality or reliability in which failures or malfunctions of products may directly affect human life or health, a local Shindengen office must be contacted in advance to confirm that the intended use of the product is appropriate. Shindengen products are grouped into the following three applications according the quality grade.

#### (Standard applications)

Computers, office automation and other office equipment, communication terminals, test and measurement equipment, audio/visual equipment, amusement equipment, consumer electronics, machine tools, personal electronic equipment, industrial equipment, etc.

### [Special applications]

Transportation equipment (vehicles, ships, etc.), trunk-line communication equipment, traffic signal control systems, antidisaster/crime systems, safety equipment, medical equipment, etc.

#### (Specific applications)

Nuclear reactor control systems, aircraft, aerospace equipment, submarine repeaters, life support equipment and systems, etc.

- 3. Although Shindengen continuously endeavors to enhance the quality and reliability of its products, customers are advised to consider and take safety measures in their design, such as redundancy, fire containment and anti-failure, so that personal injury, fires, or societal damages can be prevented.

- 4. Please note that all information described or contained herein is subject to change without notice due to product upgrades and other reasons. When buying Shindengen products, please contact the Company's offices or distributors to obtain the latest information.

- 5. Shindengen shall not bear any responsibility with regards to damages or infringement of any third-party patent rights and other intellectual property rights incurred due to the use of information on this website.

- 6. The information and materials on this website neither warrant the use of Shindengen's or any third party's patent rights and other intellectual property rights, nor grant license to such rights.

- 7. In the event that any product described or contained herein falls under the category of strategic products controlled under the Foreign Exchange and Foreign Trade Control Law of Japan, exporting of such products shall require an export license from the Japanese government in accordance with the above law.

- 8. No reprinting or reproduction of the materials on this website, either in whole or in part, is permitted without proper authorization from Shindengen.