**TCA5013**

SCPS253C - JANUARY 2014-REVISED SEPTEMBER 2019

# TCA5013 Feature Rich Smartcard Interface IC with 1 User Card and 3 SAM Card Support

#### **Features**

- Operating supply voltage range of 2.7 V to 5.5 V

- Supports EMV 4.3, ISO7816-3 and ISO7816-10 standards

- Supports 1 user card and 3 secure access module

- IEC61000-4-2 8-kV Contact discharge esd protection on all smartcard interface pins

- Low power mode for power saving when inactive (shutdown mode)

- Automatic card deactivation in the event of short circuit, card pull out, over temperature or power supply fault

- Integrated DC-DC boost to generate V<sub>CC</sub> for 5 V and 3 V on all card interfaces

- Automatic card clock generation for synchronous card activation

- 4-byte FIFO for storing ATR from ISO7816-10 Type 1 cards

- Programmable rise/fall time control for IO and clock lines of all smartcards

- Input clock frequency up to 26 MHz

- Tamper proof package design

## **Applications**

- High-end point of sale (POS) terminals

- Multi secure accesscard capable EPOS systems

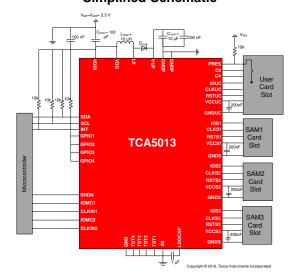

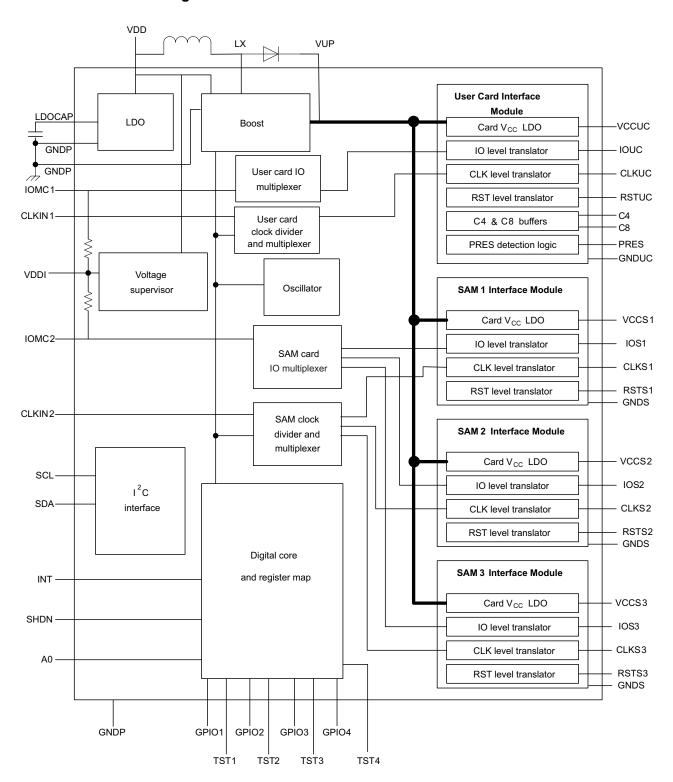

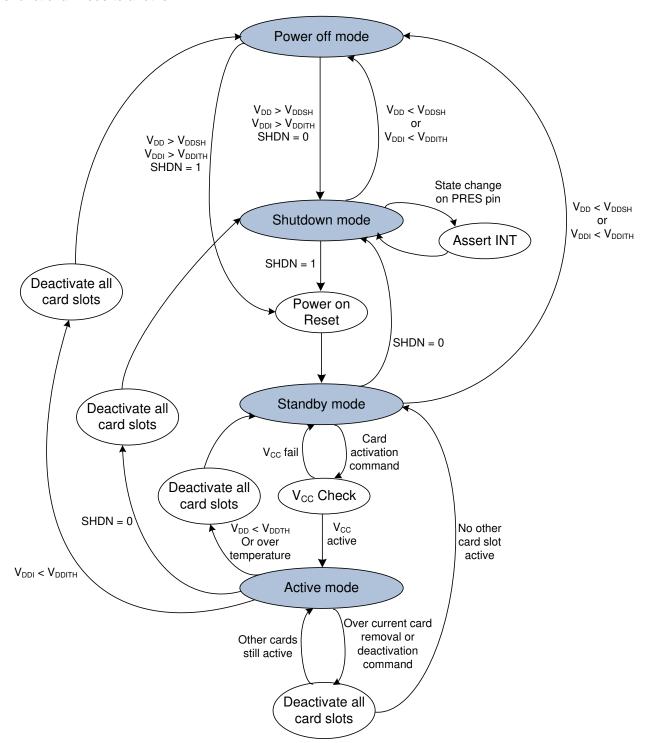

### 3 Description

TCA5013 is a smartcard interface IC that is targeted for use in Point of Sale (POS) terminals. The device enables POS terminals to interface with EMV4.3, ISO7816-3 and ISO7816-10 compliant cards. It supports up to 3 Secure Access Module (SAM) cards in addition to 1 user card. It operates from a single supply and generates all the card voltages. The device is controlled by a standard I2C interface and is capable of card activation and deactivation per EMV4.3 and ISO7816-3 standards. In addition it also supports ISO7816-10 synchronous cards. It has a 4byte FIFO that stores the ATR (Answer to Reset) sequence in ISO7816-10 type 1 cards. Synchronous cards (ISO7816-10 type 1 and type 2) can be set up for automatic activation or manual activation. The device has multiple power saving modes and also supports power saving in the smartcard itself by "clock stop" or lowering clock frequency to lowest allowable levels per the ISO7816 - 3 standard. TCA5013 has IEC 61000-4-2 8kV contact discharge on all pins that interface with smartcards. This enables the system to be resistant to ESD in the field without the need for external ESD devices. It is available in an 5 mm x 5 mm BGA package. The pin out of the device is such that all the IO pins are securely surrounded by other pins. This prevents the secure pins from being probed during device operation.

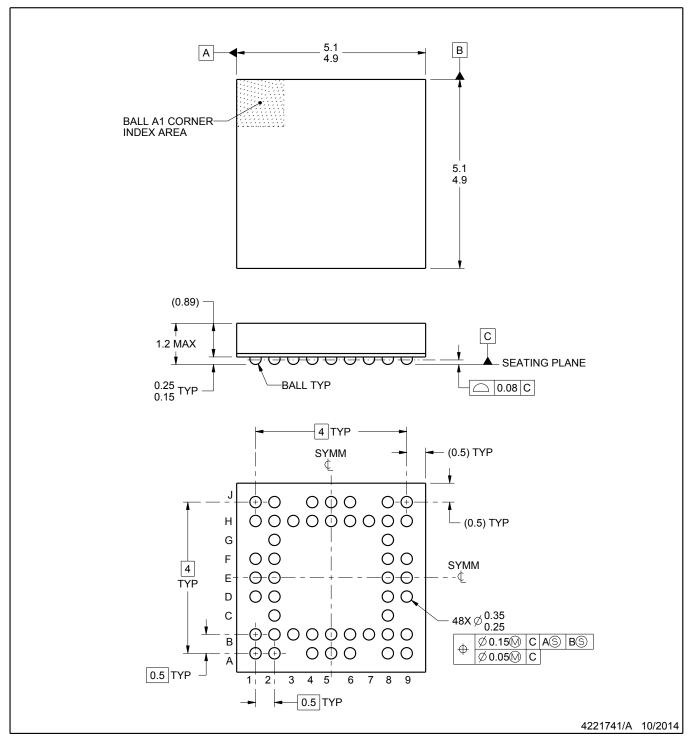

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TCA5013     | NFBGA (48) | 5.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

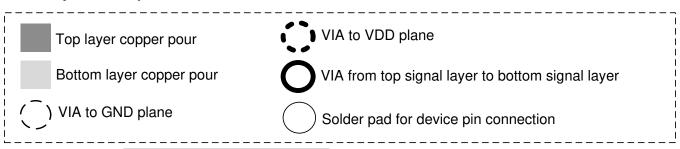

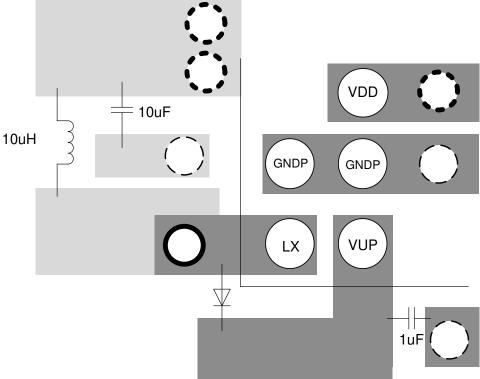

### **Simplified Schematic**

## **Table of Contents**

| 1   | Features 1                                               |    | Characteristics                                  | 11   |

|-----|----------------------------------------------------------|----|--------------------------------------------------|------|

| 2   | Applications 1                                           |    | 6.21 Synchronous Type 2 Card Activation Timing   |      |

| 3   | Description 1                                            |    | Characteristics                                  |      |

| 4   | Revision History2                                        |    | 6.22 Card Deactivation Timing Characteristics    |      |

| 5   | Pin Configuration and Functions3                         | _  | 6.23 Typical Characteristics                     |      |

| 6   | Specifications5                                          | 7  | Parameter Measurement Information                |      |

| •   | 6.1 Absolute Maximum Ratings 5                           | 8  | Detailed Description                             |      |

|     | 6.2 Handling Ratings                                     |    | 8.1 Overview                                     |      |

|     | 6.3 Recommended Operating Conditions                     |    | 8.2 Functional Block Diagram                     |      |

|     | 6.4 Thermal Information                                  |    | 8.3 Feature Description                          |      |

|     | 6.5 Electrical Characteristics—Power Supply and ESD . 6  |    | 8.4 Device Functional Modes                      |      |

|     | 6.6 Electrical Characteristics—Card V <sub>CC</sub>      |    | 8.5 Programming                                  |      |

|     | 6.7 Electrical Characteristics—Card RST                  |    | 8.6 Register Maps                                | 41   |

|     | 6.8 Electrical Characteristics—Card CLK                  | 9  | Application and Implementation                   | 55   |

|     | 6.9 Electrical Characteristics—Card Interface IO, C4 and |    | 9.1 Application Information                      | 55   |

|     | C8                                                       |    | 9.2 Typical Application                          | 55   |

|     | 6.10 Electrical Characteristics—PRES 8                   | 10 | Power Supply Recommendations                     | 57   |

|     | 6.11 Electrical Characteristics—IOMC1 and IOMC2 9        |    | 10.1 Power-On-Reset                              |      |

|     | 6.12 Electrical Characteristics—CLKIN1 and CLKIN2 9      | 11 | Layout                                           | 57   |

|     | 6.13 Electrical Characteristics—A0 and SHDN              |    | 11.1 Layout Guidelines                           |      |

|     | 6.14 Electrical Characteristics—INT                      |    | 11.2 Layout Example                              |      |

|     | 6.15 Electrical Characteristics—GPIO                     | 12 | Device and Documentation Support                 |      |

|     | 6.16 Electrical Characteristics—SDA and SCL              | 12 | 12.1 Trademarks                                  |      |

|     | 6.17 Electrical Characteristics—SDA and SCE              |    | 12.2 Electrostatic Discharge Caution             |      |

|     | Detection                                                |    | 12.3 Glossary                                    |      |

|     | 6.18 I <sup>2</sup> C Interface Timing Requirements      | 42 | · · · · · · · · · · · · · · · · · · ·            | 59   |

|     | 6.19 I <sup>2</sup> C Interface Timing Characteristics   | 13 | Mechanical, Packaging, and Orderable Information | 50   |

|     | 6.20 Synchronous Type 1 Card Activation Timing           |    | illorination                                     | 59   |

|     | 0.20 Synchronous Type I Card Activation Filming          |    |                                                  |      |

| F   | Revision History                                         |    |                                                  |      |

| nan | ges from Revision B (January 2016) to Revision C         |    |                                                  | Page |

| С   | hanged the Pin Configuration view                        |    |                                                  | 3    |

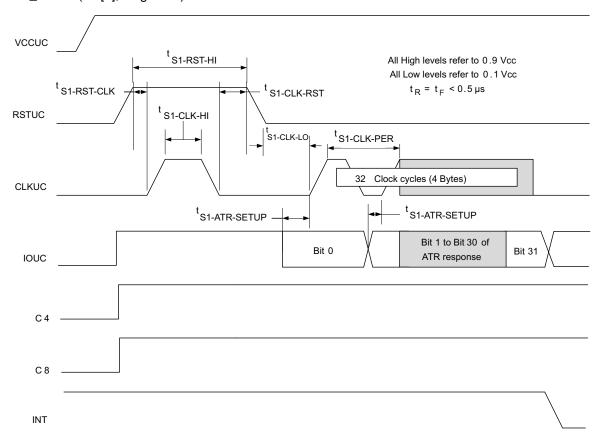

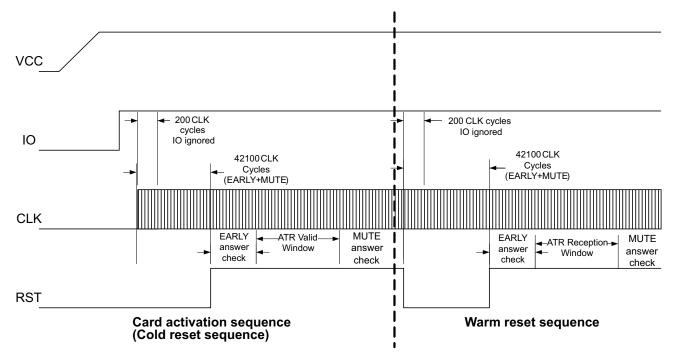

| Α   | dded: (Cold reset sequence) to Figure 6                  |    |                                                  | 22   |

|     |                                                          |    |                                                  |      |

| nan | ges from Revision A (July 2014) to Revision B            |    |                                                  | Page |

|     | hanged the datasheet title to "TCA5013 Feature Rich Sma  |    |                                                  | 1    |

| Α   | dded the Features: Tamper proof package design           |    |                                                  | 1    |

|     | hanged the Applications                                  |    |                                                  |      |

|     | ull Version release of document                          |    |                                                  |      |

| •   |                                                          |    |                                                  |      |

|     |                                                          |    |                                                  |      |

Submit Documentation Feedback

Changes from Original (July 2014) to Revision A

Copyright © 2014–2019, Texas Instruments Incorporated

**Page**

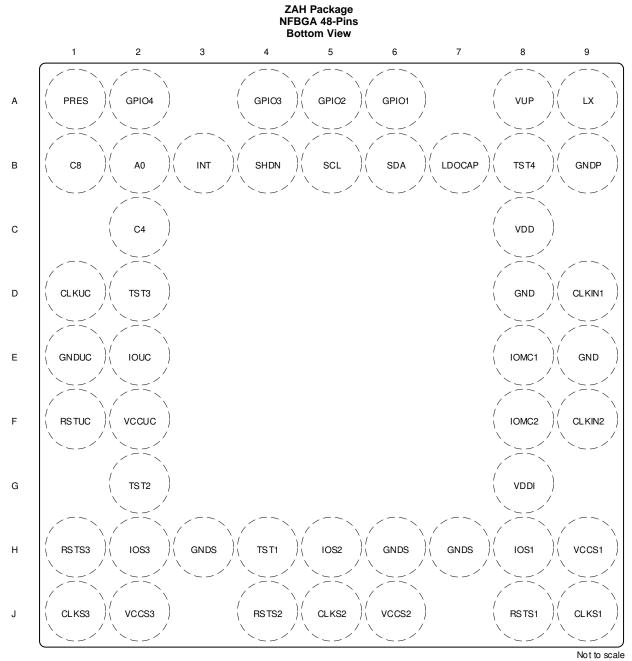

# 5 Pin Configuration and Functions

NOT to scale

### **Pin Functions**

|     | Pin Functions |            |                                                               |  |  |  |

|-----|---------------|------------|---------------------------------------------------------------|--|--|--|

| NO. | NAME          | TYPE       | DESCRIPTION                                                   |  |  |  |

| A1  | PRES          | INPUT      | User card presence detection                                  |  |  |  |

| A2  | GPIO4         | I/O        | General purpose IO (5-V tolerant)                             |  |  |  |

| A4  | GPIO3         | I/O        | General purpose IO (5-V tolerant)                             |  |  |  |

| A5  | GPIO2         | I/O        | General purpose IO (5-V tolerant)                             |  |  |  |

| A6  | GPIO1         | I/O        | General purpose IO (5-V tolerant)                             |  |  |  |

| A8  | VUP           | PWR        | Boost output terminal                                         |  |  |  |

| A9  | LX            | PWR        | Boost inductor input terminal                                 |  |  |  |

| B1  | C8            | I/O        | User card auxiliary IO (Open Drain)                           |  |  |  |

| B2  | A0            | INPUT      | I <sup>2</sup> C address selection pin. Connect to VDDI, GND. |  |  |  |

| В3  | INT           | OUTPUT     | Interrupt output (open drain)                                 |  |  |  |

| B4  | SHDN          | INPUT      | Shutdown and reset pin                                        |  |  |  |

| B5  | SCL           | INPUT      | I <sup>2</sup> C clock input                                  |  |  |  |

| B6  | SDA           | I/O        | I <sup>2</sup> C data                                         |  |  |  |

| B7  | LDOCAP        | PWR        | Internal LDO output. Connect to 1 µf decoupling capacitor.    |  |  |  |

| B8  | TST4          | NA         | Test pin. Grounded in application.                            |  |  |  |

| B9  | GNDP          | PWR        | Power ground                                                  |  |  |  |

| C2  | C4            | I/O        | User card auxiliary IO (Open drain)                           |  |  |  |

| C8  | VDD           | PWR        | Device main power supply                                      |  |  |  |

| D1  | CLKUC         | OUTPUT     | User card clock                                               |  |  |  |

| D2  | TST3          | NA NA      | Test pin. Grounded in application.                            |  |  |  |

| D8  | GND           | PWR        | + '                                                           |  |  |  |

| D9  | CLKIN1        | INPUT      | Device ground                                                 |  |  |  |

|     |               |            | User card external clock input pin                            |  |  |  |

| E1  | GNDUC         | PWR        | User card ground pin                                          |  |  |  |

| E2  | IOUC          | I/O        | User card IO pin                                              |  |  |  |

| E8  | IOMC1         | I/O        | User card microcontroller data IO                             |  |  |  |

| E9  | GND           | PWR        | Device ground                                                 |  |  |  |

| F1  | RSTUC         | OUTPUT     | User card reset output pin                                    |  |  |  |

| F2  | VCCUC         | PWR        | User card VCC pin                                             |  |  |  |

| F8  | IOMC2         | I/O        | SAM microcontroller data IO                                   |  |  |  |

| F9  | CLKIN2        | INPUT      | User card external clock input pin                            |  |  |  |

| G2  | TST2          | NA         | Test pin. Grounded in application.                            |  |  |  |

| G8  | VDDI          | PWR        | Microcontroller interface supply voltage.                     |  |  |  |

| H1  | RSTS3         | OUTPUT     | Reset output for SAM3                                         |  |  |  |

| H2  | IOS3          | I/O        | IO pin for SAM3                                               |  |  |  |

| H3  | GNDS<br>TST1  | PWR        | Ground for all SAMs  Test pip Grounded in application         |  |  |  |

| H4  | TST1          | NA<br>I/O  | Test pin. Grounded in application                             |  |  |  |

| H5  | IOS2          | I/O<br>DMP | IO pin for SAM2                                               |  |  |  |

| H6  | GNDS          | PWR        | Ground for all SAMs                                           |  |  |  |

| H7  | GNDS          | PWR        | Ground for all SAMs                                           |  |  |  |

| H8  | IOS1          | I/O        | IO pin for SAM1                                               |  |  |  |

| H9  | VCCS1         | PWR        | VCC for SAM1                                                  |  |  |  |

| J1  | CLKS3         | OUTPUT     | Clock output for SAM3                                         |  |  |  |

| J2  | VCCS3         | PWR        | VCC for SAM3                                                  |  |  |  |

| J4  | RSTS2         | OUTPUT     | Reset output for SAM2                                         |  |  |  |

| J5  | CLKS2         | OUTPUT     | Clock output for SAM2                                         |  |  |  |

| J6  | VCCS2         | PWR        | VCC for SAM2                                                  |  |  |  |

| J8  | RSTS1         | OUTPUT     | Reset output for SAM1                                         |  |  |  |

| J9  | CLKS1         | OUTPUT     | Clock output for SAM1                                         |  |  |  |

### 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted) (3)

|                |                                                                        | MIN  | MAX                    | UNIT |

|----------------|------------------------------------------------------------------------|------|------------------------|------|

| $V_{DD}$       | Supply voltage range                                                   | -0.3 | 6                      | V    |

| $V_{DDI}$      | Interface voltage range                                                | -0.3 | 4                      | V    |

|                | Input voltage range on digital I/O pins referenced to V <sub>DDI</sub> | -0.3 | V <sub>DDI</sub> + 0.3 | V    |

| V <sub>I</sub> | Input voltage range on digital I/O pins referenced to V <sub>CC</sub>  | -0.3 | V <sub>CC</sub> + 0.3  | V    |

|                | Load current on GPIO pins                                              | -15  |                        | mA   |

| IOL            | Load current on INT and SDA pins                                       | -6   |                        | mA   |

<sup>(1)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

(2) The package thermal impedance is calculated in accordance with JESD 51-7.

### 6.2 Handling Ratings

|                  |                                                                             |                                                                               | MIN  | MAX | UNIT |

|------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub> | Storage temperature rang                                                    | Storage temperature range                                                     |      |     |      |

| N 51 1 1 5 1 1   | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | -4                                                                            | 4    | 147 |      |

| V(ESD)           | V <sub>(ESD)</sub> Electrostatic discharge                                  | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -1.5 | 1.5 | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                                            | MIN  | MAX | UNIT |

|----------------------|------------------------------------------------------------|------|-----|------|

| V <sub>DD</sub>      | Supply voltage range – DC-DC enabled                       | 2.7  | 5.5 | V    |

|                      | Supply voltage Range – DC-DC disabled                      | 5.25 | 5.5 | V    |

| $V_{DDI}$            | Interface voltage range                                    | 1.65 | 3.6 | V    |

| I <sub>CC(TOT)</sub> | Sum of the currents that can be drawn on all Card VCC pins |      | 180 | mA   |

| T <sub>A</sub>       | Operating temperature range                                | -40  | 85  | °C   |

### 6.4 Thermal Information

|                      |                                              | TCA5013 |      |

|----------------------|----------------------------------------------|---------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | ZAH     | UNIT |

|                      |                                              | 48 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 96.9    |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 59.0    |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 49.4    | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.9     |      |

| ΨЈВ                  | Junction-to-board characterization parameter | 58.6    |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(3)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.5 Electrical Characteristics—Power Supply and ESD

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \mu\text{H}$ ;  $C_{VDD} = 10 \mu\text{F}$ ;  $C_{VUP} = 10 \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

|                       | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                                                                                                                     | MIN  | TYP | MAX | UNIT |

|-----------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

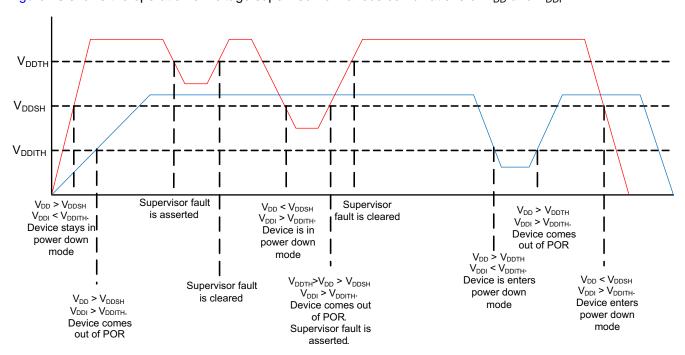

| $V_{DDTH}$            | VDD supervisor fault threshold                                 | V <sub>DD</sub> voltage below which SUPL fault is asserted                                                                                                                                                                                          | 2.45 |     | 2.7 | V    |

| $V_{DDSH}$            | VDD shutdown threshold                                         | V <sub>DD</sub> voltage below which device will shutdown                                                                                                                                                                                            |      |     | 2.0 | V    |

| $V_{DDITH}$           | VDDI shutdown threshold                                        | V <sub>DDI</sub> voltage below which device will shutdown                                                                                                                                                                                           | 1.4  |     | 1.6 | V    |

| I <sub>DDSH</sub>     | VDD Shutdown current                                           | Shutdown Mode at T <sub>ambient</sub> = 25 C                                                                                                                                                                                                        |      | 22  | 28  | μA   |

| I <sub>DDST</sub>     | VDD Standby current                                            | Shutdown Mode at T <sub>ambient</sub> = 25°C                                                                                                                                                                                                        |      | 300 | 650 | μΑ   |

| I <sub>DDA</sub>      |                                                                | IOMC1 = IOMC2 = V <sub>DDi</sub> ;<br>CLKIN1 = CLKIN2 = GND; T <sub>ambient</sub> = 25°C<br>Current consumption per card interface activated                                                                                                        |      |     | 2   | mA   |

| I <sub>DDA1</sub> (1) | Supply current                                                 | $\begin{split} &V_{CCUC}=V_{CCS1}=V_{CCS2}=V_{CCS3}=5 \text{ V;} \\ &f_{CLKIN1}=f_{CLKIN2}=f_{CLKUC}=f_{CLKS1}=5 \text{ MHz;} \\ &I_{CCUC}=I_{CCS1}=55 \text{ mA; } I_{CCS2}=I_{CCS3}=2 \text{ mA;} \\ &T_{ambient}=25^{\circ}\text{C} \end{split}$ |      | 235 | 280 | mA   |

| I <sub>DDISH</sub>    | VDD Interface shutdown current                                 | Shutdown Mode at 25°C                                                                                                                                                                                                                               |      | 3.5 | 5   | μA   |

| I <sub>DDIA</sub>     | VDD Interface supply current                                   | All Card $V_{CC} = 5 \text{ V}$ ; CLKIN1 = CLKIN2 = 5 MHz; @ 25°C; IOMC1 = IOMC2 = $V_{DDI}$                                                                                                                                                        |      | 290 | 300 | μΑ   |

| t <sub>WAKE</sub>     | Device wakeup time                                             | Time from SHDN > V <sub>IH</sub> to INT < V <sub>OL</sub>                                                                                                                                                                                           | 0.1  |     | 10  | ms   |

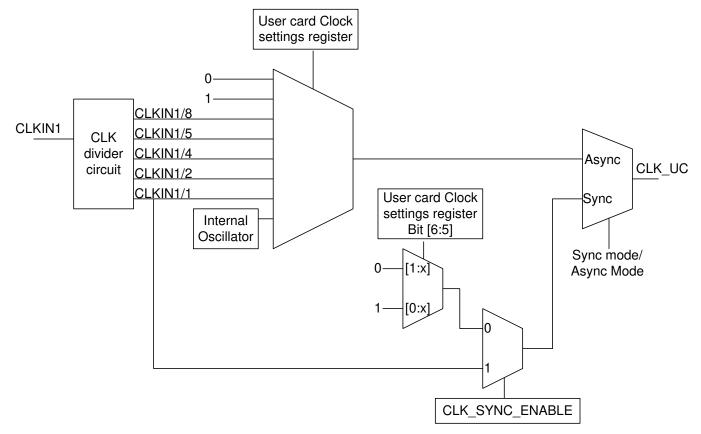

| f <sub>OSC</sub>      | Internal Oscillator Frequency                                  | Measured on CLKUC, CLKS1,CLKS2,CLKS3                                                                                                                                                                                                                | 1    | 1.2 | 1.4 | MHz  |

| f <sub>DC-DC</sub>    | DC-DC switching frequency                                      |                                                                                                                                                                                                                                                     |      | 2.4 |     | MHz  |

| V                     | DC-DC output voltage                                           | If any card V <sub>CC</sub> is 5 V                                                                                                                                                                                                                  |      | 5.5 |     | V    |

| V <sub>DC-DC</sub>    | DC-DC output voitage                                           | If all card V <sub>CC</sub> is 3 V or 1.8 V                                                                                                                                                                                                         |      | 3.5 |     | V    |

| V <sub>ESD-IEC</sub>  | IEC61000-4-2 level 4 ESD protection on pins defined in Table 1 |                                                                                                                                                                                                                                                     | -8   |     | 8   | kV   |

<sup>(1)</sup> Values highly dependent on external components like boost inductor and external rectifier. The specification is based on 75% boost efficiency for max value and 85% efficiency for typical value

### 6.6 Electrical Characteristics—Card V<sub>cc</sub>

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \mu\text{H}$ ;  $C_{VDD} = 10 \mu\text{F}$ ;  $C_{VUP} = 10 \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

| PARAMETER                     |                                                               |                                                  | TEST CONDITIONS                                  | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|---------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|------|------|------|

|                               |                                                               |                                                  | V <sub>CC</sub> = 5 V; I <sub>CC</sub> ≤ 65 mA   | 4.75 | 5    | 5.25 |      |

| $V_{CC}$                      | Card supply voltage                                           |                                                  | V <sub>CC</sub> = 3 V; I <sub>CC</sub> ≤ 65 mA   | 2.85 | 3    | 3.15 | V    |

|                               |                                                               | V <sub>CC</sub> = 1.8 V; I <sub>CC</sub> ≤ 45 mA | 1.71                                             | 1.8  | 1.89 |      |      |

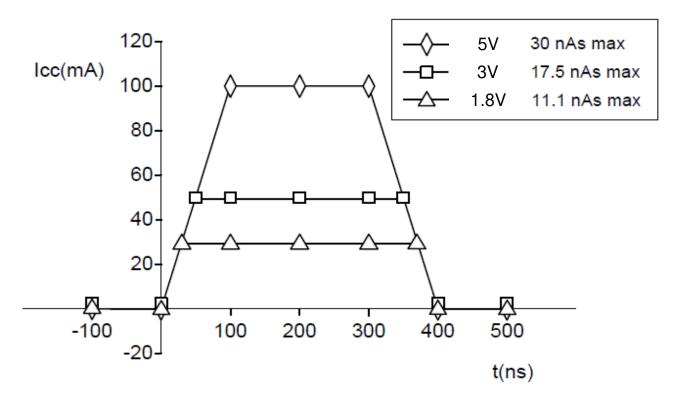

|                               | Load transient response Current pulses I < 100 mA, t < 400 ns |                                                  | V <sub>CC</sub> = 5 V ; 40 nA.s current spike    | 4.65 |      | 5.35 | V    |

| $\Delta V_{CC}/\Delta I_{CC}$ |                                                               | V <sub>CC</sub> = 3 V ; 17.5 nA.s current spike  | 2.76                                             |      | 3.24 | V    |      |

|                               |                                                               |                                                  | V <sub>CC</sub> = 1.8 V; 11.1 nA.s current spike | 1.62 |      | 1.98 | V    |

| V <sub>RIPPLE</sub>           | Peak to peak ripple voltage                                   | )                                                | Measured on V <sub>CC</sub> = 5 V, 3 V, 1.8 V    |      |      | 90   | mV   |

|                               |                                                               |                                                  | V <sub>CC</sub> = 5 V                            |      |      | 65   |      |

| $I_{CC}$                      | Card supply Current                                           |                                                  | V <sub>CC</sub> = 3 V                            |      |      | 65   | mA   |

|                               |                                                               |                                                  | V <sub>CC</sub> = 1.8 V                          |      |      | 45   |      |

| V <sub>DO</sub>               | Card LDO dropout voltage                                      |                                                  | I <sub>CC</sub> = 65 mA                          |      |      | 250  | mV   |

### 6.7 Electrical Characteristics—Card RST

$V_{DD} = V_{DDI} = 3.3 \text{ V; } L_{VDD} = 10 \text{ } \mu\text{H; } C_{VDD} = 10 \text{ } \mu\text{F; } C_{VUP} = 10 \text{ } \mu\text{F; } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise } T_{A} = -40 ^{\circ}\text{C} \text{$

|                       | PARAMETER           | TEST CONDITIONS                     | MIN                 | TYP | MAX                 | UNIT |

|-----------------------|---------------------|-------------------------------------|---------------------|-----|---------------------|------|

| V <sub>OL - RST</sub> | Output Low voltage  | I <sub>OL</sub> = -200 μA           |                     |     | 0.1 V <sub>CC</sub> | V    |

| V <sub>OH - RST</sub> | Output high voltage | I <sub>OH</sub> = 150 μA            | 0.9 V <sub>CC</sub> |     |                     | V    |

| t <sub>R - RST</sub>  | Rise time           | C <sub>L</sub> = 30 pF ; 10% to 90% |                     |     | 0.1                 | μs   |

| t <sub>F - RST</sub>  | Fall time           | C <sub>L</sub> = 30 pF ; 90% to 10% |                     |     | 0.1                 | μs   |

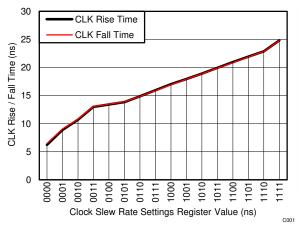

## 6.8 Electrical Characteristics—Card CLK

$V_{DD} = V_{DDI} = 3.3 \text{ V; } L_{VDD} = 10 \text{ } \mu\text{H; } C_{VDD} = 10 \text{ } \mu\text{F; } C_{VUP} = 10 \text{ } \mu\text{F; } T_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C unless otherwise noted}$

|                                             | PARAMETER                      |                                             | TEST CONDITIONS                             | MIN                 | TYP  | MAX                 | UNIT |

|---------------------------------------------|--------------------------------|---------------------------------------------|---------------------------------------------|---------------------|------|---------------------|------|

| V <sub>OL - CLK</sub>                       | Output Low voltage             | I <sub>OL</sub> = -100 μA                   |                                             |                     |      | 0.1 V <sub>CC</sub> | V    |

| V <sub>OH - CLK</sub>                       | Output high voltage            | I <sub>OH</sub> = 100 μA                    |                                             | 0.9 V <sub>CC</sub> |      |                     | V    |

|                                             |                                |                                             | CLK slew rate settings register = 0000b     |                     | 7    |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 0001b     |                     | 9    |                     |      |

|                                             |                                | CLK slew rate settings register = 0010b     |                                             | 11                  |      |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 0011b     |                     | 13   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 0100b     |                     | 13.5 |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 0101b     |                     | 14   |                     |      |

|                                             | Rise/Fall time                 | C <sub>L</sub> = 30 pF;<br>10% to 90%;      | CLK slew rate settings register = 0110b     |                     | 15   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 0111b     |                     | 16   |                     |      |

| t <sub>R</sub> - CLK / t <sub>F</sub> - CLK |                                |                                             | CLK slew rate settings register = 1000b     |                     | 17   |                     | ns   |

|                                             |                                |                                             | CLK slew rate settings register = 1001b     |                     | 18   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 1010b     |                     | 19   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 1011b     |                     | 20   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 1100b     |                     | 21   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 1101b     |                     | 22   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 1110b     |                     | 23   |                     |      |

|                                             |                                |                                             | CLK slew rate settings register = 1111b     |                     | 25   |                     |      |

| CLK <sub>PU-PD-SKEW</sub>                   | Clock pull-up / pull-down skew | t <sub>R-CLK</sub> - t <sub>F-CLK</sub> / t | t <sub>F-CLK</sub> ; C <sub>L</sub> = 30 pF |                     |      | 10                  | %    |

| f <sub>CLK</sub>                            | Frequency on CLK pin           | C <sub>L</sub> = 30 pF                      |                                             |                     |      | 20                  | MHz  |

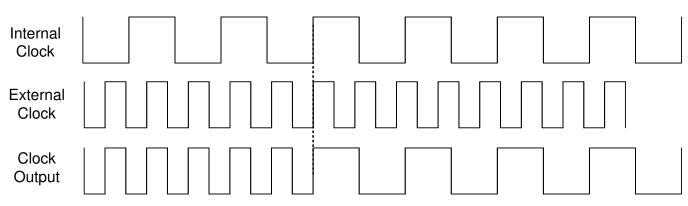

| D                                           | Clock duty cycle               | Internal clock =                            | 1.2 MHz; C <sub>L</sub> = 30 pF             | 45                  |      | 55                  | %    |

### 6.9 Electrical Characteristics—Card Interface IO, C4 and C8

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \mu\text{H}$ ;  $C_{VDD} = 10 \mu\text{F}$ ;  $C_{VUP} = 10 \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

| PARAMETER                    |                     | TEST CONDITIONS                                               | ;                       | MIN                 | TYP | MAX                 | UNIT |

|------------------------------|---------------------|---------------------------------------------------------------|-------------------------|---------------------|-----|---------------------|------|

| V <sub>OL - C4, C8</sub>     | Output Low Voltage  | V <sub>CC</sub> = 5 V                                         | I <sub>OL</sub> = -1 mA |                     |     | 0.5                 | V    |

| V <sub>OH - C4, C8</sub>     | Output Low Voltage  | V <sub>CC</sub> = 5 V, 3 V, 1.8 V                             | $I_{OH} = 20 \mu A$     | 0.9 V <sub>CC</sub> |     |                     | V    |

| V <sub>IL - IO, C4, C8</sub> | Output Low Voltage  |                                                               |                         |                     |     | 0.4 V <sub>CC</sub> | V    |

| V <sub>IH</sub> - IO, C4, C8 | Output High Voltage |                                                               |                         | 0.6 V <sub>CC</sub> |     |                     | V    |

|                              |                     | V <sub>CC</sub> = 5 V;<br>IO fall time register setting = 00b |                         |                     |     | 0.5                 |      |

| V                            | Outrot Law Valtage  | V <sub>CC</sub> = 5 V;<br>IO fall time register setting = 01b | 1 4 77 1                |                     |     | 0.5                 | V    |

| V <sub>OL</sub> - 10, 5 V    | Output Low Voltage  | V <sub>CC</sub> = 5 V;<br>IO fall time register setting = 10b | I <sub>OL</sub> = -1 mA |                     |     | 0.5                 | V    |

|                              |                     | V <sub>CC</sub> = 5 V;<br>IO fall time register setting = 11b |                         |                     |     | 0.5                 |      |

## Electrical Characteristics—Card Interface IO, C4 and C8 (continued)

$V_{DD} = V_{DDI} = 3.3 \text{ V}; L_{VDD} = 10 \text{ } \mu\text{H}; C_{VDD} = 10 \text{ } \mu\text{F}; C_{VUP} = 10 \text{ } \mu\text{F}; T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise noted}$

|                                    | RAMETER                        | TEST CONDITIONS                                                                                                                                                 |                              | MIN  | TYP | MAX  | UNIT |

|------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-----|------|------|

|                                    |                                | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 01b                                                                                                   |                              |      |     | 0.3  |      |

| V <sub>OL - IO, 3 V</sub>          | Output Low Voltage             | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 10b                                                                                                   | I <sub>OL</sub> = -1 mA      |      |     | 0.3  | V    |

|                                    |                                | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 11b                                                                                                   |                              |      |     | 0.3  |      |

|                                    |                                | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 00b                                                                                                   |                              |      |     | 0.3  |      |

| V                                  | Output Low Voltage             | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 01b                                                                                                   | I <sub>OL</sub> = -500       |      |     | 0.3  | V    |

| V <sub>OL</sub> - IO, 3 V, 500uA   | Output Low Voltage             | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 10b                                                                                                   | μĀ                           |      |     | 0.3  | V    |

|                                    |                                | V <sub>CC</sub> = 3 V;<br>IO fall time register setting = 11b                                                                                                   |                              |      |     | 0.3  |      |

| V <sub>OL - IO, 1.8 V</sub>        | Output Low Voltage             | V <sub>CC</sub> = 1.8 V;<br>IO fall time register setting = 11b                                                                                                 | I <sub>OL</sub> = -1 mA      |      |     | 0.18 | V    |

|                                    |                                | V <sub>CC</sub> = 1.8 V;<br>IO fall time register setting = 01b                                                                                                 |                              |      |     | 0.18 |      |

| V <sub>OL</sub> - IO, 1.8 V, 500uA | Output Low Voltage             | V <sub>CC</sub> = 1.8 V;<br>IO fall time register setting = 10b                                                                                                 | I <sub>OL</sub> = -500<br>μΑ | 0.18 |     | 0.18 | ٧    |

|                                    |                                | V <sub>CC</sub> = 1.8 V;<br>IO fall time register setting = 11b                                                                                                 |                              |      |     | 0.18 |      |

| t <sub>PD - R</sub> - IOMC - IO    | Rising edge propagation delay  | From IOMC pin to card IO; C <sub>L</sub> on card C <sub>L</sub> on IOMC = 30 pF; Prop delay meas 70% V <sub>DDI</sub> to 70% of V <sub>CC</sub> for rising edge | ured from                    |      |     | 400  | ns   |

| t <sub>PD - F - IOMC - IO</sub>    | Falling edge propagation delay | From IOMC pin to card IO; $C_L$ on card $C_L$ on IOMC = 30 pF; Prop delay meas 30% $V_{DDI}$ to 30% of $V_{CC}$ for falling edge                                | ured from                    |      |     | 250  | ns   |

| t <sub>FO - 10</sub>               | IO Line output fall time       | C <sub>L</sub> = 30 pF ; 10% to 90%; IO fall time re = 00b                                                                                                      | egister setting              |      | 68  |      | ns   |

| t <sub>RO - IO</sub>               | IO Line output rise time       | $C_L$ = 30 pF ; 10% to 90%; IO rise time setting = 100b                                                                                                         | register                     |      | 100 |      | ns   |

| t <sub>RO - C4, C8</sub>           | C4, C8 Line output rise time   | C <sub>L</sub> = 30 pF ; 10% to 90%                                                                                                                             |                              |      |     | 1.2  | μs   |

| t <sub>FO - C4, C8</sub>           | C4, C8 Line output fall time   | C <sub>L</sub> = 30 pF ; 90% to 10%                                                                                                                             |                              |      |     | 1.2  | μs   |

| t <sub>RI - IO, C4, C8</sub>       | IO, C4, C8 Input rise time     | 10% to 90%                                                                                                                                                      |                              |      |     | 1.2  | μs   |

| t <sub>FI</sub> - IO, C4, C8       | IO, C4, C8 Input fall time     | 90% to 10%                                                                                                                                                      |                              |      |     | 1.2  | μs   |

| C <sub>I - IO, C4, C8</sub>        | Input capacitance              | F = 1 MHz                                                                                                                                                       |                              |      |     | 10   | pF   |

| R <sub>PU</sub> - IO, C4, C8       | Pull-up resistance             | IO, C4, C8 pull-up to V <sub>CC</sub>                                                                                                                           |                              | 4.25 |     | 8.1  | kΩ   |

### 6.10 Electrical Characteristics—PRES

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \text{ } \mu\text{H}$ ;  $C_{VDD} = 10 \text{ } \mu\text{F}$ ;  $C_{VUP} = 10 \text{ } \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

| 100 1001 11 1, -VDD 10 11 11 1, -VDD 10 11 11 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                       |                                                                                    |                      |     |                               |      |  |

|---------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------|----------------------|-----|-------------------------------|------|--|

| PAR                                                                       | RAMETER               | TEST CONDITION                                                                     | MIN                  | TYP | MAX                           | UNIT |  |

| V <sub>IL - PRES</sub>                                                    | Input Low voltage     |                                                                                    |                      |     | $0.3~\mathrm{V}_\mathrm{DDI}$ | V    |  |

| V <sub>IH - PRES</sub>                                                    | Input high voltage    |                                                                                    | 0.7 V <sub>DDI</sub> |     |                               | V    |  |

| I <sub>LEAK - PRES</sub>                                                  | Input leakage current | Voltage on pin = V <sub>DDI</sub>                                                  |                      |     | 1                             | μΑ   |  |

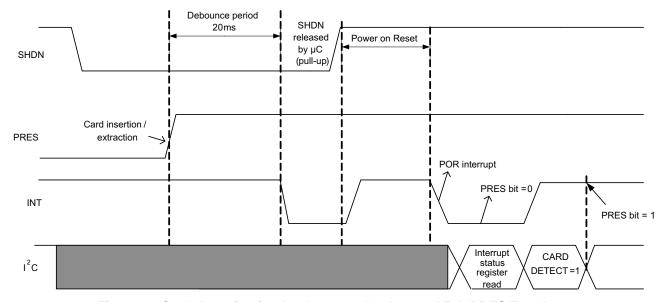

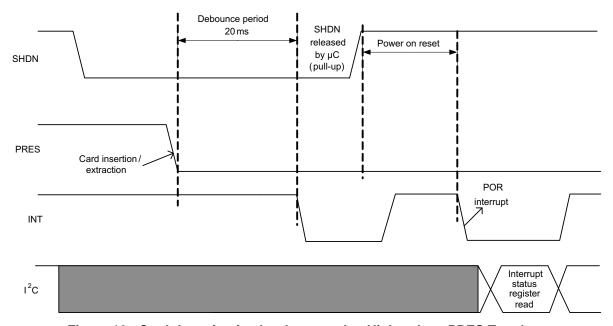

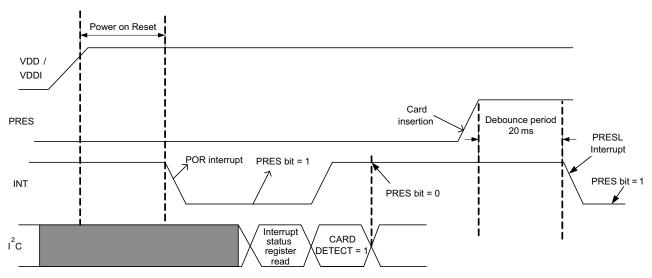

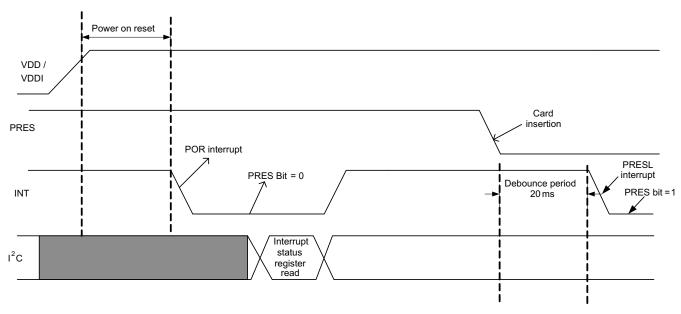

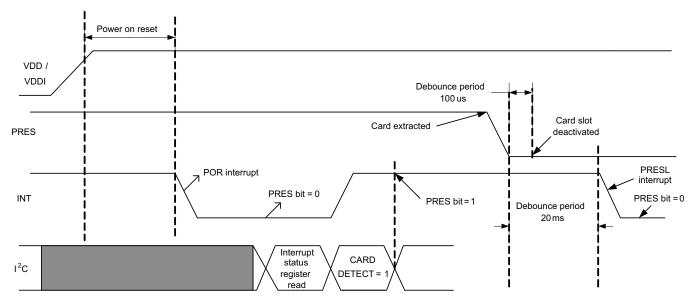

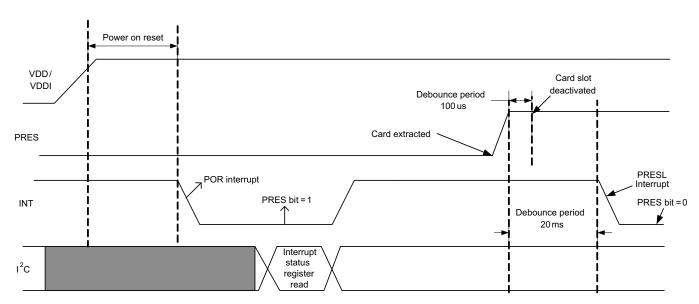

| t <sub>DEB(P)</sub>                                                       | Debounce time         | Time from transition on PRES pin to PRESL bit being set                            |                      | 20  |                               | ms   |  |

| t <sub>DEB(D)</sub>                                                       | Debounce time         | Time from transition on PRES pin to start of deactivation sequence (RST going low) |                      | 100 |                               | μs   |  |

### 6.11 Electrical Characteristics—IOMC1 and IOMC2

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \text{ } \mu\text{H}$ ;  $C_{VDD} = 10 \text{ } \mu\text{F}$ ;  $C_{VUP} = 10 \text{ } \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

| P                               | ARAMETER                       | TEST CONDITION                                                                                                                     | MIN                  | TYP | MAX                  | UNIT |

|---------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|----------------------|------|

| V <sub>OL- IOMC</sub>           | Output low voltage             | I <sub>OL</sub> = -100 μA                                                                                                          |                      |     | 0.2 V <sub>DDI</sub> | V    |

| V <sub>OH - IOMC</sub>          | Output high voltage            | I <sub>OH</sub> = 20 μA                                                                                                            | 0.8 V <sub>DDI</sub> |     |                      | V    |

| V <sub>IL - IOMC</sub>          | Input low signal               |                                                                                                                                    |                      |     | 0.3 V <sub>DDI</sub> | V    |

| V <sub>IH - IOMC</sub>          | Input high signal              |                                                                                                                                    | 0.7 V <sub>DDI</sub> |     |                      | V    |

| t <sub>PD - F - IO - IOMC</sub> | Falling edge propagation delay | From Card IO pin to IOMC; $C_L$ on card IO = 30 pF;<br>Prop delay measured from 30% $V_{CC}$ to 30% of $V_{DDI}$ for falling edge; |                      |     | 250                  | ns   |

| t <sub>PD - F -</sub> 10 - 10MC | Rising edge propagation delay  | From Card IO pin to IOMC; $C_L$ on card IO = 30 pF;<br>Prop delay measured from 70% $V_{CC}$ to 70% of $V_{DDI}$ for rising edge;  |                      |     | 400                  | ns   |

| t <sub>RO - IOMC</sub>          | Output rise time               | C <sub>L</sub> = 30 pF ; 10% to 90%                                                                                                |                      |     | 1.2                  | μs   |

| t <sub>FO - IOMC</sub>          | Output fall time               | C <sub>L</sub> = 30 pF ; 90% to 10%                                                                                                |                      |     | 1.2                  | μs   |

| t <sub>RI - IOMC</sub>          | Input rise time                | 10% to 90%                                                                                                                         |                      |     | 1.2                  | μs   |

| t <sub>FI - IOMC</sub>          | Input fall time                | 90% to 10%                                                                                                                         |                      |     | 1.2                  | μs   |

| C <sub>I - IOMC</sub>           | Input capacitance              |                                                                                                                                    |                      |     | 10                   | pF   |

| R <sub>PU - IOMC</sub>          | Pull-up resistance             | Pull-up to V <sub>DDI</sub>                                                                                                        |                      | 11  |                      | kΩ   |

### 6.12 Electrical Characteristics—CLKIN1 and CLKIN2

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \mu\text{H}$ ;  $C_{VDD} = 10 \mu\text{F}$ ;  $C_{VUP} = 10 \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

| _ DD DDI , VDD - I, , - VDD - I, , - VOF - I, , A |                       |                |                      |     |                               |      |  |

|---------------------------------------------------|-----------------------|----------------|----------------------|-----|-------------------------------|------|--|

|                                                   | PARAMETER             | TEST CONDITION | MIN                  | TYP | MAX                           | UNIT |  |

| V <sub>IL - CLKIN</sub>                           | Input Low voltage     |                |                      |     | $0.2~\mathrm{V}_\mathrm{DDI}$ | V    |  |

| V <sub>IH - CLKIN</sub>                           | Input high voltage    |                | 0.8 V <sub>DDI</sub> |     |                               | V    |  |

| t <sub>R - CLKIN</sub>                            | Rise time             | 10% to 90%     |                      |     | 0.1                           | μs   |  |

| t <sub>F - CLKIN</sub>                            | Fall time             | 90% to 10%     |                      |     | 0.1                           | μs   |  |

| f <sub>CLKIN</sub>                                | Input clock frequency |                |                      |     | 26                            | MHz  |  |

#### 6.13 Electrical Characteristics—A0 and SHDN

$V_{DD} = V_{DDI} = 3.3 \text{ V}$ ;  $L_{VDD} = 10 \mu\text{H}$ ;  $C_{VDD} = 10 \mu\text{F}$ ;  $C_{VIIP} = 10 \mu\text{F}$ ;  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted

| $v_{DD} - v_{DDI} - 3.5 \text{ V}$ , $L_{VDD} - 10  \mu\text{I}$ , $C_{VDD} - 10  \mu\text{I}$ , $C_{VUP} - 10  \mu\text{I}$ |                            |                                   |                      |     |                      |      |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|----------------------|-----|----------------------|------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PARAMETER                  | TEST CONDITION                    | MIN                  | TYP | MAX                  | UNIT |  |  |  |

| V <sub>IL - A0, SHDN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | input Low voltage          |                                   |                      |     | 0.2 V <sub>DDI</sub> | V    |  |  |  |

| V <sub>IH - A0, SHDN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | input high voltage         |                                   | 0.8 V <sub>DDI</sub> |     |                      | V    |  |  |  |

| I <sub>LEAK</sub> - A0, SHDN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input leakage current      | Voltage on pin = V <sub>DDI</sub> |                      |     | 1                    | μA   |  |  |  |

| C <sub>I - A0, SHDN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input Capacitance          |                                   |                      |     | 10                   | pF   |  |  |  |

| R <sub>PU - SHDN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pull-up resistance on SHDN | Pull-up to V <sub>DDI</sub>       |                      | 2.5 |                      | ΜΩ   |  |  |  |

### 6.14 Electrical Characteristics—INT

$V_{DD} = V_{DDI} = 3.3 \text{ V}; L_{VDD} = 10 \mu\text{H}; C_{VDD} = 10 \mu\text{F}; C_{VUP} = 10 \mu\text{F}; T_A = -40 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  unless otherwise noted

|                         | PARAMETER TEST CONDITION |                                   | MIN | TYP | MAX                           | UNIT |

|-------------------------|--------------------------|-----------------------------------|-----|-----|-------------------------------|------|

| I <sub>LEAK - INT</sub> | Input leakage current    | Voltage on pin = V <sub>DDI</sub> |     |     | 1                             | μΑ   |

| V <sub>OL - INT</sub>   | Output low voltage       | $I_{OL} = -3 \text{ mA}$          |     |     | $0.2~\mathrm{V}_\mathrm{DDI}$ | V    |

### 6.15 Electrical Characteristics—GPIO

$\underline{V_{\text{DD}}} = V_{\text{DDI}} = 3.3 \text{ V; } L_{\text{VDD}} = 10 \text{ } \mu\text{H; } C_{\text{VDD}} = 10 \text{ } \mu\text{F; } C_{\text{VUP}} = 10 \text{ } \mu\text{F; } T_{\text{A}} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ unless otherwise noted}$

| PARAMETER                |                                           | TEST CONDITION                                                                                                           |  | TYP | MAX                           | UNIT |

|--------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|-----|-------------------------------|------|

| V <sub>OL - GPIO</sub>   | Output low voltage                        | I <sub>OL</sub> = -10 mA                                                                                                 |  |     | $0.2~\mathrm{V}_\mathrm{DDI}$ | V    |

| I <sub>OL - GPIO</sub>   | Output low current                        |                                                                                                                          |  |     | 10                            | mA   |

| I <sub>LEAK - GPIO</sub> | Input leakage current                     | Voltage on pin = V <sub>DDI</sub>                                                                                        |  |     | 1                             | μΑ   |

| T <sub>PD - GPIO</sub>   | State transition on GPIO to INT assertion | R <sub>PU</sub> on INT= 10 k; C <sub>L</sub> on INT 20 pF;<br>GPIO and INT transition referenced to 0.5 V <sub>DDI</sub> |  |     | 4                             | μs   |

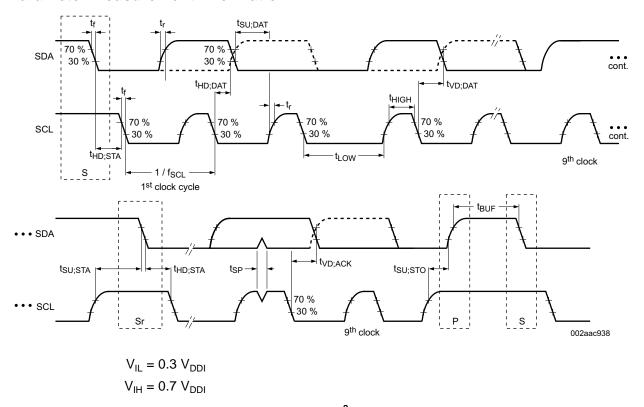

### 6.16 Electrical Characteristics—SDA and SCL

$V_{DD} = V_{DDI} = 3.3 \text{ V}; L_{VDD} = 10 \text{ } \mu\text{H}; C_{VDD} = 10 \text{ } \mu\text{F}; C_{VUP} = 10 \text{ } \mu\text{F}; T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise noted}$

| PARAMETER                    |                            | TEST CONDITION                    | MIN                  | TYP | MAX                  | UNIT |

|------------------------------|----------------------------|-----------------------------------|----------------------|-----|----------------------|------|

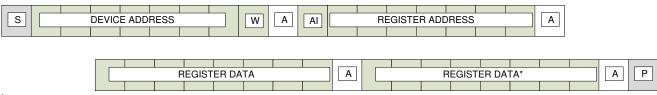

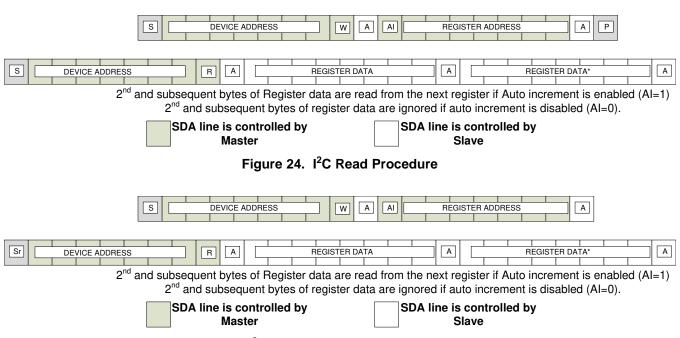

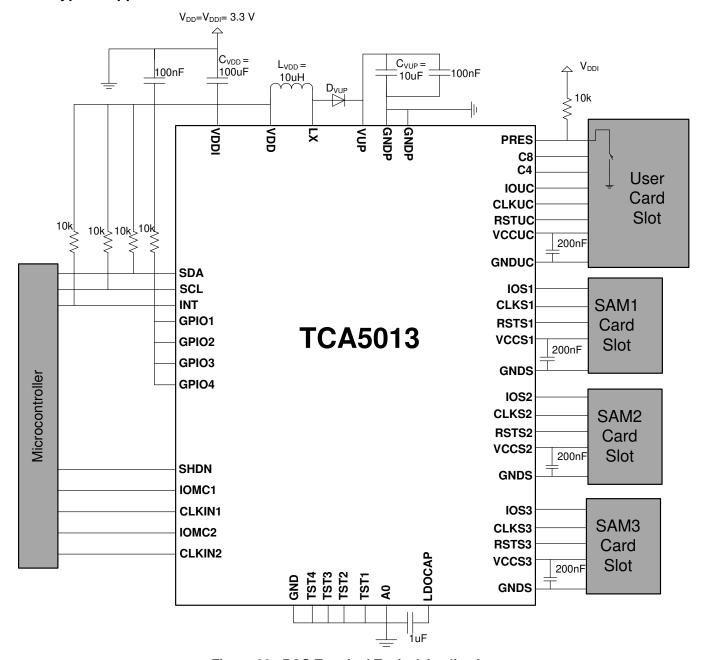

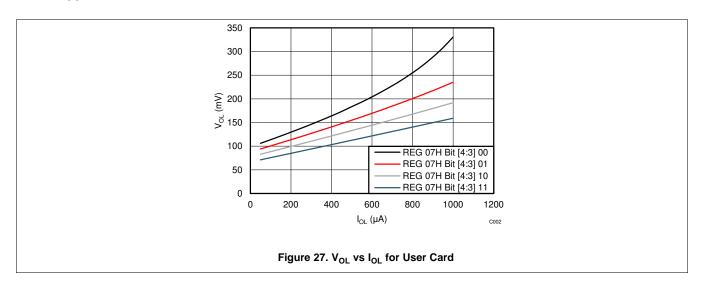

| I <sub>LEAK</sub> - SDA, SCL | Input leakage current      | Voltage on pin = V <sub>DDI</sub> |                      |     | 1                    | μA   |