## Ultra Low Power Sub-1GHz Wireless MCU

## **MCU Features**

- 32 MHz Cortex-M0+ 32-bit CPU platform

- 32 kB Flash with erasing protection

- 4 kB RAM with parity to enhance system stability

- 16 general purpose I/O interfaces available

- Flexible power management system

- 0.5 uA @ 3 V(deep sleep mode): the power consumption when all clocks are off, power-on reset is active, I/O state is maintained, I/O interrupt is active and all registers, RAM, and CPU stay in data storage status

- 0.8 uA @ 3 V (deep sleep mode): the power consumption when RTCs work

- 150 uA/MHz @3 V @16 MHz: the power consumption when CPU and peripheral modules run with program Flash operating internally

- 2 us: the chip's wakeup time from ultra-low power mode, the fast response enables mode switching more flexible and efficient

- RTC and crystal

- External high speed crystal: 4 32 MHz

- External low speed crystal: 32.768 kHz

- Internal high speed clock: 4/8/16/22 and 24 MHz

- Internal low speed clock: 32.8/38.4 kHz

- Timer and counter

- 3 general purpose 16-bit timers/counters

- A 16-bit timer/counter available in low power mode

- 3 high performance 16-bit timers/counters capable for capture/compare and PWM output

- One 20-bit programmable counter/watchdog circuit with built-in dedicated ultra-low power RC-OSC to perform WDT counting

- Communication interface

- UART 0 and UART 1 standard communication interface

- One ultra-low power UART(LPUART) supporting for low speed clock

- Standard I2C and SPI communication interface

- One 12-bit 1 Msps SAR ADC

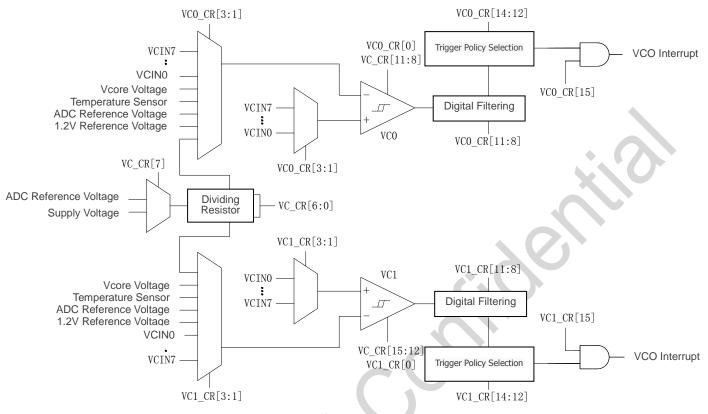

- 2 voltage comparators

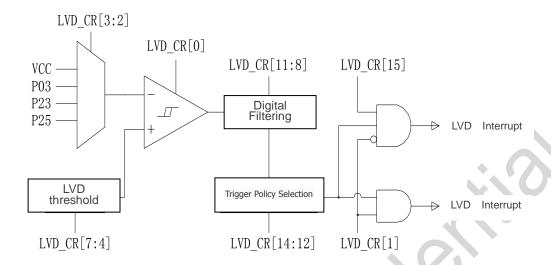

- Low voltage detector (LVD), configurable 16-level comparison level, support for port voltage and supply voltage monitoring

## **RF Features**

- Frequency range: 127 1020 MHz

- Modem: FSK, GFSK, MSK, GMSK and OOK

- Data rate: 0.5 300 kbps

- Sensitivity: -121 dBm @ 434 MHz, FSK

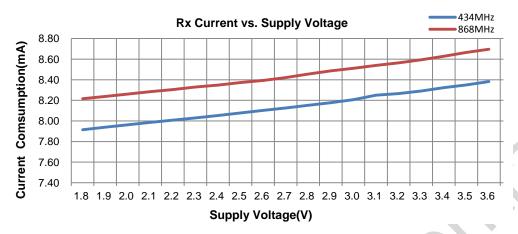

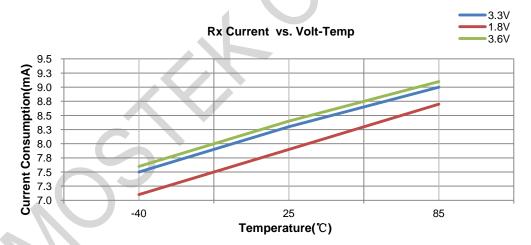

- Receiving current: 8.5 mA @ 434 MHz, FSK

- Transmitting current: 72 mA @ 20 dBm, 434 MHz

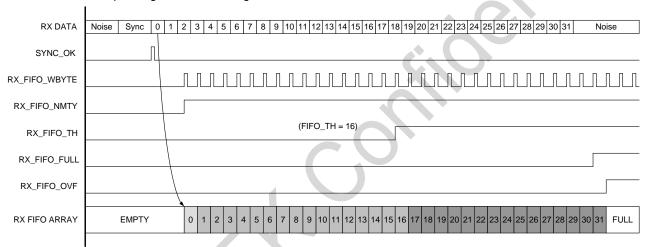

- Configurable up to 64-byte FIFO

## **System Features**

- Supply voltage: 1.8 3.6 V

- Operating temperature: -40 85 °C

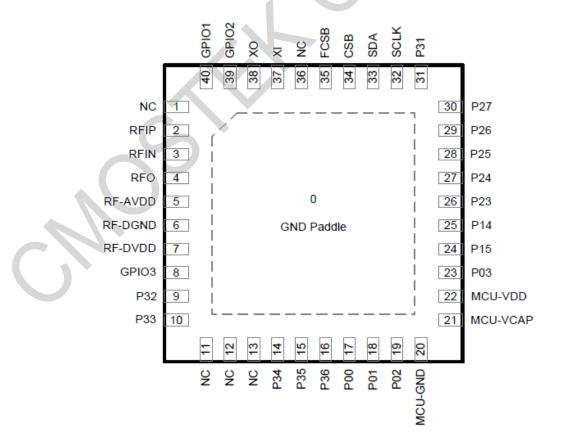

- QFN40 5x5 packaging

## **Application**

- Smart grid and automatic meter reading

- Home security and building automation

- Wireless sensor networks and industrial monitoring

- ISM band data communication

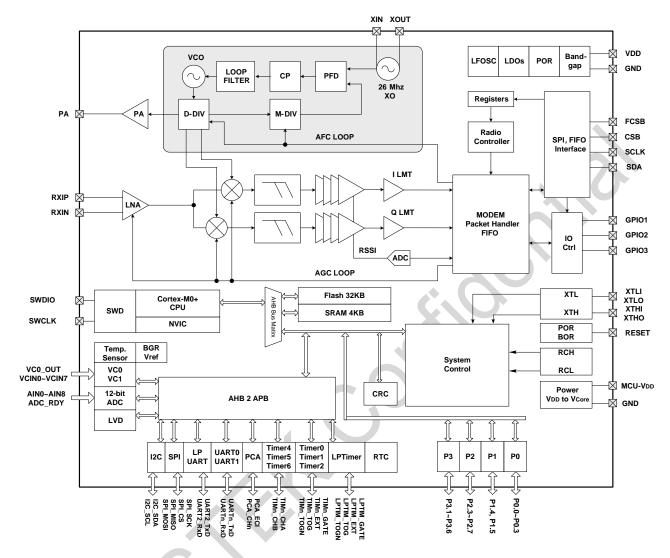

## **Description**

Employed a 32-bit Cortex-M0+ CPU core and an ultra-low power RF transceiver, the CMT2380F32 is a FSK, GFSK, MSK, GMSK and OOK wireless MCU with high performance and ultra-low power applying to 127 to 1020 MHz band wireless applications. Operating with 1.8 to 3.6 V supply voltage, the CMT2380F32 consumes only 72 mA current while delivering up to 20 dBm power. As for the receiver, the

device consumes an ultra-low current of 8.5 mA with the sensitivity reaching -121 dBm.

The device employs a wide range of peripherals like support of standard UART, I2C and SPI interfaces, up to 16 general-purpose I/Os, support of internal high-speed, low-speed, low-power RC oscillators and 32.768 kHz external crystal oscillators, flexible data handling and packet handler, up to 64-byte Tx/Rx FIFO, feature-enriched RF GPIO, multiple low-power modes and fast-start mechanisms, high-precision RSSI, manual fast frequency hopping, multi-channel input 12-bit high-speed ADC, etc. Leading the industry in the aspect of the smallest package size, the CMT2380F32 is ideal for size constraints due to a small form-factor, power-efficient IoT applications.

Table 1. The CMT2380F32 Resource List

| Memory Analog Peripherals |     | Digital Peripherals |      |          |     |     |              |                 |      | Others |     |     |          |          |      |

|---------------------------|-----|---------------------|------|----------|-----|-----|--------------|-----------------|------|--------|-----|-----|----------|----------|------|

| ROM                       | RAM | ADC                 | VCMP | LVD      | RTC | WDT | Timer        | CCP<br>PWM      | UART | LPUART | SPI | I2C | PCA      | CRC      | GPIO |

| 32 k                      | 4 k | 12-bit<br>x9-ch     | 2    | <b>√</b> | ~   | ~   | 16-bit<br>x6 | 16-bit<br>x6-ch | 2    | 1      | 1   | 1   | <b>√</b> | <b>✓</b> | 16+1 |

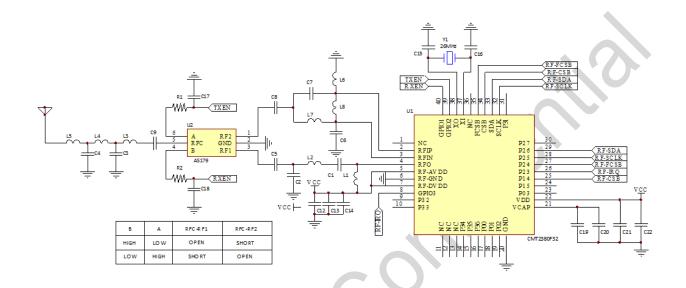

Figure 1. Typical Application Schematic for the CMT2380F32

(20dBm Output Power with Antenna Switch)

Table 2. Typical Application BOM (20 dBm Output Power with Antenna Switch)

|       |                       | Compone      | nt Value    |      |          |  |

|-------|-----------------------|--------------|-------------|------|----------|--|

| Label | Description           | 434 MHz      | 868/915 MHz | Unit | Supplier |  |

| C1    | ± 5%, 0402 NP0, 50 V  | 15           | 15          | pF   | -        |  |

| C2    | ± 5%, 0402 NP0, 50 V  | 10           | 3.9         | pF   | -        |  |

| C3    | ± 5%, 0402 NP0, 50 V  | 8.2          | 2.7         | pF   | -        |  |

| C4    | ± 5%, 0402 NP0, 50 V  | 8.2          | 2.7         | pF   | -        |  |

| C5    | ± 5%, 0402 NP0, 50 V  | 220          | 220         | pF   | -        |  |

| C6    | ± 5%, 0402 NP0, 50 V  | 4.7          | 2           | pF   | -        |  |

| C7    | ± 5%, 0402 NP0, 50 V  | 4.7          | 2           | pF   | -        |  |

| C8    | ± 5%, 0402 NP0, 50 V  | 220          | 220         | pF   | -        |  |

| C9    | ± 5%, 0402 NP0, 50 V  | 220          | 220         | pF   | -        |  |

| C12   | ± 5%, 0402 NP0, 50 V  | P0, 50 V 470 |             | pF   | -        |  |

| C13   | ± 20%, 0402 X7R, 25 V | 2.2          | 2           | nF   | -        |  |

|       |                                                   | Compone | nt Value    |      |              |

|-------|---------------------------------------------------|---------|-------------|------|--------------|

| Label | Description                                       | 434 MHz | 868/915 MHz | Unit | Supplier     |

| C14   | ± 20%, 0603 X7R, 25 V                             | 4.7     |             | uF   | -            |

| C15   | ± 5%, 0402 NP0, 50 V                              | 27      | ,           | pF   | -            |

| C16   | ± 5%, 0402 NP0, 50 V                              | 27      | ,           | pF   | -            |

| C17   | ± 5%, 0402 NP0, 50 V                              | 10      | )           | pF   | -            |

| C18   | ± 5%, 0402 NP0, 50 V                              | 10      | )           | pF   |              |

| C19   | ± 20%, 0402 X7R, 25 V                             | 10      | 0           | nF   |              |

| C20   | ± 20%, 0603 X7R, 25 V                             | 4.7     | 7           | uF   |              |

| C21   | ± 20%, 0402 X7R, 25 V                             | 10      | 0           | nF   | -            |

| C22   | ± 5%, 0402 NP0, 50 V                              | 47      | 0           | pF   | -            |

| L1    | ± 10%, 0603multilayer chip inductor               | 180     | 100         | nΗ   | Sunlord SDCL |

| L2    | ± 10%, 0603 multilayer chip inductor              | 27      | 6.8         | nH   | Sunlord SDCL |

| L3    | ± 10%, 0603 multilayer chip inductor              | 18      | 12          | nH   | Sunlord SDCL |

| L4    | ± 10%, 0603 multilayer chip inductor              | 33      | 22          | nH   | Sunlord SDCL |

| L5    | ± 10%, 0603 multilayer chip inductor              | 15      | 10          | nH   | Sunlord SDCL |

| L6    | ± 10%, 0603 multilayer chip inductor              | 27      | 12          | nH   | Sunlord SDCL |

| L7    | ± 10%, 0603 multilayer chip inductor              | 27      | 12          | nH   | Sunlord SDCL |

| L8    | ± 10%, 0603 multilayer chip inductor              | 68      | 18          | nH   | Sunlord SDCL |

| Y1    | ± 10 ppm, SMD32*25 mm                             | 26      | 3           | MHz  | EPSON        |

| U1    | CMT2380F32, ultra-low power sub-1GHz wireless MCU | -       |             | -    | CMOSTEK      |

| U2    | AS179, PHEMT GaAs IC SPDT Switch                  | -       |             | -    | SKYWORKS     |

| R1    | ± 5%, 0402                                        | 2.2     |             | kΩ   | -            |

| R2    | ± 5%, 0402                                        | 2.2     | 2           | kΩ   | -            |

#### **Table of Contents**

| 1 | Elect | rical Specifications                                               | 7    |

|---|-------|--------------------------------------------------------------------|------|

|   | 1.1   | Recommended Operating Conditions                                   | 7    |

|   | 1.2   | Absolute Maximum Ratings                                           | 7    |

|   | 1.3   | RF Power Consumption                                               | 8    |

|   | 1.4   | Receiver                                                           | 9    |

|   | 1.5   | Transmitter                                                        | 11   |

|   | 1.6   | RF Operating Mode Switching Time                                   | 12   |

|   | 1.7   | RF Frequency Synthesizer                                           | . 12 |

|   | 1.8   | Requirement on Crystals for RF Section                             | 13   |

|   | 1.9   | Controller Output Features                                         | 13   |

|   | 1.10  | Controller Input Features (P0, P1, P2 and P3 Reset)                |      |

|   | 1.11  | Port External Input Sampling Requirements (Timer Gate/Timer Clock) |      |

|   | 1.12  | Port Leakage Features (P0, P1, P2 and P3)                          |      |

|   | 1.13  | Controller Power Consumption Features                              |      |

|   | 1.14  | POR/BOR Features                                                   |      |

|   | 1.15  | Controller External XTH Oscillator                                 |      |

|   | 1.16  | Controller External 32.768 kHz Oscillator                          | 19   |

|   | 1.17  | Controller Internal RCH Oscillator                                 | 19   |

|   | 1.18  | Controller Internal RCL Oscillator                                 |      |

|   | 1.19  | Controller Flash Features                                          | 20   |

|   | 1.20  | Controller Low Power Mode Recover Time                             | 20   |

|   | 1.21  | Controller ADC Features                                            |      |

|   | 1.22  | Analog Voltage Comparator                                          |      |

|   | 1.23  | Low Battery Detection Features                                     | 25   |

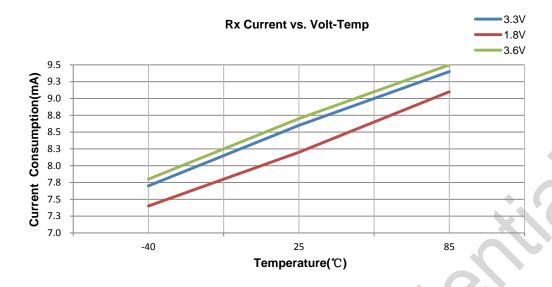

|   | 1.24  | Receive Current and Supply Voltage Correlation                     | 27   |

|   | 1.25  | Correlation Among Receive Current, Supply Voltage and Temperature  |      |

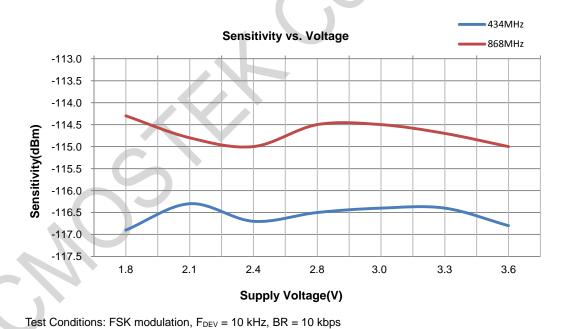

|   | 1.26  | Receive Sensitivity and Supply Voltage Correlation                 |      |

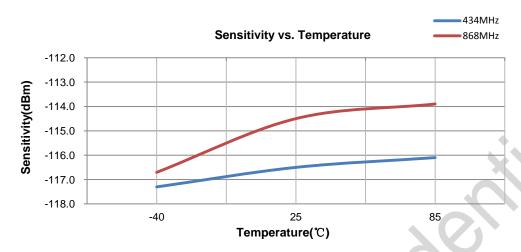

|   | 1.27  | Receive Sensitivity and Temperature Correlation                    |      |

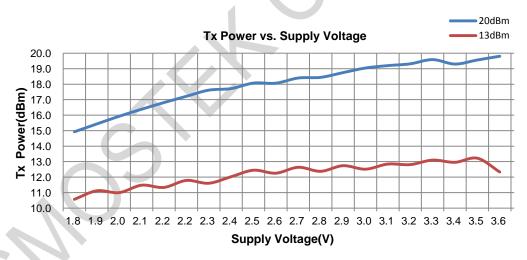

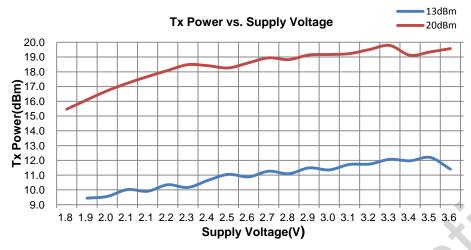

|   | 1.28  | Transmit Power and Supply Voltage Correlation                      |      |

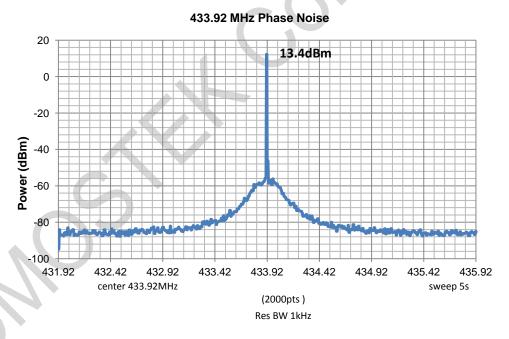

|   | 1.29  | Phase Noise                                                        | 30   |

| 2 | Pin D | Description                                                        | . 31 |

| 3 | Chip  | Structure                                                          | . 37 |

| 4 | Sub-  | GHz Transceiver                                                    | . 39 |

|   | 4.1   | Transmitter                                                        | 30   |

|   | 4.2   | Receiver                                                           |      |

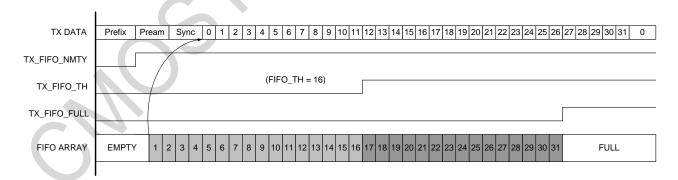

|   | 4.3   | Transceiver Power-on Reset (POR)                                   |      |

|   | 4.4   | Transceiver Crystal Oscillator                                     |      |

|   | 4.5   | Transceiver Built-in Low Frequency Oscillator (LPOSC)              |      |

|   | 4.6   | Transceiver Built-in Low Battery Detection                         |      |

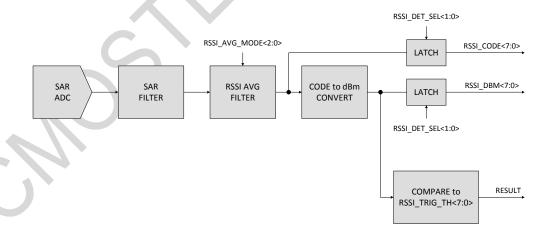

|   | 4.7   | Receiver Signal Strength Indication (RSSI)                         |      |

|   | 4.8   | Phase Jump Detector (PJD)                                          |      |

|   | 4.9   | Receiver Clock Data Recovery (CDR)                                 |      |

|   | -     |                                                                    |      |

|    | 4.10  | Fast Manual Frequency Hopping                                      | 43 |

|----|-------|--------------------------------------------------------------------|----|

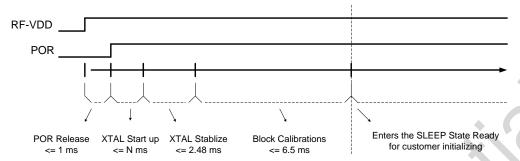

|    | 4.11  | Transceiver Control Interface and Operating Mode                   | 43 |

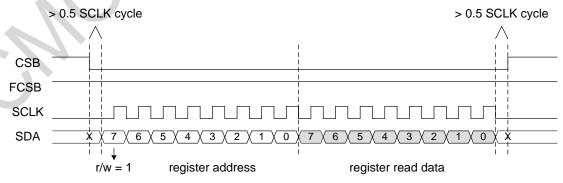

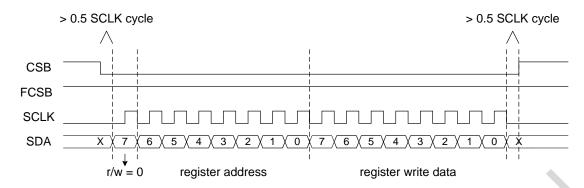

|    | 4     | I.11.1 Transceiver SPI Interface Timing                            | 43 |

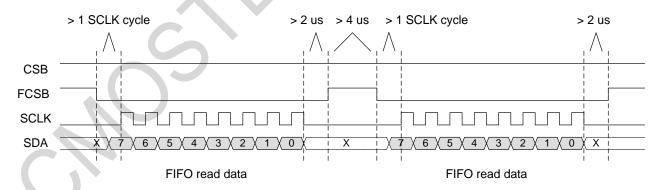

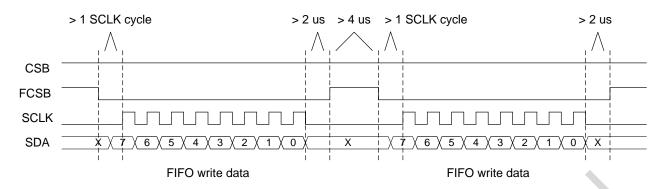

|    |       | 1.11.2 Transceiver FIFO Interface Timing                           |    |

|    |       | 1.11.3 Transceiver Operating Status, Timing, and Power Consumption |    |

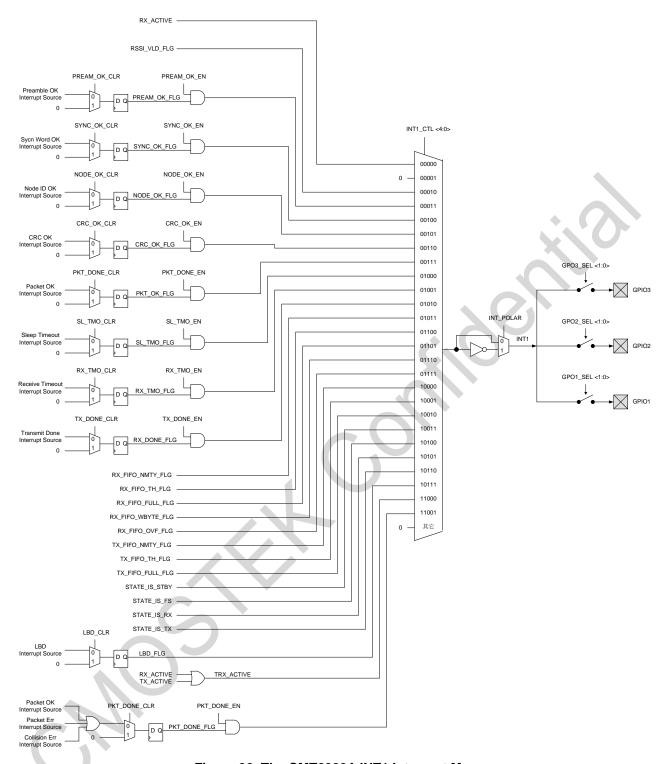

|    | 4     | I.11.4 Transceiver GPIO Function and Interrupt Mapping             | 48 |

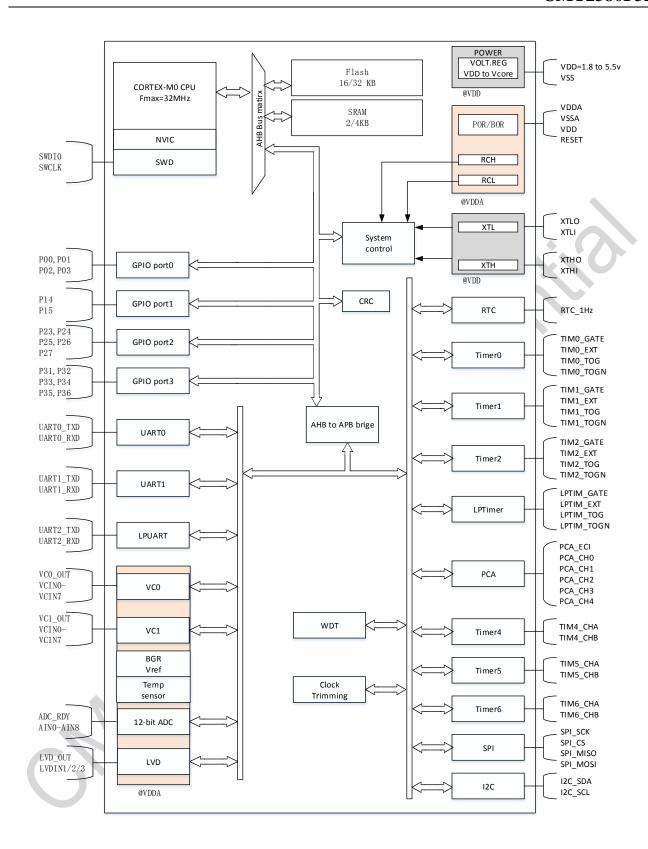

| 5  | Cont  | roller function Introduction                                       | 50 |

|    | 5.1   | Cortex M0+ Core Function Description                               |    |

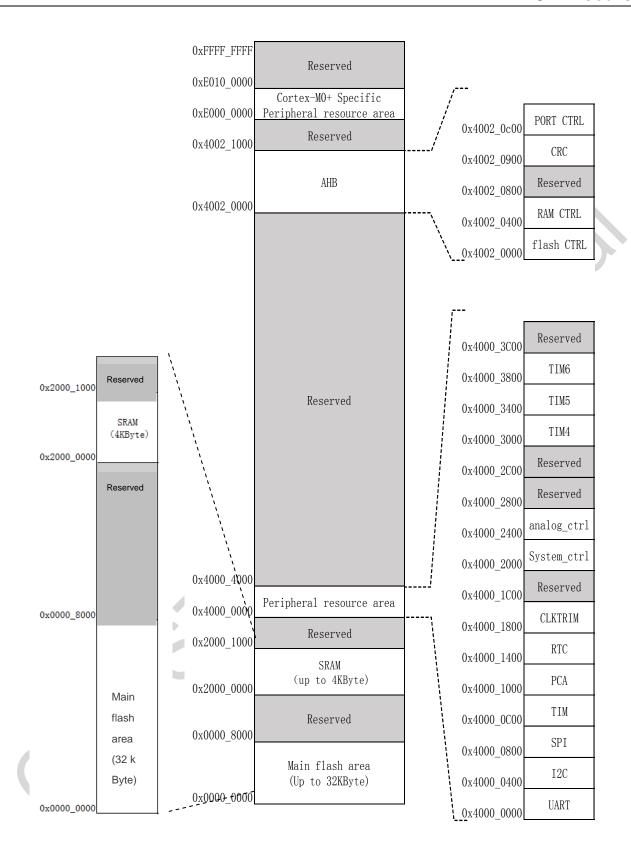

|    | 5.2   | Memory                                                             | 53 |

|    | 5     | 5.2.1 On-chip Program Memory Flash                                 |    |

|    | 5     | 5.2.2 On-chip Data Memory Flash                                    |    |

|    | 5.3   | System Clock                                                       |    |

|    | 5.4   | Operating Mode                                                     |    |

|    | 5.5   | RTC Hardware Real Time Clock RTC                                   | 55 |

|    | 5.6   | General Purpose IO Port                                            |    |

|    | 5.7   | Interrupt Controller                                               |    |

|    | 5.8   | Reset Controller                                                   |    |

|    | 5.9   | Timer/Counter                                                      |    |

|    | 5.10  | Watchdog WDT                                                       | 58 |

|    | 5.11  | Universal Purpose Asynchronous Receiver UART0, UART1 and LPUART    |    |

|    | 5.12  | Synchronous Serial Interface SPI                                   | 59 |

|    | 5.13  | I2C Bus                                                            | 59 |

|    | 5.14  | Buzzer                                                             | 59 |

|    | 5.15  | Clock Calibration Circuit                                          | 59 |

|    | 5.16  | Unique ID number                                                   | 59 |

|    | 5.17  | CRC16 Hardware Cyclic Redundancy Check Code                        | 59 |

|    | 5.18  | 12-bit SARADC                                                      | 59 |

|    | 5.19  | Voltage Comparator (VC)                                            | 59 |

|    | 5.20  | LVD Low Voltage Detector (LVD)                                     | 59 |

|    | 5.21  | Embedded Debug System                                              | 60 |

|    | 5.22  | High Security                                                      | 60 |

| 6  | Orde  | r Information                                                      | 61 |

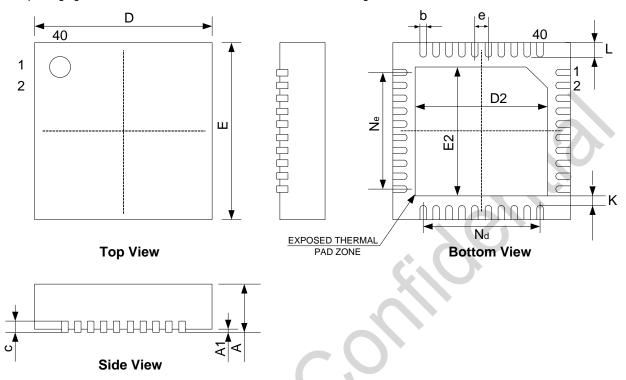

| 7  | Pack  | aging Information                                                  | 62 |

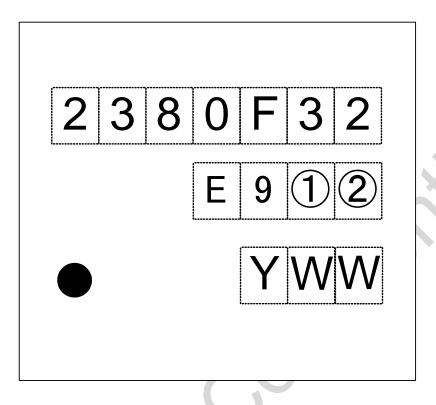

| 8  | Top ! | Marking                                                            | 63 |

| 9  | Refe  | rence Documents                                                    | 64 |

| 10 | Revis | se History                                                         | 64 |

| 11 | Cont  | acts                                                               | 65 |

# 1 Electrical Specifications

$V_{DD}$ = 3.3 V,  $T_{OP}$ = 25 °C,  $F_{RF}$  = 433.92 MHz, sensitivity is measured by receiving a PN9 sequence and matching to 50  $\Omega$  impedance, 0.1% BER if nothing else stated. All measurement results are obtained using the evaluation board CMT2380F32-EM if nothing else stated.

## 1.1 Recommended Operating Conditions

**Table 3. Recommended Operating Conditions**

| Parameter                                   | Symbol               | Condition           | Min. | Тур. | Max. | Unit  |

|---------------------------------------------|----------------------|---------------------|------|------|------|-------|

| Operating supply voltage                    | $V_{DD}$             |                     | 1.8  |      | 3.6  | V     |

| Operating temperature                       | T <sub>OP</sub>      |                     | -40  |      | 85   | °C    |

| Operating speed                             |                      | CPU frequency range | 256k | 4M   | 32 M | Hz    |

| RF supply voltage slope                     | V <sub>RF-PSR</sub>  |                     | 1    |      |      | mV/us |

| Controller supply voltage                   | V <sub>MCU-PSR</sub> |                     | 50   |      |      | mV/us |

| Controller power-on reset effective voltage | V <sub>MCU-POR</sub> |                     |      |      | 0.1  | V     |

## 1.2 Absolute Maximum Ratings

Table 4. Absolute Maximum Ratings[1]

| Parameter                 | Symbol           | Condition                     | Min. | Тур. | Max. |

|---------------------------|------------------|-------------------------------|------|------|------|

| Supply voltage            | $V_{DD}$         |                               | -0.3 | 3.6  | V    |

| Interface voltage         | V <sub>IN</sub>  |                               | -0.3 | 3.6  | V    |

| Junction temperature      | TJ               |                               | -40  | 125  | °C   |

| Storage temperature       | T <sub>STG</sub> |                               | -50  | 150  | °C   |

| Soldering temperature     | T <sub>SDR</sub> | Lasts for at least 30 seconds |      | 255  | °C   |

| ESD rating <sup>[2]</sup> |                  | Human body model (HBM)        | -2   | 2    | kV   |

| Latch-up current          |                  | @ 85 ℃                        | -100 | 100  | mA   |

#### Notes:

- [1]. Exceeding the Absolute Maximum Ratings may cause permanent damage to the equipment. This value is a pressure rating and does not imply that the function of the equipment is affected under this pressure condition, but if it is exposed to absolute maximum ratings for extended periods of time, it may affect equipment reliability.

- [2]. The CMT2380F32 is a high performance RF integrated circuit. The operation and assembly of this chip should only be performed on a workbench with good ESD protection.

Caution! ESD sensitive device. Precaution should be used when handling the device in order to prevent performance degradation or loss of functionality.

# 1.3 RF Power Consumption

**Table 5. RF Power Consumption**

| Parameter                          | Symbol               | Condition                                 | Min. | Тур. | Max. | Unit |

|------------------------------------|----------------------|-------------------------------------------|------|------|------|------|

| Class surrent                      |                      | Sleep mode, sleep counter off             |      | 300  |      | nA   |

| Sleep current                      | I <sub>SLEEP</sub>   | Sleep mode ,sleep counter on              |      | 800  |      | nA   |

| Standby current                    | I <sub>Standby</sub> | Crystal oscillator on                     |      | 1.45 |      | mA   |

|                                    |                      | 433 MHz                                   |      | 5.7  |      | mA   |

| RFS current                        | I <sub>RFS</sub>     | 868 MHz                                   |      | 5.8  |      | mA   |

|                                    |                      | 915 MHz                                   |      | 5.8  |      | mA   |

|                                    |                      | 433 MHz                                   |      | 5.6  |      | mA   |

| TFS current                        | I <sub>TFS</sub>     | 868 MHz                                   |      | 5.9  |      | mA   |

|                                    |                      | 915 MHz                                   |      | 5.9  |      | mA   |

| EOK DV                             |                      | 433 MHz, 10 kbps,10 kHz F <sub>DEV</sub>  |      | 8.5  |      | mA   |

| FSK, RX current (high performance) | I <sub>Rx-HP</sub>   | 868 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 8.6  |      | mA   |

|                                    |                      | 915 MHz, 10 kbps,10 kHz F <sub>DEV</sub>  |      | 8.9  |      | mA   |

| FSK, RX current                    |                      | 433 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> | X    | 7.2  |      | mA   |

|                                    | I <sub>Rx-LP</sub>   | 868 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.3  |      | mA   |

| (low power mode)                   |                      | 915 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.6  |      | mA   |

|                                    |                      | 433 MHz, +20 dBm (Direct-tie)             |      | 72   |      | mA   |

|                                    |                      | 433 MHz, +20 dBm (With RF switch)         |      | 77   |      | mA   |

|                                    |                      | 433 MHz, +13 dBm (Direct-tie)             |      | 23   |      | mA   |

|                                    |                      | 433 MHz, +10 dBm (Direct-tie)             |      | 18   |      | mA   |

|                                    |                      | 433 MHz, -10 dBm (Direct-tie)             |      | 8    |      | mA   |

|                                    |                      | 868 MHz, +20dBm (Direct-tie)              |      | 87   |      | mA   |

|                                    |                      | 868 MHz, +20dBm (With RF switch)          |      | 80   |      | mA   |

| FSK, TX current                    | I <sub>Tx</sub>      | 868 MHz, +13 dBm (Direct-tie)             |      | 27   |      | mA   |

|                                    |                      | 868 MHz, +10 dBm (Direct-tie)             |      | 19   |      | mA   |

|                                    |                      | 868 MHz, -10 dBm (Direct-tie)             |      | 8    |      | mA   |

|                                    |                      | 915 MHz, +20 dBm (Direct-tie)             |      | 70   |      | mA   |

|                                    |                      | 915 MHz, +20 dBm (Direct-tie)             |      | 75   |      | mA   |

|                                    | 1                    | 915 MHz, +13 dBm (Direct-tie)             |      | 28   |      | mA   |

|                                    |                      | 915 MHz, +10 dBm (Direct-tie)             |      | 19   |      | mA   |

|                                    |                      | 915 MHz, +10 dBm (Direct-tie)             |      | 8    |      | mA   |

## 1.4 Receiver

**Table 6. Receiver Specifications**

| Data Rate Error           | DR<br>F <sub>DEV</sub> | OOK FSK and GFSK FSK and GFSK                                                 | 0.5 |      | 40<br>300  | kbps |

|---------------------------|------------------------|-------------------------------------------------------------------------------|-----|------|------------|------|

|                           |                        |                                                                               |     |      | 200        |      |

| Error                     | F <sub>DEV</sub>       | FSK and GFSK                                                                  | _   |      | 300        | kbps |

|                           |                        |                                                                               | 2   |      | 200        | kHz  |

|                           |                        | DR = 2.0 kbps, $F_{DEV}$ = 10 kHz                                             |     | -121 | •          | dBm  |

|                           |                        | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz                                       |     | -116 |            | dBm  |

|                           |                        | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz (low power mode)                      |     | -115 | <b>*</b> ( | dBm  |

|                           |                        | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz                                       |     | -113 |            | dBm  |

| Sensitivity<br>@ 433 MHz  | S <sub>433-HP</sub>    | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (low power mode)                      |     | -112 |            | dBm  |

|                           |                        | DR = 50 kbps, F <sub>DEV</sub> = 25 kHz                                       |     | -111 |            | dBm  |

|                           |                        | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                       |     | -108 |            | dBm  |

|                           |                        | DR =200 kbps, $F_{DEV} = 100 \text{ kHz}$                                     |     | -105 |            | dBm  |

|                           |                        | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                      |     | -103 |            | dBm  |

|                           |                        | DR = 2 kbps, F <sub>DEV</sub> = 10 kHz                                        |     | -119 |            | dBm  |

|                           |                        | $DR = 10 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$                              |     | -113 |            | dBm  |

|                           |                        | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz (low power                            |     | -111 |            | dBm  |

|                           | S <sub>868-HP</sub>    | mode)                                                                         |     | 444  |            | -dD  |

| Sensitivity               |                        | DR = 20 kbps, $F_{DEV}$ = 20 kHz                                              |     | -111 |            | dBm  |

| @ 868 MHz                 |                        | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (low power mode)                      |     | -109 |            | dBm  |

|                           |                        | $DR = 50 \text{ kbps}, F_{DEV} = 25 \text{ kHz}$                              |     | -108 |            | dBm  |

|                           |                        | DR =100 kbps, $F_{DEV} = 50 \text{ kHz}$                                      |     | -105 |            | dBm  |

|                           |                        | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                      |     | -102 |            | dBm  |

|                           |                        | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                      |     | -99  |            | dBm  |

|                           |                        | $DR = 2 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$                               |     | -117 |            | dBm  |

|                           |                        | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz                                       |     | -113 |            | dBm  |

|                           |                        | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz(low power mode)                       |     | -111 |            | dBm  |

| Sensitivity               |                        | DR = 20 kbps, $F_{DEV}$ = 20 kHz                                              |     | -111 |            | dBm  |

| @ 915 MHz                 | S <sub>915-HP</sub>    | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (low power mode)                      |     | -109 |            | dBm  |

|                           |                        | DR = 50 kbps, $F_{DEV}$ = 25 kHz                                              |     | -109 |            | dBm  |

|                           |                        | DR =100 kbps, $F_{DEV} = 50 \text{ kHz}$                                      |     | -105 |            | dBm  |

|                           |                        | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                      |     | -102 |            | dBm  |

|                           |                        | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                      |     | -99  |            | dBm  |

| Saturation                | P <sub>LVL</sub>       | 211 -000 h0p0, 1 DEV - 100 h112                                               |     | J-3  | 20         | dBm  |

| Catalation                | • LVL                  | F <sub>RF</sub> = 433 MHz                                                     |     | 35   | 20         | dBc  |

| Image rejection ratio     | IMR                    | F <sub>RF</sub> = 868 MHz                                                     |     | 33   |            | dBc  |

| ago rojoulon ralio        | 114117                 | F <sub>RF</sub> = 915 MHz                                                     |     | 33   |            | dBc  |

| Receive channel bandwidth | BW                     | Receive channel bandwidth                                                     | 50  |      | 500        | kHz  |

| Co-channel rejection      | CCR                    | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz Interference with the same modulation |     | -7   |            | dBc  |

| Parameter                                   | Symbol   | Condition                                                                                                                | Min. | Тур.   | Max. | Unit |

|---------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|

| Adjacent channel rejection                  | ACR-I    | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz, BW = 100 kHz, 200 kHz channel spacing, interference with the same modulation    |      | 30     |      | dBc  |

| Alternate channel rejection                 | ACR-II   | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz,<br>BW=100kHz, 400 kHz channel spacing,<br>interference with the same modulation |      | 45     |      | dBc  |

|                                             |          | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz, ±1 MHz offset, continuous wave interference                                     |      | 70     |      | dBc  |

| Blocking                                    | ВІ       | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz, ± 2 MHz offset, continuous wave interference                                    |      | 72     |      | dBc  |

|                                             |          | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz, ±10 MHz offset, continuous wave interference                                    |      | 75     |      | dBc  |

| Input 3 <sup>rd</sup> order intercept point | IIP3     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz, 1 MHz and<br>20 MHz offset two tone test, maximum<br>system gain setting        |      | -25    |      | dBm  |

| RSSI range                                  | RSSI     |                                                                                                                          | -120 |        | 20   | dBm  |

|                                             |          | $DR = 1.2 \text{ kbps}, F_{DEV} = 5 \text{ kHz}$                                                                         |      | -122.9 |      | dBm  |

|                                             |          | $DR = 1.2 \text{ kbps}, F_{DEV} = 10 \text{kHz}$                                                                         |      | -121.8 |      | dBm  |

|                                             |          | $DR = 1.2 \text{ kbps}, F_{DEV} = 20 \text{ kHz}$                                                                        |      | -119.5 |      | dBm  |

|                                             |          | $DR = 2.4 \text{ kbps}, F_{DEV} = 5 \text{ kHz}$                                                                         |      | -120.6 |      | dBm  |

|                                             |          | DR = 2.4 kbps, F <sub>DEV</sub> = 10 kHz                                                                                 |      | -120.3 |      | dBm  |

|                                             |          | $DR = 2.4 \text{ kbps}, F_{DEV} = 20 \text{ kHz}$                                                                        |      | -119.7 |      | dBm  |

|                                             |          | $DR = 9.6 \text{ kbps}, F_{DEV} = 9.6 \text{ kHz}$                                                                       |      | -116.0 |      | dBm  |

| Sensitivity                                 |          | $DR = 9.6 \text{ kbps}, F_{DEV} = 19.2 \text{ kHz}$                                                                      |      | -116.1 |      | dBm  |

| @ 433.92 MHz<br>(typical                    |          | DR = 20 kbps, F <sub>DEV</sub> = 10 kHz                                                                                  |      | -114.2 |      | dBm  |

| configuration)                              |          | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz                                                                                  |      | -113.0 |      | dBm  |

| oorinigaration)                             |          | DR = 50 kbps, F <sub>DEV</sub> = 25 kHz                                                                                  |      | -110.6 |      | dBm  |

|                                             |          | $DR = 50 \text{ kbps}, F_{DEV} = 50 \text{ kHz}$                                                                         |      | -109.0 |      | dBm  |

|                                             |          | $DR = 100 \text{ kbps}, F_{DEV} = 50 \text{ kHz}$                                                                        |      | -107.8 |      | dBm  |

|                                             | <b>(</b> | DR = 200 kbps, F <sub>DEV</sub> = 50 kHz                                                                                 |      | -103.5 |      | dBm  |

|                                             |          | $DR = 200 \text{ kbps}, F_{DEV} = 100 \text{ kHz}$                                                                       |      | -104.3 |      | dBm  |

|                                             |          | $DR = 300 \text{ kbps}, F_{DEV} = 50 \text{ kHz}$                                                                        |      | -98.0  |      | dBm  |

|                                             |          | DR = 300 kbps, F <sub>DEV</sub> = 150 kHz                                                                                |      | -101.6 |      | dBm  |

## 1.5 Transmitter

**Table 7. Transmitter Specifications**

| Parameter                                      | Symbol               | Condition                                                           | Min. | Тур. | Max. | Unit |

|------------------------------------------------|----------------------|---------------------------------------------------------------------|------|------|------|------|

| Output power                                   | P <sub>OUT</sub>     | Specific matching network is required for different frequency bands | -20  |      | +20  | dBm  |

| Output power step                              | P <sub>STEP</sub>    |                                                                     |      | 1    |      | dB   |

| GFSK (Gaussian filter coefficient)             | ВТ                   |                                                                     | 0.3  | 0.5  | 1.0  |      |

| Output power change with different temperature | P <sub>OUT-TOP</sub> | Temperature range:-40 to + 85 °C                                    |      | 1    |      | dB   |

| Courieus emissiens                             |                      | $P_{OUT} = +13 \text{ dBm},433\text{MHz}, F_{RF} < 1 \text{ GHz}$   |      |      | -54  | dBm  |

| Spurious emissions                             |                      | 1 GHz to12.75 GHz, including harmonics                              |      |      | -36  | dBm  |

| Harmonic output <sup>[1]</sup>                 | H2 <sub>433</sub>    | 2 <sup>nd</sup> harmonic,+20 dBm P <sub>OUT</sub>                   |      | - 46 |      | dBm  |

| for F <sub>RF</sub> = 433 MHz                  | H3 <sub>433</sub>    | 3 <sup>nd</sup> harmonic,+20 dBm P <sub>OUT</sub>                   |      | - 50 |      | dBm  |

| Harmonic output <sup>[1]</sup>                 | H2 <sub>868</sub>    | 2 <sup>nd</sup> harmonic,+20 dBm P <sub>OUT</sub>                   |      | - 43 |      | dBm  |

| for F <sub>RF</sub> = 868 MHz                  | H3 <sub>868</sub>    | 3 <sup>nd</sup> harmonic,+20 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

| Harmonic output <sup>[1]</sup>                 | H2 <sub>915</sub>    | 2 <sup>nd</sup> harmonic,+20 dBm P <sub>OUT</sub>                   |      | - 48 |      | dBm  |

| for F <sub>RF</sub> = 915 MHz                  | H3 <sub>915</sub>    | 3 <sup>nd</sup> harmonic,+20 dBm P <sub>OUT</sub>                   |      | - 53 |      | dBm  |

| Harmonic output <sup>[1]</sup>                 | H2 <sub>433</sub>    | 2 <sup>nd</sup> harmonic,+13 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

| for F <sub>RF</sub> = 433 MHz                  | H3 <sub>433</sub>    | 3 <sup>nd</sup> harmonic,+13 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

| Harmonic output <sup>[1]</sup>                 | H2 <sub>868</sub>    | 2 <sup>nd</sup> harmonic,+13 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

| for F <sub>RF</sub> = 868 MHz                  | H3 <sub>868</sub>    | 3 <sup>nd</sup> harmonic,+13 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

| Harmonic output <sup>[1]</sup>                 | H2 <sub>915</sub>    | 2 <sup>nd</sup> harmonic,+13 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

| for F <sub>RF</sub> = 915 MHz                  | H3 <sub>915</sub>    | 3 <sup>nd</sup> harmonic,+13 dBm P <sub>OUT</sub>                   |      | - 52 |      | dBm  |

#### Notes:

Rev0.9 | 11/65

<sup>[1].</sup> The harmonic level mainly depends on the matching network. Above parameters are measured based on the CMT2380F32-EM, users may get different results on their applications.

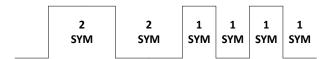

# 1.6 RF Operating Mode Switching Time

**Table 8. RF Operating Mode Switching Time**

| Parameter                        | Symbol                             | Condition                                 | Min. | Тур.                 | Max.     | Units |

|----------------------------------|------------------------------------|-------------------------------------------|------|----------------------|----------|-------|

|                                  | T <sub>SLP-RX</sub> <sup>[1]</sup> | From sleep to RX                          |      | 1                    |          | ms    |

|                                  | T <sub>SLP-TX</sub> <sup>[1]</sup> | From sleep to TX                          |      | 1                    |          | ms    |

|                                  | T <sub>STB-RX</sub>                | From standby to RX                        |      | 350                  |          | us    |

| DE aparating made                | T <sub>STB-TX</sub>                | From standby to TX                        |      | 350                  |          | us    |

| RF operating mode switching time | T <sub>RFS-RX</sub>                | From RFS to RX                            |      | 20                   |          | us    |

| Switching time                   | T <sub>TFS-RX</sub>                | From TFS to TX                            |      | 20                   | <b>\</b> | us    |

|                                  | T <sub>TX-RX</sub>                 | From TX to RX                             |      | 2T <sub>symbol</sub> |          | 31    |

|                                  |                                    | (Needs 2T <sub>symbol</sub> to ramp down) |      | +350                 |          | us    |

|                                  | T <sub>RX-TX</sub>                 | From RX to TX                             |      | 350                  |          | us    |

#### Notes:

## 1.7 RF Frequency Synthesizer

**Table 9. RF Frequency Synthesizer**

| Parameter                | Symbol            | Condition         | Min. | Тур. | Max. | Unit   |

|--------------------------|-------------------|-------------------|------|------|------|--------|

|                          |                   |                   | 760  |      | 1020 | MHz    |

|                          | _                 |                   | 380  |      | 510  | MHz    |

| Frequency range          | $F_RF$            |                   | 190  |      | 340  | MHz    |

|                          |                   |                   | 127  |      | 170  | MHz    |

| Frequency resolution     | F <sub>RES</sub>  |                   |      | 25   |      | Hz     |

| Frequency tuning time    | t <sub>TUNE</sub> |                   |      | 150  |      | us     |

|                          |                   | 10 kHz deviation  |      | -94  |      | dBc/Hz |

| Dhana maina @ 400        | PN <sub>433</sub> | 100 kHz deviation |      | -99  |      | dBc/Hz |

| Phase noise @ 433<br>MHz |                   | 500 kHz deviation |      | -118 |      | dBc/Hz |

| IVITIZ                   |                   | 1MHz deviation    |      | -127 |      | dBc/Hz |

|                          |                   | 10 MHz deviation  |      | -134 |      | dBc/Hz |

|                          |                   | 10 kHz deviation  |      | -92  |      | dBc/Hz |

| DI                       |                   | 100 kHz deviation |      | -95  |      | dBc/Hz |

| Phase noise @ 868<br>MHz | PN <sub>868</sub> | 500 kHz deviation |      | -114 |      | dBc/Hz |

| IVITIZ                   |                   | 1MHz deviation    |      | -121 |      | dBc/Hz |

|                          |                   | 10 MHz deviation  |      | -130 |      | dBc/Hz |

|                          |                   | 10 kHz deviation  |      | -89  |      | dBc/Hz |

| Di                       |                   | 100 kHz deviation |      | -92  |      | dBc/Hz |

| Phase noise @ 915        | PN <sub>915</sub> | 500 kHz deviation |      | -111 |      | dBc/Hz |

| MHz                      |                   | 1MHz deviation    |      | -121 |      | dBc/Hz |

|                          |                   | 10 MHz deviation  |      | -130 |      | dBc/Hz |

<sup>[1].</sup> T<sub>SLP-RX</sub> and T<sub>SLP-TX</sub> are dominated by the crystal oscillator startup time, and the start-up time is to a large degree crystal dependent.

## 1.8 Requirement on Crystals for RF Section

Table 10. Requirement on Crystals for RF Section

| Parameter                                  | Symbol            | Condition | Min. | Тур. | Max. | Unit |

|--------------------------------------------|-------------------|-----------|------|------|------|------|

| Crystal frequency <sup>[1]</sup>           | F <sub>XTAL</sub> |           |      | 26   |      | MHz  |

| Crystal frequency tolerance <sup>[2]</sup> | ppm               |           |      | 20   |      | ppm  |

| Load capacitance                           | $C_{LOAD}$        |           |      | 15   |      | pF   |

| ESR                                        | Rm                |           |      | 60   |      | Ω    |

| Crystal startup time <sup>[3]</sup>        | t <sub>XTAL</sub> |           |      | 400  |      | us   |

#### Notes:

- [1]. An external 26 MHz reference clock can be used to drive the XI pin directly through a coupling capacitor if such a clock is available. The peak-to-peak level of the external reference clock is required between 0.3 and 0.7 V.

- [2]. It involves:(1) initial tolerance, (2) crystal loading, (3) aging, and (4) temperature changing. The acceptable crystal frequency tolerance is subject to the bandwidth of the receiver and the RF tolerance between the receiver and its paired transmitter.

- [3]. This parameter is to a large degree crystal dependent.

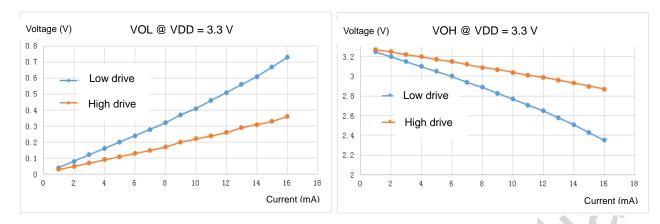

## 1.9 Controller Output Features

**Table 11. Controller Output Features**

| Parameter         | Symbol                                | Condition                                      | Min.                   | Тур. | Max.                   | Unit |

|-------------------|---------------------------------------|------------------------------------------------|------------------------|------|------------------------|------|

| Outrot bish lavel | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Sourcing 4 mA current, V <sub>DD</sub> = 3.3V  | V <sub>DD</sub> - 0.25 |      |                        | V    |

| Output high level | V <sub>OH</sub>                       | Sourcing 6 mA current, V <sub>DD</sub> = 3.3V  | V <sub>DD</sub> - 0.60 |      |                        | V    |

| Outrat law laws   |                                       | Sinking 4 mA current, V <sub>DD</sub> = 3.3V   |                        |      | V <sub>DD</sub> + 0.25 | V    |

| Output low level  | V <sub>OL</sub>                       | Sinking 6 mA current, V <sub>DD</sub> = 3.3V   |                        |      | V <sub>DD</sub> + 0.60 | V    |

| Output high level | V                                     | Sourcing 8 mA current, V <sub>DD</sub> = 3.3V  | V <sub>DD</sub> - 0.25 |      |                        | V    |

| (enhanced mode)   | V <sub>OHD</sub>                      | Sourcing 12 mA current, V <sub>DD</sub> = 3.3V | V <sub>DD</sub> - 0.60 |      |                        | V    |

| Output low level  | N.                                    | Sinking 8 mA current, V <sub>DD</sub> = 3.3V   |                        |      | V <sub>DD</sub> + 0.25 | V    |

| (enhanced mode)   | V <sub>OLD</sub>                      | Sinking 12 mA current, V <sub>DD</sub> = 3.3V  |                        |      | V <sub>DD</sub> + 0.60 | V    |

#### Notes:

- The maximum total current of I<sub>OH</sub> and I<sub>OL</sub> (sum of all pins) shall not exceed 40 mA to meet the specified maximum voltage drop.

- The maximum total current of I<sub>OH</sub> and I<sub>OL</sub> (sum of all pins, enhanced mode) shall not exceed 100 mA to meet the specified maximum voltage drop.

Figure 2. Controller I/O Driving Ability

## 1.10 Controller Input Features (P0, P1, P2 and P3 Reset)

**Symbol Parameter** Condition Min. Тур. Max. Unit  $V_{DD} = 1.8 \text{ V}$ 1 1.1 1.2 ٧ Output high level  $V_{IH}$  $V_{DD} = 3.3 \text{ V}$ 1.8 2 2.2 ٧  $V_{DD} = 1.8 \text{ V}$ ٧ 0.6 0.7 8.0 Output low level  $V_{\mathsf{IL}}$  $V_{DD} = 3.3 \text{ V}$ 1.1 1.3 ٧ 1.5  $V_{DD} = 1.8 \text{ V}$ 0.4 0.4 0.4 Input hysteresis range  $V_{HYS}$  $V_{DD} = 3.3 \text{ V}$ 0.7 0.7 0.7 V

80

5

Table 12. Controller Input Features (P0, P1, P2 and P3 Reset)

# 1.11 Port External Input Sampling Requirements (Timer Gate/Timer Clock)

Pull-up enabled

$R_{\text{\tiny PUP}}$

Table 13. Port External Input Sampling Requirements (Timer Gate/Timer Clock)

Sinking 12 mA current,  $V_{DD} = 3.3 \text{ V}$

| Parameter                            | Symbol           | Condition               | Min.              | Тур. | Max.   | Unit |

|--------------------------------------|------------------|-------------------------|-------------------|------|--------|------|

| External interrupt input pulse width | <b>-</b>         | V <sub>DD</sub> = 1.8 V | 30 <sup>[1]</sup> |      |        | ns   |

|                                      | $T_{INT}$        | V <sub>DD</sub> = 3.3 V | 30 <sup>[1]</sup> |      |        | ns   |

| Timer 4/5/6 capture pulse width      | <b>-</b>         | V <sub>DD</sub> = 1.8 V | 0.5               |      |        | us   |

| (F <sub>SYS</sub> =4MHz)             | $T_CAP$          | V <sub>DD</sub> = 3.3 V | 0.5               |      |        | us   |

| Timer 0/1/2/4/5/6 external clock     | <b>-</b>         | V <sub>DD</sub> = 1.8 V |                   |      | PCLK/2 | MHz  |

| input (F <sub>SYS</sub> =4MHz)       | T <sub>CLK</sub> | V <sub>DD</sub> = 3.3 V |                   |      | PCLK/2 | MHz  |

| DCA external input plant             | <b>T</b>         | V <sub>DD</sub> = 1.8 V |                   |      | PCLK/8 | MHz  |

| PCA external input clock             | $T_PCA$          | V <sub>DD</sub> = 3.3 V |                   |      | PCLK/8 | MHz  |

#### Notes:

$(V_{IH}-V_{IL})$

Pull-up resistor

Input capacitance

kΩ

рF

<sup>[1].</sup> It's the minimum external interrupt input pulse width used in the practical test for triggering the interrupt. It can support triggering the interrupt with even shorter pulse width based on the chip capability.

# 1.12 Port Leakage Features (P0, P1, P2 and P3)

Table 14. Port Leakage Features (P0, P1, P2, and P3)

| Parameter       | Symbol          | Condition                     | Min. | Тур. | Max. | Unit |

|-----------------|-----------------|-------------------------------|------|------|------|------|

| Leakage current | $I_{lkg(Px,y)}$ | V <sub>DD</sub> : 1.8 to 3.6V |      |      | ± 50 | nA   |

#### Notes:

- [1]. Unless otherwise specified, the leakage current is measured with GND or VDD applied to the corresponding pin.

- [2]. The pin to be tested must be set to input mode.

## 1.13 Controller Power Consumption Features

**Table 15. Controller Power Consumption Features**

| Parameter                      | Symbol               | Condition                                                                                                                   | Note                                                           | Тур. | Max. | Unit |

|--------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|------|------|

|                                |                      |                                                                                                                             | 4 MHz                                                          | 220  |      | uA   |

|                                |                      | V <sub>CORE</sub> = 1.55 V, V <sub>DD</sub> = 3.3 V. All                                                                    | 8 MHz                                                          | 400  |      | uA   |

| Operating current when program | I <sub>DD-RAM</sub>  | peripheral clock sources are off. Run While(1) in SRAM with RCH as clock source.                                            | 16 MHz                                                         | 740  |      | uA   |

| running in SRAM                |                      |                                                                                                                             | 24 MHz                                                         | 1080 |      | uA   |

|                                |                      |                                                                                                                             | 32 MHz                                                         | 1400 |      | uA   |

|                                |                      | 1                                                                                                                           | <sub>E</sub> = 1.55 V, V <sub>DD</sub> = 3.3 V. AII 8 MHz 1300 | 670  |      | uA   |

| Core mark operating current    | I <sub>DD-Mark</sub> | V <sub>CORE</sub> = 1.55 V, V <sub>DD</sub> = 3.3 V. All                                                                    | 8 MHz                                                          | 1300 |      | uA   |

|                                |                      | peripheral clock sources are off. Run Core Mark in Flash with RCH                                                           | 16 MHz                                                         | 2380 |      | uA   |

|                                |                      | as clock source                                                                                                             | 24 MHz                                                         | 3410 |      | uA   |

|                                |                      |                                                                                                                             | 32 MHz<br>Flash Wait=1                                         | 3530 |      | uA   |

|                                |                      |                                                                                                                             | 4 MHz                                                          | 700  | 880  | uA   |

|                                |                      | $V_{CORE}$ = 1.55 V, $V_{DD}$ = 3.3 V. All peripheral clock sources are on. Run While(1) in Flash with RCH as clock source. | 8 MHz                                                          | 1350 | 1600 | uA   |

|                                |                      |                                                                                                                             | 16 MHz                                                         | 2500 | 3000 | uA   |

|                                |                      | diodic double.                                                                                                              | 24 MHz                                                         | 3600 | 4300 | uA   |

| Operating current              | I <sub>RUN</sub>     |                                                                                                                             | 4 MHz                                                          | 550  | 750  | uA   |

|                                |                      | V <sub>CORE</sub> = 1.55 V, V <sub>DD</sub> = 3.3 V. All                                                                    | 8 MHz                                                          | 1050 | 1300 | uA   |

|                                |                      | peripheral clock sources are off. Run While(1) in Flash with RCH as                                                         | 16 MHz                                                         | 1900 | 2400 | uA   |

|                                |                      | clock source.                                                                                                               | 24 MHz                                                         | 2700 | 3300 | uA   |

|                                |                      |                                                                                                                             | 32 MHz<br>Flash Wait=1                                         | 2850 | 3000 | uA   |

| Sleep current                  | I <sub>SLP</sub>     | $V_{CORE} = 1.55 \text{ V}, V_{DD} = 1.8 \sim 3.6 \text{ V}.$                                                               | 4 MHz                                                          | 260  | 280  | uA   |

| Parameter            | Symbol                | Condition                                                                                         | Note              | Тур. | Max. | Unit |

|----------------------|-----------------------|---------------------------------------------------------------------------------------------------|-------------------|------|------|------|

|                      |                       | All peripheral clock sources are on with RCH as clock source.                                     | 8 MHz             | 500  | 520  | uA   |

|                      |                       | with NOTE as clock source.                                                                        | 16 MHz            | 950  | 970  | uA   |

|                      |                       |                                                                                                   | 24 MHz            | 1400 | 1420 | uA   |

|                      |                       |                                                                                                   | 4 MHz             | 110  | 125  | uA   |

|                      |                       | V 455VV 40 00V                                                                                    | 8 MHz             | 190  | 210  | uA   |

|                      |                       | $V_{CORE} = 1.55 \text{ V}, V_{DD} = 1.8 \sim 3.6 \text{ V}.$<br>All peripheral clock sources are | 16 MHz            | 330  | 360  | uA   |

|                      |                       | off. RCH clock source is used.                                                                    | 24 MHz            | 470  | 500  | uA   |

|                      |                       |                                                                                                   | 32 MHz            | 580  | 610  | uA   |

|                      |                       | $V_{CORE}$ = 1.55 V, $V_{DD}$ = 1.8 ~ 3.6 V.<br>All peripheral clock sources are                  | TA = -40 ~ 25 °C  | 7    | 9    | uA   |

| LP operating current | I <sub>LP-RUN</sub>   | on. Run While(1) in Flash with                                                                    | TA = 50 °C        | 7.3  | 9.2  | uA   |

|                      |                       | XTAL (32768Hz, Driver = 1) as clock source.                                                       | TA = 85 °C        | 8.9  | 11.3 | uA   |

|                      |                       | $V_{CORE}$ = 1.55V, $V_{DD}$ = 1.8 ~ 3.6 V.<br>All peripheral clock sources are                   | TA = - 40 ~ 25 °C | 6    | 8    | uA   |

|                      | I <sub>LP-RUN</sub>   | off. Run While(1) in Flash with                                                                   | TA = 50 °C        | 6.1  | 8.2  | uA   |

|                      |                       | XTAL (32768 Hz, Driver = 1) as clock source.                                                      | TA = 85 °C        | 7.7  | 10.1 | uA   |

|                      |                       | V <sub>CORE</sub> = 1.55 V, V <sub>DD</sub> = 1.8 ~ 3.6 V.<br>All peripheral clock sources are    | TA = - 40 ~ 25 °C | 3.3  | 3.5  | uA   |

|                      | I <sub>LP-SLP</sub>   | on. Run While(1) in Flash with                                                                    | TA = 50 °C        | 3.6  | 3.8  | uA   |

|                      |                       | XTAL (32768 Hz, Driver = 1) as clock source.                                                      | TA = 85 °C        | 5.4  | 5.8  | uA   |

| LP sleep current     |                       | $V_{CORE}$ = 1.55 V, $V_{DD}$ = 1.8 ~ 3.6 V.<br>All peripheral clock sources are off              | TA = - 40 ~ 25 °C | 2.2  | 2.4  | uA   |

|                      | I <sub>LP-SLP</sub>   | (except LPTimer and RTC). Run                                                                     | TA = 50 °C        | 2.5  | 2.6  | uA   |

|                      |                       | While(1) in Flash with XTAL<br>(32768Hz, Driver = 1) as clock<br>source.                          | TA = 85 °C        | 4.2  | 4.6  | uA   |

|                      |                       | $V_{CORE} = 1.55 \text{ V}, V_{DD} = 1.8 \sim 3.6 \text{ V}.$                                     | TA = - 40 ~ 25 °C | 1.5  | 1.65 | uA   |

|                      |                       | All peripheral clock sources are off, except LPTimer, WDT and                                     | TA = 50 °C        | 1.85 | 2.2  | uA   |

|                      |                       | RTC.                                                                                              | TA = 85 °C        | 3.5  | 4.2  | uA   |

|                      |                       | V 455 V V 49 26 V                                                                                 | TA = - 40 ~ 25 °C | 1.2  | 1.3  | uA   |

| Deep sleep current   | I <sub>DEEP-SLP</sub> | $V_{CORE} = 1.55 \text{ V}, V_{DD} = 1.8 \sim 3.6 \text{ V}.$<br>All peripheral clock sources are | TA = 50 °C        | 1.5  | 1.8  | uA   |

|                      |                       | off, except WDT.                                                                                  | TA = 85 °C        | 3.1  | 3.7  | uA   |

|                      |                       | Vesse = 1.55 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                  | TA = - 40 ~ 25 °C | 0.9  | 1    | uA   |

|                      |                       | $V_{CORE} = 1.55 \text{ V}, V_{DD} = 1.8 \sim 3.6 \text{ V}.$ All peripheral clock sources are    | TA = 50 °C        | 1.1  | 1.3  | uA   |

|                      |                       | off, except LPTimer.                                                                              | TA = 85 °C        | 2.6  | 3    | uA   |

| Parameter | Symbol | Condition                                                                                                 | Note              | Тур. | Max. | Unit |

|-----------|--------|-----------------------------------------------------------------------------------------------------------|-------------------|------|------|------|

|           |        | V <sub>CORE</sub> = 1.55 V, V <sub>DD</sub> = 1.8~3.6V. All peripheral clock sources are off, except RTC. | TA = - 40 ~ 25 °C | 1.0  | 1.1  | uA   |

|           |        |                                                                                                           | TA = 50 °C        | 1.2  | 1.5  | uA   |

|           |        |                                                                                                           | TA = 85 °C        | 2.6  | 3.4  | uA   |

|           |        | V -155 VV -19 26 V                                                                                        | TA = - 40 ~ 25 °C | 0.42 | 0.6  | uA   |

|           |        | $V_{CORE} = 1.55 \text{ V}, V_{DD} = 1.8 \sim 3.6 \text{ V}.$ All peripheral clock sources are            | TA = 50 °C        | 0.75 | 0.95 | uA   |

|           |        | off.                                                                                                      | TA = 85 °C        | 2.2  | 2.7  | uA   |

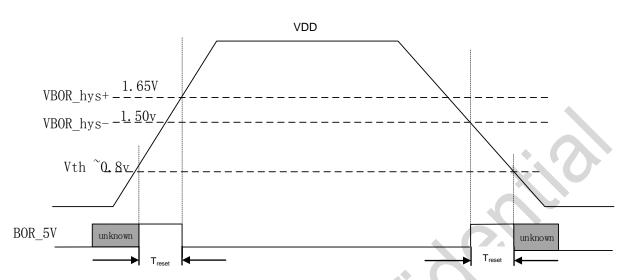

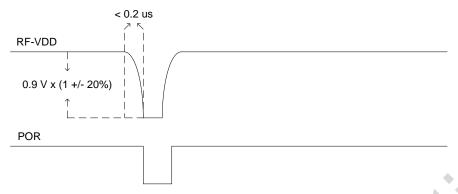

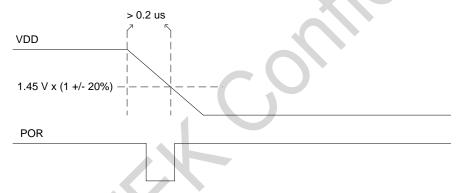

#### 1.14 POR/BOR Features

Figure 3. POR/BOR Features

#### Notes:

- 1. POR/BOR detects the VDD voltage.

- 2. It detects the threshold only instead of VDD power-up and power-down slew rate.

- 3. The detection threshold is the same no matter the VDD is powering on or off. A reset pulse is triggered when VDD is lower than the threshold.

- 4. In case a reset pulse is generated, the pulse duration will not be less than T<sub>reset</sub> to guarantee a complete system reset.

**Table 16. POR/BOR Features**

| Parameter                                                                        | Symbol    | Condition | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------|-----------|-----------|------|------|------|------|

| POR release voltage (power-up process)BOR detection voltage (power-down process) | $V_{POR}$ |           | 1.45 | 1.50 | 1.65 | V    |

## 1.15 Controller External XTH Oscillator

**Table 17. Controller External XTH Oscillator**

| Parameter                          | Symbol              | Condition                                                        | Min. | Тур. | Max. | Unit |

|------------------------------------|---------------------|------------------------------------------------------------------|------|------|------|------|

| Crystal frequency                  | F <sub>FCLK</sub>   |                                                                  | 4    |      | 32   | MHz  |

| Equivalent series                  | FOD                 | 32 MHz crystal                                                   |      | 30   | 60   | Ω    |

| resistance                         | ESR <sub>FCLK</sub> | 4 MHz crystal                                                    |      | 400  | 1500 | Ω    |

| Load capacitance                   | C <sub>FCLK</sub>   | The two pins of the crystal oscillator are connected separately. | 12   |      | 24   | pF   |

| Duty cycle                         | DC <sub>FCLK</sub>  |                                                                  | 40   | 50   | 60   | %    |

| Current consumption <sup>[1]</sup> | I <sub>DD</sub>     | 32 MHz crystal, $C_{FCLK}$ = 12 pF, $ESR_{FCLK}$ = 30 $\Omega$   |      | 600  |      | uA   |

| Startup time                       | T <sub>Fstart</sub> | 4 MHz~32 MHz                                                     | 200  |      | 400  | us   |

#### Notes:

[1]. It is the current consumption when configure XTH\_CR\_Driver = 0b1110.

## 1.16 Controller External 32.768 kHz Oscillator

Table 18. Controller External 32.768 kHz Oscillator

| Parameter                          | Symbol              | Condition                                                                   | Min. | Тур.   | Max. | Unit |

|------------------------------------|---------------------|-----------------------------------------------------------------------------|------|--------|------|------|

| Crystal frequency                  | F <sub>SCLK</sub>   |                                                                             |      | 32.768 |      | kHz  |

| Equivalent series                  | ESR <sub>SCLK</sub> |                                                                             |      | 65     | 85   | kΩ   |

| Load capacitance                   | C <sub>SCLK</sub>   | The two pins of the crystal oscillator are connected separately.            | 0    | 12     |      | pF   |

| Clock duty cycle                   | DC <sub>FCLK</sub>  |                                                                             | 40   | 50     | 60   | %    |

| Current consumption <sup>[1]</sup> | I <sub>DD</sub>     | $C_{SCLK}$ =12pF,ESR <sub>SCLK</sub> = 65k $\Omega$                         |      | 0.6    | 1    | uA   |

| Startup time                       | T <sub>start</sub>  | $C_{SCLK}$ =12pF,ESR <sub>SCLK</sub> = 65<br>k $\Omega$ ,40%~60% duty cycle |      | 500    |      | ms   |

Notes:

# 1.17 Controller Internal RCH Oscillator

Table 19. Controller Internal RCH Oscillator

| Parameter                                         | Symbol              | Condition                                                               | Min. | Тур.  | Max.  | Unit |

|---------------------------------------------------|---------------------|-------------------------------------------------------------------------|------|-------|-------|------|

|                                                   |                     |                                                                         |      | 4.0   |       |      |

| Internal high speed oscillating                   |                     |                                                                         |      | 8.0   |       |      |

| frequency                                         | F <sub>MCLK</sub>   |                                                                         | 4    | 16.0  | 32    | MHz  |

|                                                   |                     |                                                                         |      | 22.12 |       |      |

|                                                   |                     | F <sub>MCLK</sub> = 4 MHz                                               |      | 6.0   |       | us   |

| Startup time (not including software calibration) | T <sub>Mstart</sub> | F <sub>MCLK</sub> = 8 MHz                                               |      | 4.0   |       | us   |

|                                                   |                     | F <sub>MCLK</sub> = 16 MHz                                              |      | 3.0   |       | us   |

|                                                   |                     | F <sub>MCLK</sub> = 24 MHz                                              |      | 2.5   |       | us   |

|                                                   |                     | F <sub>MCLK</sub> = 4 MHz                                               |      | 80    |       | uA   |

|                                                   |                     | F <sub>MCLK</sub> = 8 MHz                                               |      | 100   |       | uA   |

| Current consumption                               | I <sub>MCLK</sub>   | F <sub>MCLK</sub> = 16 MHz                                              |      | 120   |       | uA   |

|                                                   |                     | F <sub>MCLK</sub> = 24 MHz                                              |      | 140   |       | uA   |

| Clock duty cycle                                  | DC <sub>MCLK</sub>  |                                                                         | 45   | 50    | 55    | %    |

|                                                   | DE)/                | $V_{DD} = 1.8 \sim 3.6 \text{ V},$ $TA = -40 \sim +85 ^{\circ}\text{C}$ | -2.5 |       | +2.5  | %    |

| Frequency tolerance                               | DEV <sub>MCLK</sub> | V <sub>DD</sub> = 1.8 V ~ 3.6 V,<br>TA = - 20 ~ + 50 °C                 | -2.0 |       | + 2.0 | %    |

<sup>[1].</sup> The operating current is measured under the condition at XTL\_CR\_Driver = 0b0011 and ESR=65k $\Omega$ .

## 1.18 Controller Internal RCL Oscillator

**Table 20. Controller Internal RCL Oscillator**

| Parameter                               | Symbol                                             | Condition                                          | Min.   | Тур. | Max. | Unit  |

|-----------------------------------------|----------------------------------------------------|----------------------------------------------------|--------|------|------|-------|

| Internal high speed                     | F                                                  |                                                    |        | 38.4 |      | Id I= |

| oscillating frequency                   | F <sub>ACLK</sub>                                  |                                                    | 32.768 |      | kHz  |       |

| Startup time                            | T <sub>ACLK</sub>                                  |                                                    |        | 100  |      | us    |

| Current consumption                     | I <sub>ACLK</sub>                                  |                                                    |        | 0.25 |      | uA    |

| Clock duty cycle                        | DC <sub>ACLK</sub>                                 |                                                    | 25     | 50   | 75   | %     |

| -                                       | 551                                                | V <sub>DD</sub> = 1.8 ~ 3.6V,<br>TA = -40 ~ +85 °C | -2.0   |      | +2.0 | %     |

| Frequency tolerance DEV <sub>ACLK</sub> | V <sub>DD</sub> = 1.8 ~ 3.6V,<br>TA = -20 ~ +50 °C | -1.5                                               |        | +1.5 | %    |       |

## 1.19 Controller Flash Features

**Table 21. Controller Flash Features**

| Parameter         | Symbol                 | Condition   | Min. | Тур. | Max. | Unit    |

|-------------------|------------------------|-------------|------|------|------|---------|

| Sector endurance  | EC <sub>Flash</sub>    |             | 20   |      |      | kcycles |

| Byte Program Time | T <sub>Prog</sub>      |             | 6    |      | 7.5  | us      |

| Sector erase time | т.                     |             | 4    |      | 5    | ms      |

| Chip erase time   | T <sub>Erase</sub>     |             | 30   |      | 40   | ms      |

| B i               | RET <sub>Flash</sub> - | TA = +25 °C | 20   |      |      | Year    |

| Data retention    |                        | TA = +85 °C | 10   |      |      | Year    |

## 1.20 Controller Low Power Mode Recover Time

Table 22. Controller Low Power Mode Recover Time

| Parameter                  | Symbol              | Condition                            | Min. | Тур. | Max. | Unit |

|----------------------------|---------------------|--------------------------------------|------|------|------|------|

|                            |                     | Regulated 1.5 V, TA = + 25°C, 4 MHz  |      | 4.0  |      | us   |

| Return to active mode from | T <sub>Wakeup</sub> | Regulated 1.5 V, TA = + 25°C, 8 MHz  |      | 3.1  |      | us   |

| deep sleep mode            |                     | Regulated 1.5 V, TA = + 25°C, 16 MHz |      | 2.8  |      | us   |

|                            |                     | Regulated 1.5 V, TA = + 25°C, 24 MHz |      | 2.7  |      | us   |

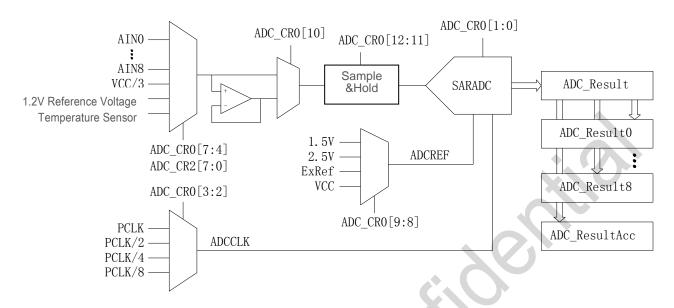

## 1.21 Controller ADC Features

Figure 4. Controller ADC Features

**Table 23. Controller ADC Features**

| Parameter                                                     | Symbol                  | Condition                                                                                                                                                | Min.  | Тур. | Max.               | Unit   |

|---------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------------------|--------|

| Input voltage range                                           | V <sub>ADCin</sub>      | Single-ended                                                                                                                                             | 0     |      | $V_{ADC\_REF\_IN}$ | V      |

| External input reference voltage                              | V <sub>ADC_REF_IN</sub> | .\_                                                                                                                                                      | 0     |      | 3.6                | V      |

| Internal 2.5V reference voltage                               | V <sub>REF_25</sub>     | $TA = 25^{\circ}C, V_{DD} = 3.3 \text{ V}$                                                                                                               | 2.475 | 2.5  | 2.525              | V      |

| Internal 1.5 V reference voltage                              | V <sub>REF_15</sub>     | $TA = 25^{\circ}C, V_{DD} = 3.3 \text{ V}$                                                                                                               | 1.485 | 1.5  | 1.515              | V      |

| Operating current (including reference source and buffer)     | l <sub>ADC1</sub>       | 200 ksps                                                                                                                                                 |       | 2    |                    | mA     |

| Operating current (not including reference source and buffer) | I <sub>ADC2</sub>       | 1000 ksps                                                                                                                                                |       | 0.5  |                    | mA     |

| Input capacitance                                             | C <sub>ADC_IN</sub>     |                                                                                                                                                          |       | 16   | 19.2               | pF     |