## NAU85L20

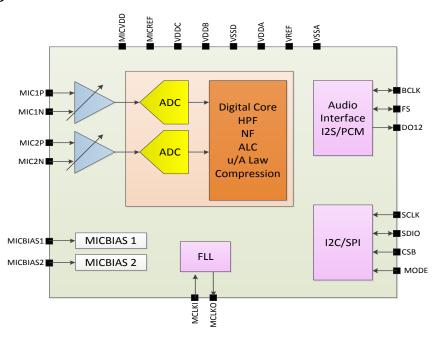

# **Dual Audio ADC with Integrated FLL and Microphone Preamplifier**

### **Description**

The NAU85L20 is a low power, high quality, 2-channel ADC for microphone array application. The NAU85L20 integrates programmable gain preamplifiers for stereo differential microphones, significantly reducing external component requirements. A fractional FLL is available to accurately generate any audio sample rate using any commonly available system clock source from 8KHz through 33MHz. Audio data can be directed to I2S data out lines.

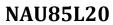

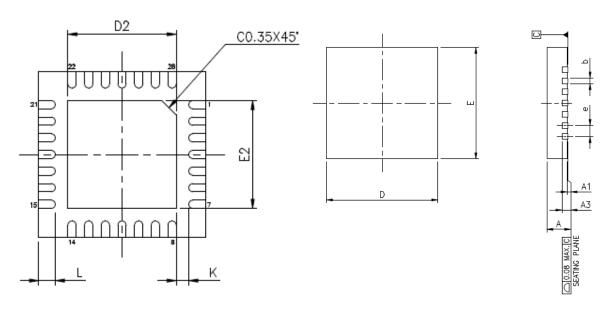

The NAU85L20 operates with analog supply voltages from 1.6V to 2V, while the digital core can operate down to 1.2V to conserve power. Internal register controls enable flexible power saving modes by powering down subsections of the chip under software control. The NAU85L20 is specified for operation from -40°C to +85°C, and is available in a 28-lead QFN package.

#### **Features**

- 101dB SNR (A-weighted) @ 0dB gain, VDDA=1.8V, Fs = 48 kHz, OSR=128x

- 91dB THD+N @ 0dB gain, 0.8Vrms in, VDDA=1.8V, Fs=48 kHz, OSR=128x

- -124dB Channel Crosstalk @ 0dB gain, 0.9Vrms in, VDDA=1.8V, Fs=48 kHz, OSR=128x

- Integrated programmable gain microphone amplifier

- On-chip FLL

- I2C Serial control interface with read/write capability

- Supports sample rates from 8 kHz to 48 kHz at 24bit resolution

- Two separate microphone bias supplies for low noise microphone biasing.

- Standard audio data bus interfaces: I2S, Left or Right justified, Two's compliment, MSB first

- 32-bit audio sub frames

- Package: Pb free 28L-QFN

- Temperature range: -40 to 85°

# **Block Diagram**

# **Table of Contents**

| BI |            | DIAGRAM                                                       | 1  |

|----|------------|---------------------------------------------------------------|----|

| ΡI | N DIAC     | GRAM                                                          | 4  |

|    | Orderir    | ng Information                                                | 4  |

| ΡI | N DES      | CRIPTION                                                      | 5  |

| ΕI | LECTR      | ICAL CHARACTERISTICS                                          | 6  |

| 1  | GE         | ENERAL DESCRIPTION                                            | ξ  |

| 2  | AN         | IALOG INPUTS                                                  | ç  |

|    | 2.1        | ADC and Digital Signal Processing                             | 10 |

|    | 2.2        | ADC Digital Block                                             | 10 |

|    | 2.2.       | 1 Input Limiter / Automatic Level Control (ALC)               | 11 |

|    | 2.2.       | 2 ADC Digital Volume Control                                  | 15 |

|    | 2.2.       | 3 ADC Programmable High Pass Filter                           | 15 |

|    | 2.2.       | 4 Programmable Notch Filter                                   | 16 |

|    | 2.3        | Audio Data Companding                                         | 16 |

|    | 2.3.       | 1 μ-law                                                       | 17 |

|    | 2.3.       | 2 A-law                                                       | 17 |

|    | 2.4        | Digital Interfaces                                            | 17 |

| 3  | PC         | OWER SUPPLY                                                   | 17 |

|    | 3.1        | Power on and off reset                                        | 17 |

|    | 3.2        | Reference Voltage Generation                                  | 18 |

|    | 3.3        | Microphone Bias Generation                                    | 19 |

| 4  | CL         | OCKING AND SAMPLE RATES                                       | 19 |

|    | 4.1        | PCM Clock Generation                                          | 21 |

|    | 4.2        | Frequency Locked Loop (FLL)                                   |    |

| 5  | CC         | ONTROL INTERFACES                                             | 24 |

|    | 5.1        | Selection of Control Mode                                     |    |

|    | 5.2        | 2-Wire-Serial Control Mode (I <sup>2</sup> C Style Interface) |    |

|    | 5.3        | 2-Wire Protocol Convention                                    |    |

|    | 5.4        | 2-Wire Write Operation                                        |    |

|    | 5.5        | 2-Wire Read Operation                                         |    |

|    | 5.6        | Digital Serial Interface Timing                               |    |

| _  | 5.7        | Software Reset                                                |    |

| 6  |            | GITAL AUDIO INTERFACE                                         |    |

|    | 6.1        | Right-Justified Audio Data                                    |    |

|    | 6.2        | Left-Justified Audio Data                                     |    |

|    | 6.3<br>6.4 | I2S Audio Data Mode  PCM A Audio Data                         |    |

|    | 6.5        | PCM B Audio Data                                              |    |

|    | 6.6        | PCM Time Slot Audio Data                                      |    |

| 7  |            | GISTER MAP                                                    |    |

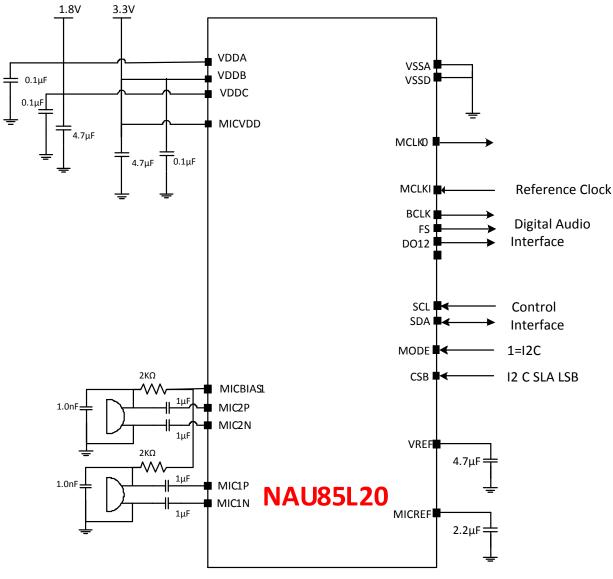

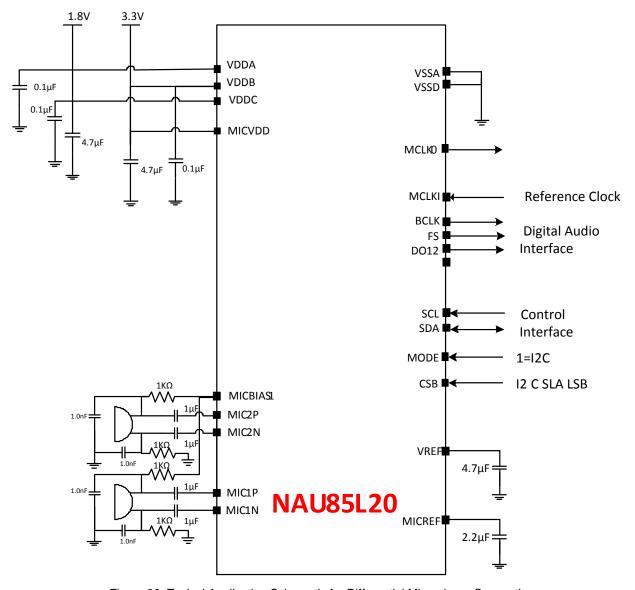

| 8  |            | PICAL APPLICATION DIAGRAM                                     |    |

| 9  |            | CKAGE INFORMATION                                             |    |

| J  | 1 /        | NOTO NOTE THAT OTNIVIZATION                                   | 40 |

| 9.1 | VERSION HISTORY      | 46 |

|-----|----------------------|----|

| 10  | ORDERING INFORMATION | 46 |

# Pin Diagram

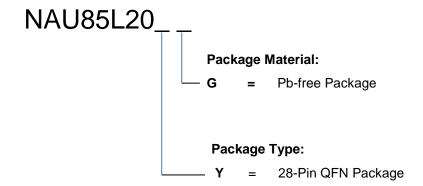

# **Ordering Information**

| Part Number | Dimension | Package | Package Material |

|-------------|-----------|---------|------------------|

| NAU85L20YG  | 4 x 4 mm  | 28 QFN  | Green            |

# **Pin Description**

| Pin# | Name       | Type           | Functionality                                       |

|------|------------|----------------|-----------------------------------------------------|

|      |            | * *            |                                                     |

| 1    | MIC2P/LIN2 | Analog Input   | MICP Input 2 / Line In Input 2                      |

| 2    | MIC2N      | Analog Input   | MICN Input 2                                        |

| 3    | VREF       | Reference      | Decoupling for Mid-rail Reference Voltage           |

| 4    | MICREF     | Analog Output  | Decoupling for MIC Reference Voltage                |

| 5    | VDDC       | Supply         | Digital Core Supply                                 |

| 6    | VSSD       | Supply         | Digital Ground                                      |

| 7    | VDDB       | Supply         | Digital Buffer (Input/Output) Supply                |

| 8    | MCLKO      | Digital Output | Output from PLL                                     |

| 9    | NC         |                |                                                     |

| 10   | DO12       | Digital Output | Digital Audio ADC Data Output for ADC 1 and 2       |

| 11   | BCLK       | Digital I/O    | Digital Audio Bit Clock                             |

| 12   | FS         | Digital I/O    | Digital Audio Frame Sync                            |

| 13   | MCLKI      | Digital Input  | Master Clock Input                                  |

| 14   | CSB        | Digital Input  | 3-Wire MPU Chip Select/I2C address LSB              |

| 15   | SCL        | Digital Input  | 3-Wire MPU Clock Input/I2C Clock (SCL)              |

| 16   | SDA        | Digital I/O    | 3-Wire MPU Data Input/I2C Data I/O (SDA)            |

| 17   | MODE       | Digital Input  | Control Interface Mode Selection Pin (I2C=1, SPI=0) |

| 18   | VDDA       | Supply         | Analog Power Supply                                 |

| 19   | VSSA       | Supply         | Analog Ground                                       |

| 20   | MIC1N      | Analog Input   | MICN Input 1                                        |

| 21   | MIC1P/LIN1 | Analog Input   | MICP Input 1 / Line In Input 1                      |

| 22   | NC         |                |                                                     |

| 23   | NC         |                |                                                     |

| 24   | MICBIAS1   | Analog Output  | Microphone Bias for Microphone ADC 1                |

| 25   | MICVDD     | Supply         | Microphone Supply                                   |

| 26   | MICBIAS2   | Analog Output  | Microphone Bias for Microphone ADC 2                |

| 27   | NC         |                |                                                     |

| 28   | NC         |                |                                                     |

# **Electrical Characteristics**

Conditions: VDDA = VDDC=1.8V, VDDB = 3.3V, MICVDD=3.3V, MCLK = 12.88MHz,  $T_A$  = +25°C, 1 kHz signal, Fs = 48 kHz, 24-bit audio data, with differential inputs unless otherwise stated.

| Symbol            | Parameter                                | Conditions                                                                                                                           | Typical | Limit | Units (Limit)    |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|-------|------------------|

|                   |                                          | V <sub>DD</sub> A in Shutdown Mode                                                                                                   | 0.5     | 1     |                  |

|                   |                                          | V <sub>DD</sub> A When V <sub>DD</sub> C=1.2V                                                                                        | 16.7    |       |                  |

| ISD               | Shutdown Current                         | V <sub>DD</sub> B                                                                                                                    | 0.2     | 1     | μA               |

|                   |                                          | V <sub>DD</sub> C                                                                                                                    | 2       | 10    |                  |

|                   |                                          | V <sub>DD</sub> MIC                                                                                                                  | 0.5     | 1     |                  |

| ADC               |                                          |                                                                                                                                      |         |       |                  |

| THD+N             | ADC Total Harmonic Distortion<br>+ Noise | Reference= @ 0dB gain, 0.8Vrms in, VDDA=1.8V, Fs=48 kHz, OSR=128x                                                                    | 91      |       | dB               |

| SNR               | Signal to Noise Ratio                    | Reference = VOUT(0dBFS), A-<br>Weighted, MIC Input, MIC Gain =<br>0dB,fs = 8KHz, Mono Differential Input                             | 100     |       | dB               |

|                   |                                          | Reference = VOUT(0dBFS), A-<br>Weighted, MIC Input, MIC Gain =<br>6dB,fs = 8KHz, Mono Differential Input                             | 98      |       | dB               |

|                   |                                          | Reference = VOUT(0dBFS), A-<br>Weighted, dual Input, Gain = 12dB,fs =<br>16KHz                                                       | 96      |       | dB               |

|                   |                                          | Reference= MIC Gain= 0dB gain, (A-<br>weighted) VDDA=1.8V, Fs = 48 kHz,<br>OSR=128x                                                  | 101     |       | dB               |

| PSRR              | Power Supply Rejection Ratio             | V <sub>RIPPLE</sub> = 200mVP_P applied to AVDD,<br>f <sub>RIPPLE</sub> = 217Hz, Input Referred,<br>MIC_GAIN = 0dB Differential Input | 65      |       | dB               |

| Xtalk             | ADC channel cross talk                   | MIC Input, MIC_GAIN = 0dB, VIN = 0.8Vrms, f=1KHz, Fs = 48KHz, Channel 1(3) to Channel 2 (4)                                          | -124    |       | dB               |

| FS <sub>ADC</sub> | ADC Full Scale Input Level               | AV <sub>DD</sub> = 1.8V                                                                                                              | 1       |       | V <sub>RMS</sub> |

| MICBIAS           | ,                                        |                                                                                                                                      |         | ı     |                  |

| V <sub>BIAS</sub> | Output Voltage                           | Programmable 2.1V to 2.8V in 0.1V Steps                                                                                              | 2.5     |       | V                |

| l <sub>OUT</sub>  | Output Current                           |                                                                                                                                      |         | 4     | mA               |

| eos               | Output Noise                             | A-weighted 20Hz-20kHz                                                                                                                | -115    |       | dBV              |

#### Notes

- 1. Full Scale input level is relative to the magnitude of VDDA and can be calculated as FS = 1V<sub>ms</sub>\*VDDA/1.8.

- 2. Distortion is measured in the standard way as the combined quantity of distortion products plus noise. The signal level for distortion measurements is at 3dB below full scale, unless otherwise noted.

- 3. Unused analog input pins should be left as no-connection.

- 4. Unused digital input pins should be tied to ground.

Tel: 1-408-544-1718 Fax: 1-408-544-1787

# Digital I/O

| Parameter              | Symbol          | Comments/Conditions |             | Min         | Max         | Units |

|------------------------|-----------------|---------------------|-------------|-------------|-------------|-------|

| Input LOW level        | VIL             | VDD                 | VDDB = 1.8V |             | 0.33 * VDDB | V     |

| mpat 2011 lovoi        | V 1L            | VDD                 | 0B = 3.3V   |             | 0.37 * VDDB | ,     |

| Input HIGH level       | V <sub>IH</sub> | VDDB = 1.8V         |             | 0.67 * VDDB |             | V     |

| mpat morniovo.         | • 10            | VDD                 | 0B = 3.3V   | 0.63 * VDDB |             | ,     |

| Output HIGH level      | V <sub>OH</sub> | I <sub>Load</sub> = | VDDB = 1.8V | 0.9 * VDDB  |             | V     |

| Guipat i ii Giri iovoi | VOH             | 1mA                 | VDDB = 3.3V | 0.95 * VDDB |             | ,     |

| Output LOW level       | Vol             | I <sub>Load</sub> = | VDDB = 1.8V |             | 0.1 * VDDB  | V     |

| 33,53, 23,410,401      | • OL            | 1mA                 | VDDB = 3.3V |             | 0.05 * VDDB | ,     |

# **Recommended Operating Conditions**

| Condition                                                       | Symbol         | Min  | Typical | Max  | Units |

|-----------------------------------------------------------------|----------------|------|---------|------|-------|

| Digital Supply Range with sample rate > 48 kHz or FLL enabled   | VDDC           | 1.62 | 1.8     | 1.98 | V     |

| Digital Supply Range with sample rate <= 48kHz and FLL disabled | VDDC           | 1.2  | 1.8     | 1.98 | V     |

| Digital I/O Supply Range                                        | VDDB           | 1.62 | 1.8     | 3.6  | V     |

| Analog Supply Range                                             | VDDA           | 1.62 | 1.8     | 1.98 | V     |

| Microphone Bias Supply Voltage                                  | VDDMIC         | 1.8  | 4.2     | 5.5  | V     |

| Temperature Range                                               | T <sub>A</sub> | -40  |         | +85  | °C    |

CAUTION: Below condition needed to be followed for regular operation: VDDB > VDDC - 0.6V

# **Absolute Maximum Ratings**

| Parameter                               | Min        | Max        | Units |

|-----------------------------------------|------------|------------|-------|

| Digital Supply Range (VDDC)             | -0.3       | 2.2        | V     |

| Digital I/O Supply Range (VDDB)         | -0.3       | 6.0        | V     |

| Analog Supply Range (VDDA)              | -0.3       | 2.2        | V     |

| Microphone Bias Supply Voltage (MICVDD) | -0.3       | 6.0        | V     |

| Voltage Input Digital Range             | VSSD - 0.3 | VDDB + 0.3 | V     |

| Voltage Input Analog Range              | VSSA - 0.3 | VDDA + 0.3 | V     |

| Junction Temperature, T <sub>J</sub>    | -40        | +150       | °C    |

| Storage Temperature                     | -65        | +150       | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods. Exposure to such conditions may adversely influence product reliability and result in failures not covered by warranty.

CAUTION: The following condition need to be followed for maximum ratings: VDDB > VDDC - 0.6V.

# 1 General Description

The NAU85L20 is a low power, high quality, 2-channel ADC for microphone array applications. There are eight analog inputs with individual input PGA gain stages and are passed to the ADC path for signal processing. A low noise microphone bias circuit supplies a programmable voltage reference for one or more electret microphones on two buffered MICBIAS outputs that are available to separately supply microphones associated with channels 1 & 2. The digital audio data from the ADC's can be processed by a Volume Control, High Pass filter, and ALC before it is passed on to the serial I2S interface. This digital serial output data can be available in separate dual channel formats on ADCOUT12 for channel 1 & 2. The device clock can be locked to an external clock reference or generated internally by the on-chip FLL. The registers that control the NAU85L20 can be programmed through standard I2C or SPI interface.

## 2 Analog Inputs

NAU85L20 has two low noise, high common mode rejection ratio analog microphone differential inputs – MIC1/MIC1P together are MIC.1, MIC2N/MIC2P together are MIC.2. Each of these microphone inputs are followed by a -1dB to 36dB PGA gain stage with a fixed 12kOhm input impedance.

All inputs are maintained at a DC bias at approximately 1/2 of the VDDA supply voltage. Connections to these inputs should be AC-coupled by means of DC blocking capacitors suitable for the device application.

The differential microphone input structure is essential in noisy digital systems where amplification of low-amplitude analog signals is necessary such as in portable digital media devices and cell phones. Differential inputs are also very useful to reduce ground noise in systems in which there are ground voltage differences between different chips and components. When properly implemented, the differential input architecture offers an improved power-supply rejection ratio (PSRR) and higher ground noise immunity.

A detailed diagram of the input PGA connections and associated registers is shown in Figure 1. The PGA inputs can also be disconnected from the amplifier for applications where the inputs are shared with other devices. In addition, there is a pre-charge circuit that can speed up charging the external coupling capacitor set with <a href="#FEPGA2.ACDC">FEPGA2.ACDC</a> CTRL REG0x6A[9:8] and <a href="#FEPGA2.ACDC">FEPGA2.ACDC</a> CTRL REG0x6A[15:14]. The PGA gain can be set from -1dB to 36dB in 1dB steps and the embedded antialiasing filter also has a single bit adjustment to shift the cut-off frequency.

A detailed register description is available in registers FEPGA1 REG0x69 to FEPGA4 REG0x6C.

### GAIN CH1 MODE CH# To ADC1 MIC1P/MIC1N Bit 0 = Anti-Aliasing Filter for Fs<=16KHz Bit 1 = MICP/MICN Disconnect from PGA Bit 3 = Shorts MICP/MICN and terminates with $12k\Omega$ GAIN CH2 differentially MIC2P/MIC2N To ADC2 Register: FEPGA1 and FEPGA2 Register: FEPGA3 and FEPGA4

**Analog MIC Input Path**

Figure 1: Analog Input Structure

## 2.1 ADC and Digital Signal Processing

The NAU85L20 has two independent high quality ADCs. These are high performance 24-bit sigma-delta converters that are suitable for a very wide range of applications. All digital processing is with 24-bit precision minimizing processing artifacts and maximizing the audio dynamic range supported by the NAU84L04.

The ADCs are supported by a wide range mixed-mode Automatic Level Control (ALC), a high pass filter, and a notch filter. All of which are optional and programmable. The high pass filter function is intended for DC-blocking or low frequency noise reduction, such as to reduce unwanted ambient noise or "wind noise" on a microphone input. The notch filter may be programmed to greatly reduce a specific frequency band or frequency, such as a 50Hz, 60Hz, or 217Hz unwanted noise. The 2-channel ADC TDM interface also provides for flexible routing options.

## 2.2 ADC Digital Block

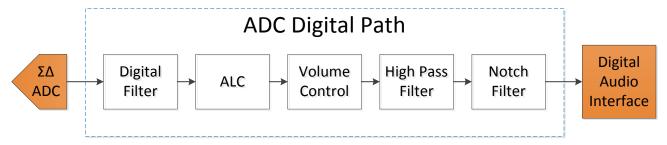

Figure 2: ADC Digital Path

The ADC digital block performs 24-bit analog-to-digital conversion and signal processing, making available a high quality audio sample stream the audio path digital interface. This block consists of a sigma-delta modulator, digital decimator/ filter, ALC, volume control, high pass filter, and a notch filter.

In order to enable the ADCs, <u>POWER\_MANAGEMENT.ADC1\_EN Reg0x01[0]</u> and <u>POWER\_MANAGEMENT.ADC2\_EN Reg0x01[3]</u> must be set to 1. The audio sample rate of the ADC is set by <u>CLOCK\_SRC.CLK\_ADC\_SRC\_REG0x03[7:6]</u>, which is derived from the MCLK. (See Section <u>CLOCKING AND SAMPLE RATES</u>).

The polarity of either ADC output signal can be changed independently on either ADC logic output which can be sometimes useful in management of the audio phase. This feature can help minimize any audio processing that may be otherwise required as the data are passed to other stages in the system. The ADC coding scheme is in twos complement format and the full-scale input level is proportional to VDDA. For example, with a 1.8V supply voltage, the full-scale level is 1.0VRMS.

### 2.2.1 Input Limiter / Automatic Level Control (ALC)

The ADC digital path of the NAU85L20 is supported by the digital Automatic Level Control (ALC) function. This can be used to automatically manage the gain to optimize the signal level at the output of the ADC by automatically amplifying input signals that are too small or decreasing the amplitude of the signals that are too loud

The ALC monitors the output of the ADC, measured after the digital decimator. The ADC output is fed into a peak detector, which updates the measured peak value whenever the absolute value of the input signal is higher than the current measured peak. The measured peak gradually decays to zero unless a new peak is detected, allowing for an accurate measurement of the signal envelope. The peak value is then used by a logic algorithm to determine whether the gain should be increased, decreased, or remain the same.

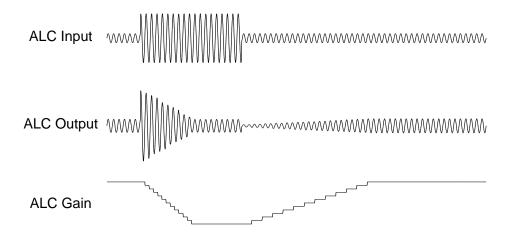

In normal mode, when sudden peaks occur above the desired gain settings, the ALC reduces volume at a register determined rate and step size. This continues until the output level of the ADC is again at the desired target level. If the input signal suddenly becomes quiet, the ALC increases volume at a register determined rate and step size until the output level from the ADC reaches the target level. If the input gain stays within the target level, the ALC will remain in a steady state.

In addition to the normal operation mode, the ALC may be operated in a special limiter mode that functions similarly to the normal mode but with faster attack times. This mode is primarily used to quickly ramp down signals that are too loud.

#### 2.2.1.1 ALC Peak Limiter Function

Both normal and limiter mode include a peak limiter function. This implements an emergency gain reduction when the ADC output level exceeds a set gain value. When the ADC output exceeds 87.5% of full scale, the ALC block ramps down the gain at the maximum ALC Attack Time rate. This is regardless of the mode and attack rate settings. This continues until the ADC output level has been reduced to below the emergency limit threshold. This action limits ADC clipping if there is a sudden increase in the input signal level.

### 2.2.1.2 ALC Parameter Definitions

- ALC Maximum Gain (ALCMAX): This sets the maximum allowed gain during normal mode ALC operation. In the Limiter mode of ALC operation, the ALCMXGAIN value is not used, instead, the maximum gain allowed is set equal to the pre-existing gain value that was in effect at the moment in time that the Limiter mode is enabled. See ALC\_CONTROL\_2 REG0x21 for details.

- ALC Minimum Gain (ALCMIN): This sets the minimum allowed gain during all modes of ALC operation. This is useful to keep the ALC operating range close to the desired range for a given application scenario. See <a href="ALC CONTROL 2 Reg0x21">ALC CONTROL 2 Reg0x21</a> for details.

- ALC Target Value (ALCLVL): Determines the value used by the ALC logic decisions comparing this fixed value with the output of the ADC. This value is expressed as a fraction of Full Scale (FS) output from the ADC. Depending on the logic conditions, either the output value used in the comparison may be the instantaneous value of the ADC, or a time weighted average of the ADC peak output level. See <a href="ALC\_CONTROL\_2 Reg0x21">ALC\_CONTROL\_2 Reg0x21</a> for details.

- ALC Attack Time (ALCATK): Attack time refers to how quickly a system responds to an increasing volume level that is greater than some defined threshold. Typically, attack time is much faster than decay time. In the NAU85L20, when the absolute value of the ADC output exceeds the ALC Target Value, the gain

will be reduced at a step size and rate determined by this parameter. When the peak ADC output is at least 1.5dB lower than the ALC Target Value, the stepped gain reduction will halt. See ALC\_CONTROL\_3 REG0x22 for details.

ALC Decay Time (ALCDCY): Decay time refers to how quickly a system responds to a decreasing volume level. Typically, decay time is much slower than attack time. When the ADC output level is below the ALC Target value by at least 1.5dB, the gain will increase at a rate determined by this parameter. In Limiter mode, the time constants are faster than in ALC mode. See <a href="ALC\_CONTROL\_3 REG0x22">ALC\_CONTROL\_3 REG0x22</a> for details.

ALC Hold Time (ALCHLD): Hold time refers to the duration of time when no action is taken. This is typically to avoid undesirable sounds that can happen when an ALC responds too quickly to a changing input signal. In the NAU85L20, the hold time value is the duration of time that the ADC output peak value must be less than the target value before there is an actual gain increase. See <a href="ALC CONTROL 2 REG0x21">ALC CONTROL 2 REG0x21</a> for details.

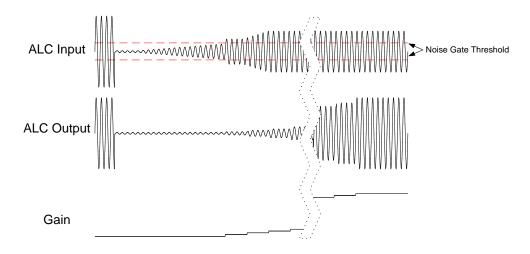

Figure 3: ALC Operation

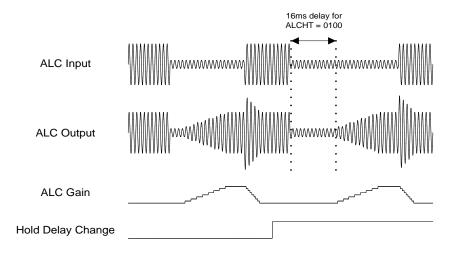

### 2.2.1.3 ALC Normal Mode Example Using ALC Hold Time Feature

Input signals with different characteristics (e.g., voice vs. music) may require different settings for this parameter for optimum performance. Increasing the ALC hold time prevents the ALC from reacting too quickly to brief periods of silence such as those that may appear in music recordings. Having a shorter hold time may be useful in voice applications where a faster reaction time helps to adjust the volume setting for speakers with different volumes. The waveform below shows the operation of the <a href="https://dx.doi.org/10.1016/j.cc.ncm/">ALC\_CONTROL\_2.ALCHLD REG0x21[7:4]</a> parameter.

Figure 4: ALC using Hold time

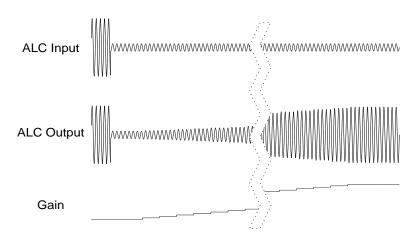

### 2.2.1.4 Noise Gate (Normal Mode Only)

A noise gate threshold prevents ALC amplification of noise when there is no input signal or no signal above an expected background noise level. The noise gate is enabled by setting <a href="ALC\_CONTROL\_1.ALC\_NGEN\_REG0x20[4">ALC\_CONTROL\_1.ALC\_NGTH REG0x20[3:0]</a>. When there is no signal or a very quiet signal (pause) composed mostly of noise, the ALC holds the gain constant instead of amplifying the signal towards the target threshold. The NAU85L20 accomplishes this by comparing the input signal level against the noise gate threshold. The noise gate only operates in conjunction with the ALC and only in Normal mode.

Figure 5: ALC without Noise gate

Figure 6: ALC with noise gate

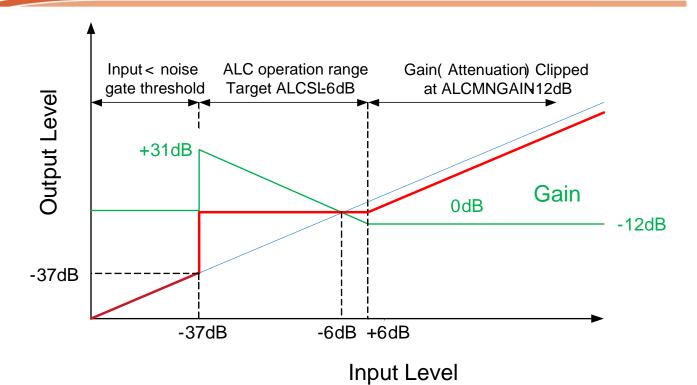

### 2.2.1.5 ALC Example with ALC Min/Max Limits and Noise Gate Operation

The drawing below shows the effects of ALC operation over the full scale signal range. The drawing is color coded as follows:

Blue Original Input signal (linear line from zero to maximum)

Green PGA gain value over time (inverse to signal in target range)

Red Output signal (held to a constant value in target range)

| <u>Registe</u> r | Bits  | <u>Name</u> | <u>Value</u> | <u>Descriptio</u> n      |

|------------------|-------|-------------|--------------|--------------------------|

| 22               | 12-15 | ALCCH(1-4)E | 1111         | ALC enabled all channels |

| 21               | 12-14 | ALCMAXGAIN  | 111          | Max ALC gain@ 35.25dB    |

| 21               | 8-10  | ALCMINGAIN  | 000          | Min ALC gain@-12dB       |

| 21               | 0-3   | ALCLVL      | 1011         | Target ALC gain@-6dBFS   |

| 20               | 4     | NGEN        | 1            | Noise gate enabled       |

0100

Noise gate@-37dB

Figure 7: ALC Response Envelope

### 2.2.2 ADC Digital Volume Control

20

0-3

The effective output audio volume of each ADC can be changed from +36dB through -128dB in 0.125dB steps using the digital volume control feature. Included in the volume control is a "digital mute" value that will completely mute the signal output of the ADC.

In addition, the ADC has an analog gain control, which can be set from -1dB to 36dB.

**NGTH**

Registers <u>DIGITAL\_GAIN\_CH1 REG0x40</u> and <u>DIGITAL\_GAIN\_CH REG0x43</u> control the digital gain of each channel. These registers can also select the ADC source of each output channel.

#### 2.2.3 ADC Programmable High Pass Filter

A high pass filter in the digital output path optionally supports each ADC. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.com/her-supports-each-ADC">https://example.com/her-supports-each-ADC</a>. The High Pass filter can be enabled by setting <a href="https://example.

The high pass filter has two different operating modes. In the audio mode, the filter is a simple first order DC blocking filter, with a cut-off frequency of 3.7Hz. In the application specific mode, the filter is a second order audio frequency filter, with a programmable cut-off frequency. The cutoff frequency of the high pass filter is scaled depending on the sampling frequency indicated to the system by the setting in register ADC SAMPLE RATE.SMPL RATE REG0x3A[7:5].

The following table provides the exact cutoff frequencies with different sample rates. These cutoff frequencies can be selected by setting <a href="https://example.com/her-file-example-rates">her-file-example rates</a>. These cutoff frequencies can be selected by setting <a href="https://example.com/her-file-example-rates">her-file-example rates</a>. These cutoff frequencies with different sample rates. These cutoff frequencies can be selected by setting <a href="https://example.com/her-file-example-rates">her-file-example rates</a>. These cutoff frequencies can be selected by setting <a href="https://example.com/her-file-example-rates">her-file-example rates</a>. These cutoff frequencies can be selected by setting <a href="https://example.com/her-file-example-rates">her-file-example rates</a>. The selected by setting <a href="https://example-example-rates">her-file-example rates</a>. The selected by setting <a href="https://example-example-rates">her-file-example-example-rates</a>. The selected by setting <a href="https://example-example-rates">her-file-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-example-

|         | SMPL_RATE REG0x3A[7:5] in kHz (FS) |            |     |     |            |     |            |      |     |

|---------|------------------------------------|------------|-----|-----|------------|-----|------------|------|-----|

| HPF_CUT |                                    | 101 or 100 | )   | (   | 011 or 010 | D   | 001 or 000 |      |     |

|         | 8                                  | 11.025     | 12  | 16  | 22.05      | 24  | 32         | 44.1 | 48  |

| 000     | 82                                 | 113        | 122 | 82  | 113        | 122 | 82         | 113  | 122 |

| 001     | 102                                | 141        | 153 | 102 | 141        | 153 | 102        | 141  | 153 |

| 010     | 131                                | 180        | 156 | 131 | 180        | 156 | 131        | 180  | 156 |

| 011     | 163                                | 225        | 245 | 163 | 225        | 245 | 163        | 225  | 245 |

| 100     | 204                                | 281        | 306 | 204 | 281        | 306 | 204        | 281  | 306 |

| 101     | 261                                | 360        | 392 | 261 | 360        | 392 | 261        | 360  | 392 |

| 110     | 327                                | 450        | 490 | 327 | 450        | 490 | 327        | 450  | 490 |

| 111     | 408                                | 563        | 612 | 408 | 563        | 612 | 408        | 563  | 612 |

Table 1: High Pass Filter Cut-off Frequencies in Hz (with HPF AM = 1)

### 2.2.4 Programmable Notch Filter

A notch filter in the digital output path optionally supports each ADC. The notch filter is used to stop a very narrow band of frequencies around a center frequency. This function can be enabled by setting NFEN in <a href="MOTCH\_FIL1\_CH1.NFEN Reg0x30[14]">NOTCH\_FIL1\_CH1.NFEN Reg0x30[14]</a>, and <a href="MOTCH\_FIL1\_CH1.NFA1 Reg0x30[13:0]">NOTCH\_FIL1\_CH1.NFA1 Reg0x30[13:0]</a>, and <a href="MOTCH\_FIL1\_CH.NFA1 Reg0x36[13:0]">NOTCH\_FIL1\_CH.NFA1 Reg0x30[13:0]</a> with two's compliment coefficient values calculated using Table 2 as shown below.

It is important to note that the register update bits are write-only bits. The update bit function is important so that all filter coefficients actively being used are changed simultaneously; even though the register values must be written sequentially. When there is a write operation to any of the filter coefficient settings, but the update bit is not set (value = 0), the value is stored as pending a future update, but does not go into effect. When there is a write operation to any coefficient register, and the update bit is set (value = 1), then the new value in the register being written is immediately put into effect, and any other pending coefficient value is put into effect at the same time.

| A <sub>0</sub>                                                          | <b>A</b> <sub>1</sub>                    | Notation                                                                                      | Register Value (DEC)                                                                                                                                       |

|-------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{1 - \tan \frac{2\pi f_b}{2f_s}}{1 + \tan \frac{2\pi f_b}{2f_s}}$ | $-(1+A_0)\times\cos\frac{2\pi f_c}{f_s}$ | $f_c$ = center frequency (Hz)<br>$f_b$ = -3dB bandwidth (Hz)<br>$f_s$ = sample frequency (Hz) | NFCA0 = $-A_0 \times 2^{13}$<br>NFCA1 = $-A_1 \times 2^{12}$<br>Note: Values are rounded to the nearest<br>whole number and converted to 2's<br>complement |

Table 2: Equations to calculate notch filter coefficients

## 2.3 Audio Data Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates, using non-linear algorithms. The NAU85L20 supports the two main telecommunications companding

Nuvoton Technology Corporation America Tel: 1-408-544-1718 Fax: 1-408-544-1787 Rev. 0.1.9: May 10, 2016

standards: A-law and μ-law. The A-law algorithm is primarily used in European communication systems and the μ-law algorithm is primarily used by North America, Japan, and Australia.

Companding converts 13 bits ( $\mu$ -law) or 12 bits (A-law) to 8 bits using non-linear quantization. The companded signal is an 8bit word containing sign (1-bit), exponent (3-bits) and mantissa (4-bits)

Following are the data compression equations set in the ITU-T G.711 standard and implemented in the NAU85L20.

### 2.3.1 μ-law

$$F(x) = \frac{\ln(1 + \mu \times |x|)}{\ln(1 + \mu)},$$

$$\mu = 255$$

### 2.3.2 A-law

$$F(x) = \frac{A \times |x|}{(1 + \ln(A))}, \qquad x \le \frac{1}{A}$$

$$F(x) = \frac{(1 + \ln(A \times |x|))}{(1 + \ln(A))}, \qquad \frac{1}{A} \le x \le 1$$

$$A = 87.6$$

When companding is enabled, the PCM interface must be set to an 8-bit word length by setting <a href="PCM\_CTRL0.CMB8 Reg0x10[10]">PCM\_CTRL0.CMB8 Reg0x10[10]</a>. When in 8-bit mode, the Register word length controls in <a href="PCM\_CTRL0.WLEN Reg0x10[3:2]">PCM\_CTRL0.WLEN Reg0x10[3:2]</a> are ignored.

# 2.4 Digital Interfaces

Command and control of the device is accomplished using a 2-wire/3-wire serial control interface. This simple, but highly flexible, interface is compatible with many commonly used command and control serial data protocols and host drivers. See **CONTROL INTERFACES** for more detail.

Digital audio input/output data streams are transferred to and from the device separately for command and control. The digital audio data interface supports either I2S or PCM audio data protocols, and is compatible with commonly used industry standard devices that follow either of these two serial data formats. See DIGITAL AUDIO INTERFACE for more detail.

# 3 Power Supply

The NAU85L20 has been designed to operate reliably using a wide range of power supply conditions and power-on/power-off sequences. However, because of existence of ESD protection diodes between the supplies, that will have impact on the application of the supplies. Because of these diodes, the following conditions need to be met:

VDDMIC > VDDA-1.2V and VDDB > VDDC - 0.6V.

#### 3.1 Power on and off reset

The NAU85L20 includes a power on and off reset circuit on chip. The circuit resets the internal logic control at VDDC and VDDA supply power up and this reset function is automatically generated internally when power supplies are too low for reliable operation. The reset threshold is approximately 0.55Vdc and 1.0Vdc for

VDDA. It should be noted that these values are much lower than the required voltage for normal operation of the chip.

The reset is held on while the power levels for both VDDC and VDDA are below their respective thresholds. Once the power levels rise above their thresholds, the reset is released. Once the reset is released, the registers are ready to be written to. It is also important to note that all the registers should be kept in their reset state for at least 6µs.

An additional internal RC filter based circuit is added which helps the circuit respond for fast ramp rates (~10µs) and generate the desired reset period width (~10µs at typical corner). This filter is also used to eliminate supply glitches which can generate a false reset condition, typically 50ns.

For reliable operation, it is recommended to write to register <a href="SW\_RESET Reg0x00">SW\_RESET Reg0x00</a> upon power up. This will reset all registers to the known default state.

Note that when VDDA and/or VDDC are below the power on reset threshold, then the digital IO pins will go into a tri-state condition.

#### **Application Notes:**

VDDA ramp up time for a guaranteed power on reset needs to be less than 50msec. The VDDA ramp down time for a guaranteed power off reset needs to be less than 125msec. If the ramp down rate is too slow (no pull down), then we can enable the minimum VREF impedance by <a href="VMID\_CTRL.VMIDSEL">VMID\_CTRL.VMIDSEL</a> REG0X66[5:4]=11 with <a href="VMID\_CTRL.VMIDEN REG0X66[6]=1">VMID\_CTRL.VMIDEN REG0X66[6]=1</a>, before shutdown in order to discharge VDDA quickly.

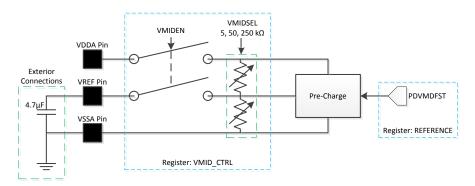

### 3.2 Reference Voltage Generation

The NAU85L20 includes a mid-supply reference circuit that is decoupled to VSS through the VREF pin by means of a bypass capacitor. The VREF voltage is used as the reference for the majority of the circuits inside NAU85L20. Therefore, the bypass capacitor needs to be large in order to achieve good power supply rejection at low frequencies. Typically, a 4.7uF capacitor can be used. However, a larger value can be chosen but it will increase the rise time of VREF and therefore it will delay the valid line output signal. However, a pre-charge circuit can pre-charge the capacitor close to VDDA/2 at power up in order to reduce the rise time for fast line out availability. This bypass capacitor should also be low leakage due to the high impedance nature of the VREF pin

The VREF voltage can be enabled by setting <a href="VMID\_CTRL.VMIDEN Reg0x60[6">VMID\_CTRL.VMIDEN Reg0x60[6</a>]. Once VREF has been enabled, the voltage will quickly ramp up due to the pre-charge circuit. The pre-charge circuit can then be disabled in order to save power or to prevent it from adjusting the VREF voltage when the supply varies. This can be done by setting <a href="REFERENCE.PDVMDFST Reg0x68[13]">REFERENCE.PDVMDFST Reg0x68[13]</a> to 1. Once the VREF voltage has settled to VDDA/2, the output impedance on the VREF pin is determined by setting the bits <a href="VMID\_CTRL.VMIDSEL">VMID\_CTRL.VMIDSEL</a> <a href="REg0x60[5:4">REg0x60[5:4]</a>. The output impedance is set as per the following table.

| VMIDSEL<br>REG0x60[5:4] | VREF Resistor Selection    | VREF Impedance               |

|-------------------------|----------------------------|------------------------------|

| 00                      | Open, no resistor selected | Open, no impedance installed |

| 01                      | 50kOhm                     | 25kOhm                       |

| 10                      | 250kOhm                    | 125kOhm                      |

| 11                      | 5kOhm                      | 2.5kOhm                      |

Table 3: V<sub>REF</sub> Impedance

Figure 8: V<sub>REF</sub> Circuitry

## 3.3 Microphone Bias Generation

The NAU85L20 provides two microphone bias pins which can be used in various stereo applications. The microphone bias can be used to power electret microphones. In order to ensure safe operation of the device, it is recommended that the microphones do not draw more than 4mA of current from each MICBIAS pin. Register MIC\_BIAS REG0x67 provides the control for powering up the MICBIAS circuitry. It should be noted that the two MICBIAS outputs both have the same voltage level.

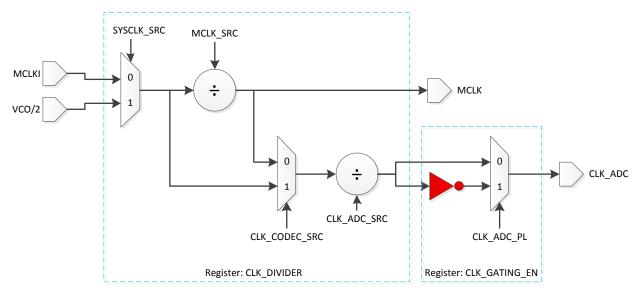

# 4 Clocking and Sample Rates

The internal clocks for the NAU85L20 are derived from a common internal clock source, MCLK. This clock is the reference for the ADCs and DSP core functions, digital audio interface and other internal functions.

MCLK can be derived directly from MCLKI pin or may be generated from a Frequency Locked Loop (FLL) using MCLKI, BCLK or FS as a reference. The FLL provides additional flexibility for a wide range of MCLK frequencies and can be used to generate a free-running clock in the absence of an external reference source. See FREQUENCY LOCKED LOOP (FLL)

for further details.

It should be noted that the internal clock frequency MCLK must be running at 256\*Fs (Fs = sample rate in Hz) in order to achieve the best performance. For example, when targeting 48 kHz sample rate audio, the MCLK must be set to 256\*48k = 12.288MHz. When the input clock MCLKI is higher than this speed, <a href="CLOCK\_SRC.MCLK\_SRC Reg0x03[4:0]">CLOCK\_SRC.MCLK\_SRC Reg0x03[4:0]</a> provides flexible division selection to meet the requirement.

Figure 9: Clock Generation

| Bits | MCLK_SRC<br>REG0x03[4:0] |

|------|--------------------------|

| 0000 | Divide by 1              |

| 0001 | Invert                   |

| 0010 | Divide by 2              |

| 0011 | Divide by 4              |

| 0100 | Divide by 8              |

| 0101 | Divide by 16             |

| 0110 | Divide by 32             |

| 0111 | Divide by 3              |

| 1001 | Invert                   |

| 1010 | Divide by 6              |

| 1011 | Divide by 12             |

| 1100 | Divide by 24             |

Table 4: CLOCK SRC.MCLK SRC REG0x03[4:0] Register Settings

| Bits | CLK_ADC_SRC<br>REG0x03[7:6] |

|------|-----------------------------|

| 00   | Divide by 1                 |

| 01   | Divide by 2                 |

| 10   | Divide by 4                 |

| 11   | Divide by 8                 |

Table 5: CLOCK SRC.CLK ADC SRC REG0x03[7:6] Register Settings

The OSR (over sampling rate) is defined as CLK\_ADC frequency divided by the audio sample rate.

$$OSR = \frac{CLK\_ADC}{Fs}$$

Available over-sampling rates are 32, 64, 128 or 256 as set in the <u>ADC\_SAMPLE\_RATE.OSR</u>

<u>REG0x3A[1:0]</u> register. CLK\_ADC frequency is set by <u>CLOCK\_SRC.CLK\_CODEC\_SRC REG0x03[13]</u> and <u>CLOCK\_SRC.CLK\_ADC\_SRC REG0x03[7:6]</u> registers.

It should be noted that the OSR and Fs must be selected so that the max frequency of CLK\_ADC is less than 6.144MHz. When CLK\_ADC is determined, <u>ADC SAMPLE RATE.OSR REG0x3A[1:0]</u> should be set to provide appropriate down sampling through digital filters.

#### Example 1:

To configure Fs = 48 kHz, MCLK = (256\*Fs) = 12.288MHz, and CLK\_ADC = 6.144MHZ Set:

CLOCK\_SRC.CLK\_CODEC\_SRC REG0x03[13] = 1'b0, CLOCK\_SRC.CKL\_ADC\_SRC REG0x03[7:6] = 2'b01, and OSR = 2'b10 (128)

#### Example 2:

To configure Fs = 16 kHz, MCLKI = 12.288MHz, and CLK\_ADC = 4.096MHz

Set:

- CLOCK SRC.MCLK SRC REG0x03[4:0] = 3'b111 (Divide MCLKI by 3) to get MCLK = (256\*Fs) = 4.096MHz

- CLOCK SRC.CLK CODEC SRC REG0x03[13] = 1'b0, CLOCK SRC.CLK ADC SRC REG0x03[7:6] = 2'b00, and OSR = 2'b11 (256)

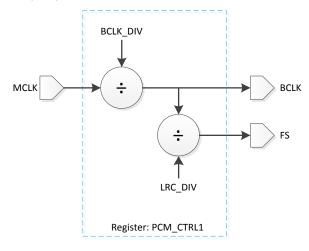

### 4.1 PCM Clock Generation

In master mode, BCLK is derived from MCLK via a programmable divider set by <a href="PCM\_CTRL1.BCLK\_DIV">PCM\_CTRL1.BCLK\_DIV</a>

<a href="REG0x11">REG0x11">REG0x11"</a>[13:12].</a>

To select specific Fs values, <u>PCM\_CTRL1.BCLK\_DIV\_REG0x11[2:0]</u> and <u>PCM\_CTRL1.LRC\_DIV\_REG0x11[13:12]</u> must be set according to the block diagram seen in Figure 10 and the equation below.

$BCLK = Fs \times data\ length \times channels$

#### Example 1:

If we want an Fs of 48 kHz and 16 bit data is to be sent to the I2S bus (2 channel)

- BCLK = 48000\*16\*2 = 1.536MHz and MCLK = 48000\*256 = 12.288MHz

- Set PCM\_CTRL1.BCLK\_DIV REG0x11[2:0] = 3'b011 (8) and PCM\_CTRL1.LRC\_DIV REG0x11[13:12] = 2'b11 (32)

Or 32 bit data is to be sent

- BCLK = 48000\*32\*2 = 3.073MHz and MCLK = 48000\*256 = 12.288MHz

- Set <u>PCM\_CTRL1.BCLK\_DIV REG0x11[2:0]</u> = 3'b010 (4) and <u>PCM\_CTRL1.LRC\_DIV REG0x11[13:12]</u> = 2'b10 (64)

#### Example 2:

If we want an Fs of 16 kHz and 16 bit data is to be sent to the I2S bus (2 channel)

- BCLK = 16000\*16\*2 = 512kHz and MCLK = 16000\*256 = 4.096MHz

- Set <u>PCM\_CTRL1.BCLK\_DIV Reg0x11[2:0]</u> = 3'b011 (8) and <u>PCM\_CTRL1.LRC\_DIV Reg0x11[13:12]</u> = 2'b11 (32)

32 bit data is to be sent,

- BCLK = 16000\*32\*2 = 1.024MHz and MCLK = 16000\*256 = 4.096MHz

- Set <u>PCM\_CTRL1.BCLK\_DIV Reg0x11[2:0]</u> = 3'b100 (4) and <u>PCM\_CTRL1.LRC\_DIV Reg0x11[13:12]</u> = 2'b10 (64)

#### Example 3:

If we want an Fs of 16 kHz and 32 bit data is to be sent to the I2S TDM bus (4 channels)

- BCLK = 16000\*32\*4 = 2.048MHz and MCLK = 16000\*256 = 4.096MHz

- Set <u>PCM\_CTRL1.BCLK\_DIV Reg0x11[2:0]</u> = 3'b001 (2) and <u>PCM\_CTRL1.LRC\_DIV</u>

#### REG0x11[13:12] = 2'b01 (128)

Figure 10: Master Mode PCM Clock Generation

| Bits | BCLK_DIV<br>REG0x11[2:0] |

|------|--------------------------|

| 000  | Divide by 1              |

| 001  | Divide by 2              |

| 010  | Divide by 4              |

| 011  | Divide by 8              |

| 100  | Divide by 16             |

| 101  | Divide by 32             |

Table 6: PCM\_CTRL1.BCLK\_DIV REG0x11[2:0] Register Settings

| Bits | LRC_DIV<br>REG0x11[13:12] |

|------|---------------------------|

| 00   | Divide by 256             |

| 01   | Divide by 128             |

| 10   | Divide by 64              |

| 11   | Divide by 32              |

Table 7: PCM\_CTRL1.LRC\_DIV REG0x11[13:12] Register Settings

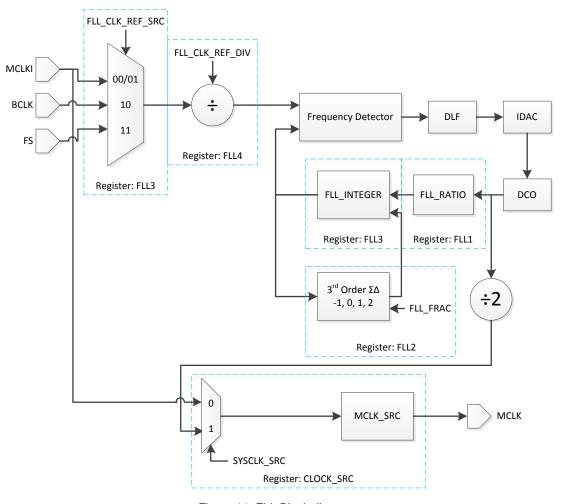

## 4.2 Frequency Locked Loop (FLL)

The integrated FLL can be used to generate a master system clock, MCLK, from MCLKI, BCLK or FS as a reference. Because of the FLL's tolerance of jitter, it may be used to generate a stable MCLK from less stable input clock sources or it can be used to generate a free-running clock in the absence of an external reference clock source. To run as a free running clock, enable <a href="FLL6.DCO">FLL6.DCO</a> EN REG0x09[15] and set <a href="FLL VCO\_RSV.DOUT2VCO\_RSV REG0x0A[15:0]">FLL6.DCO</a> EN REG0x0A[15:0]</a> to 16'hF13C.

The FLL is enabled using <a href="CLOCK\_SRC.SYSCLK\_SRC Reg0x03">CLOCK\_SRC.SYSCLK\_SRC Reg0x03</a>[15] and it is recommended that the FLL be disabled before any setting changes via <a href="CLOCK\_SRC.SYSCLK\_SRC Reg0x03">CLOCK\_SRC.SYSCLK\_SRC Reg0x03</a>[15] and then re-enabled after the register settings have been updated. To select between sources, use <a href="FLL3.FLL\_CLK\_REF\_SRC">FLL3.FLL\_CLK\_REF\_SRC</a>[Reg0x06</a>[11:10] and use <a href="FLL4.FLL\_CLK\_REF\_DIV Reg0x07">FLL4.FLL\_CLK\_REF\_DIV Reg0x07</a>[11:10] to divide the reference source by 1, 2, 4 or 8 to bring the frequency down to 13.5MHz or below.

To control the internal gain loop of the FLL, <u>FLL3.GAIN\_ERR REG0x06[15:13]</u> and <u>FLL4.FLL\_REF\_DIV\_4CHK REG0x07[14:12]</u> can be used. However, it is recommended that only the default settings be used in these registers.

Figure 11: FLL Block diagram

The FLL output frequency is determined by the following parameters:

- FLL1.FLL\_RATIO REG0x04[6:0]

- CLOCK SRC.MCLK SRC REG0x03[4:0]

- FLL3.FLL\_INTEGER REG0x06[9:0]

- FLL2.FLL\_FRAC REG0x05[15:0]

- FREF is the output of <u>FLL4.FLL\_CLK\_REF\_DIV REG0x07[]</u>

To determine these settings, the following output frequency equations are used:

- 1. FDCO = FREF x FLL\_INTEGER REG0x06[9:0] . FLL\_FRAC REG0x05[15:0] x FLL\_RATIO REG0x04[6:0]

- 2.  $MCLK = (FDCO \times MCLK\_SRC Reg0x03[4:0])/2$

Where FREF is the reference clock frequency, MCLK is the desired system clock frequency, and FDCO is the frequency of DCO in decimal. It should also be noted that the values in the above equations are the decimal values of the registers.

### Example:

If the reference frequency (FREF) is 12MHz, the desired sampling rate (Fs) is 48 kHz, and MCLK = 256\*Fs, what are the output frequency parameters?

Using these requirements, the following can be determined.

- MCLK = 256 x 48kHz = 12.288MHz

- Using Equation 2:

- FDCO = (2 x 12.288MHz) / MCLK SRC

- For FDCO to remain between 90MHz 100MHz, MCLK\_SRC must be chosen to be 1/4. This and other values for MCLK\_SRC REG0x03[4:0] can be seen on the register tables.

- $\circ$  FDCO =  $(2 \times 12.288MHz) / (1/4) = 98.304MHz$

- Using Equation 1:

- FLL\_INTEGER REG0x06[9:0] . FLL\_FRAC REG0x05[15:0] = FDCO / (FREF x FLL\_RATIO REG0x04[6:0])

- FLL\_RATIO REG0x04[6:0] = 1 because FREF ≥ 512 kHz. This and other values for FLL\_RATIO REG0x04[6:0] can be seen on the register tables.

- $\frac{\text{FLL\_INTEGER Reg0x06[9:0]}}{8.192} \cdot \frac{\text{FLL\_FRAC Reg0x05[15:0]}}{8.192} = 98.304 \text{MHz} / (12 \text{MHz} \times 1) = 8.192$

- FLL\_INTEGER Reg0x06[9:0] . FLL\_FRAC Reg0x05[15:0] represents an integer and fractional number in decimal

- o FLL\_INTEGER REG0x06[9:0] = 8

- FLL FRAC REG0x05[15:0] = 0.192

- Now retrieve or convert the parameter values into their corresponding HEX values

- FLL\_RATIO REG0x04[6:0] = 7'h1 (this value is taken from the register chart for FREF ≥ 512kHz)

- MCLK SRC REG0x03[4:0] = 4'h3 (this value is taken from the register chart for MCLK\_SRC REG0x03[4:0] = 1/4)

- FLL\_INTEGER REG0x06[9:0] = 8 = 10'h8

- o <u>FLL\_FRAC Reg0x05[15:0]</u> = 0.192 × 2<sup>16</sup> = 12583=16'h3126

If low power consumption is required, then FLL settings must be chosen where <u>FLL\_INTEGER</u> <u>REG0x06[9:0]</u>. <u>FLL\_FRAC REG0x05[15:0]</u> is an integer (i.e. <u>FLL\_FRAC REG0x05[15:0]</u> = 0). In this case, the fractional mode can be turned off by disabling register setting <u>FLL6.SDM EN REG0x09[14]</u>.

### **5** Control Interfaces

### **5.1** Selection of Control Mode

The NAU85L20 features include a serial control bus that provides access to all of the device control registers. This bus may be configured either as a 2-wire interface that is interoperable with industry standard implementations of the I2C serial bus, or as a 3-wire bus compatible with commonly used industry implementations of the SPI (Serial Peripheral Interface) bus.

Mode selection is accomplished by means of combination of the MODE control logic pin and <a href="MISC\_CTRL.SPI3\_EN Reg0x51[15]">MISC\_CTRL.SPI3\_EN Reg0x51[15]</a>. The following table shows the three functionally different modes that are supported.

| MODE Pin | SPI3 EN<br>Reg0x51[15] | Description                               |

|----------|------------------------|-------------------------------------------|

| 1        | Х                      | 2-Wire Interface, Read/Write operation    |

| 0        | 0                      | SPI Interface 3-Wire Write-only operation |

Table 8: Control Interface Selection

The timing in all three bus configurations is fully static resulting in good compatibility with standard bus interfaces and software simulated buses. A software simulated bus can be very simple and low cost, such as by utilizing general purpose I/O pins on the host controller and software "bit banging" techniques to create the required timing.

## 5.2 2-Wire-Serial Control Mode (I<sup>2</sup>C Style Interface)

The 2-wire bus is a bidirectional serial bus protocol. This protocol defines any device that sends data onto the bus as a transmitter (or master), and the receiving device as the receiver (or slave). The NAU85L20 can function only as a slave device when in the 2-wire interface configuration.

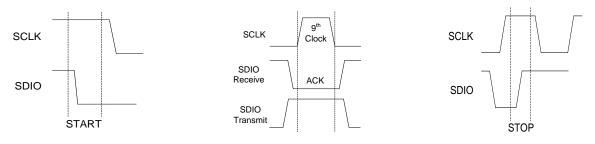

### 5.3 2-Wire Protocol Convention

All 2-Wire interface operations must begin with a START condition, which is a HIGH-to-LOW transition of SDIO while SCLK is HIGH. All 2-Wire interface operations are terminated by a STOP condition, which is a LOW to HIGH transition of SDIO while SCLK is HIGH. A STOP condition at the end of a read or write operation places the device in a standby mode.

An acknowledge (ACK), is a software convention used to indicate a successful data transfer. To allow for the ACK response, the transmitting device releases the SDIO bus after transmitting eight bits. During the ninth clock cycle, the receiver pulls the SDIO line LOW to acknowledge the reception of the eight bits of data.

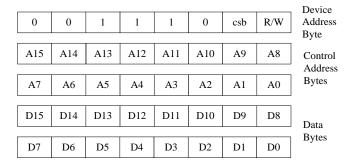

Following a START condition, the master must output a device address byte. This consists of a 7-bit device address, and the LSB of the device address byte is the R/W (Read/Write) control bit. When R/W=1, this indicates the master is initiating a read operation from the slave device, and when R/W=0, the master is initiating a write operation to the slave device. If the device address matches the address of the slave device, the slave will output an ACK during the period when the master allows for the ACK signal.

Figure 12: Valid START Condition

Figure 13: Valid Acknowledge

Figure 14: Valid STOP Condition

Figure 15: Slave Address Byte, Control Address Bytes, and Data Byte Order

## 5.4 2-Wire Write Operation

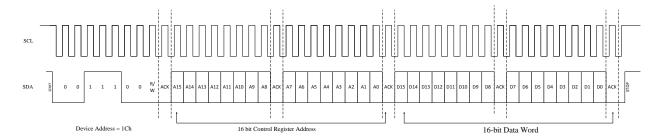

A Write operation consists of a three-byte instruction followed by one or more Data Bytes. A Write operation requires a START condition, followed by a valid device address byte with R/W=0, a valid control address byte, data byte(s), and a STOP condition.

The Device Address of the NAU85L20 is either 0x1C (CSB=0) or 0x1D (CSB=1). In I2C mode the CSB pin will set the LSB of the Slave Address. If the Device Address matches this value, the NAU85L20 will respond with the expected ACK signaling as it accepts the data being transmitted to it.

Figure 16: Byte Write Sequence

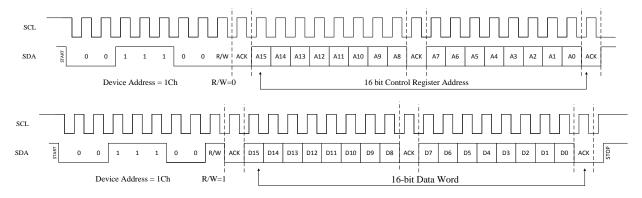

## 5.5 2-Wire Read Operation

A Read operation consists of a three-byte Write instruction followed by a Read instruction of one or more data bytes. The bus master initiates the operation issuing the following sequence: a START condition, device address byte with the R/W bit set to "0", and a Control Register Address byte. This indicates to the slave device which of its control registers is to be accessed.

If the device address matches this value, the NAU85L20 will respond with the expected ACK signaling as it accepts the Control Register Address being transmitted into it. After this, the master transmits a second START condition, and a second instantiation of the same device address, but now with R/W=1.

After again recognizing its device address, the NAU85L20 transmits an ACK, followed by a two byte value containing the 16 bits of data from the selected control register inside the NAU85L20.

During this phase, the master generates the ACK signaling with each byte transferred from the NAU85L20. If there is no STOP signal from the master, the NAU85L20 will internally auto-increment the target Control Register Address and then output the two data bytes for this next register in the sequence.

This process will continue as long as the master continues to issue ACK signaling. If the Control Register Address being indexed inside the NAU85L20 reaches the value 0xFFFF (hexadecimal) and the value for this register is output, the index will roll over to 0x0000. The data bytes will continue to be output until the master terminates the read operation by issuing a STOP condition.

Figure 17: Read Sequence

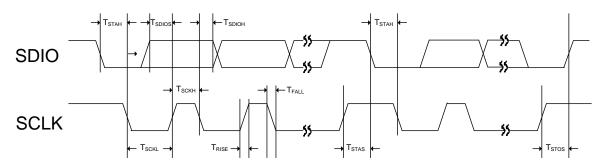

# 5.6 Digital Serial Interface Timing

Figure 18: Two-Wire Control Mode Timing

| Symbol             | Description                                                                          | min   | typ | max | unit |

|--------------------|--------------------------------------------------------------------------------------|-------|-----|-----|------|

| T <sub>STAH</sub>  | SDIO falling edge to SCLK falling edge hold timing in START / Repeat START condition | 600   | -   | -   | ns   |

| T <sub>STAS</sub>  | SCLK rising edge to SDIO falling edge setup timing in Repeat START condition         | 600   | -   | -   | ns   |

| T <sub>STOS</sub>  | SCLK rising edge to SDIO rising edge setup timing in STOP condition                  | 600   | -   | -   | ns   |

| T <sub>SCKH</sub>  | SCLK High Pulse Width                                                                | 600   | -   | -   | ns   |

| T <sub>SCKL</sub>  | SCLK Low Pulse Width                                                                 | 1,300 | -   | -   | ns   |

| T <sub>RISE</sub>  | Rise Time for all 2-wire Mode Signals                                                | -     | -   | 300 | ns   |

| T <sub>FALL</sub>  | Fall Time for all 2-wire Mode Signals                                                | -     | -   | 300 | ns   |

| T <sub>SDIOS</sub> | SDIO to SCLK Rising Edge DATA Setup Time                                             | 100   | -   | -   | ns   |

| T <sub>SDIOH</sub> | SCLK falling Edge to SDIO DATA Hold Time                                             | 0     | -   | 600 | ns   |

#### 5.7 Software Reset

The entire NAU85L20 and all of its control registers can be reset to default initial conditions by writing any value to <a href="Mailto:SW\_RESET Reg0x00">SW\_RESET Reg0x00</a>, using any of the control interface modes. Writing to any other valid register address terminates the reset condition, but all registers will now be set to their power-on default values.

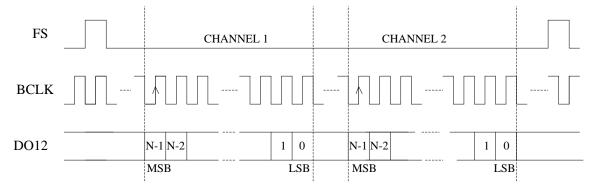

# 6 Digital Audio Interface

The NAU85L20 can be configured as either the master or the slave, by setting <a href="PCM\_CTRL1.MS">PCM\_CTRL1.MS</a>

<a href="REG0x11[3]">REG0x11[3]</a>, 1 for master mode and 0 for slave mode. By default, the NAU85L20 is in Slave mode. In master mode, NAU85L20 outputs both Frame Sync (FS) and the audio data bit clock (BCLK) which has full control of the data transfer. In the slave mode, an external controller supplies BCLK and FS. Data is latched on the rising edge of BCLK.

In master mode, the BCLK and FS are generated from MCLK according to the clock division specified in <a href="PCMCLOCK GENERATION">PCMCLOCK GENERATION</a>.

The DO12 data port only supports normal mode. The DO12 default setting is normal mode with PCM A format.

When DO12 are not driving PCM data, they can be configured to drive a low output, be tri-state, or have a weak pull-up or pull-down. If <a href="PCM\_CTRL1.DO12\_DRV REG0x11[14]">PCM\_CTRL1.DO12\_DRV REG0x11[14]</a> is set then DO12 will drive an output low when not transmitting data. When DO12\_TRI is set DO12 will be tri-state when not transmitting. Pull-up or pull-down devices can be added to the DO12 pin by setting pull enable (DO12\_PE) bit and selecting up or down with DO12\_PS where 1 = pull-up and 0 = pull-down. This enables user to configure for wired-OR type bus sharing. All of these controls can be found in register <a href="PCM\_CTRL1 REG0x11">PCM\_CTRL1 REG0x11</a>.

Nuvoton Technology Corporation America Tel: 1-408-544-1718

Rev. 0.1.9: May 10, 2016

If PE and PS are both logic=0, DO12 is high impedance, except when actively transmitting left and right channel audio data. After outputting audio channel data, DO12 will return to high impedance on the BCLK negative edge during the LSB data period if <a href="PCM\_CTRL1.TRI REG0x11[9]">PCM\_CTRL1.TRI REG0x11[9]</a>, is HIGH, or on the BCLK positive edge of LSB if <a href="PCM\_CTRL1.TRI REG0x11[9]">PCM\_CTRL1.TRI REG0x11[9]</a> is LOW. Tri-stating on the negative edge allows the transmission of data by multiple sources in adjacent timeslots with reduced risk of bus driver contention.

ADC Output through Channel1 and Channel2 can be selected by setting <u>DIGITAL MUX.CH1 SEL REG0x44[1:0]=00</u> and <u>DIGITAL\_MUX.CH2\_SEL REG0x44[3:2]=11</u> respectively.

There are six types of data formats in normal mode, which is entered with <a href="PCM\_CTRL4.TDM\_MODE">PCM\_CTRL4.TDM\_MODE</a> REG0x14[15] = 0.

| PCM Mode         | PCM_CTRL0. AIFMT REG0x10[1:0] | PCM_CTRL0.<br>LRP<br>REG0x10[6] | PCM_CTRL1. PCM TS EN REG0x11[10] | PCM_CTRL4.TDM<br>OFFSET_EN<br>REG0x14[14] |

|------------------|-------------------------------|---------------------------------|----------------------------------|-------------------------------------------|

| Right Justified  | 00                            | 0                               | 0                                | 0                                         |

| Left Justified   | 01                            | 0                               | 0                                | 0                                         |

| I2S              | 10                            | 0                               | 0                                | 0                                         |

| PCM A            | 11                            | 0                               | 0                                | 0                                         |

| РСМ В            | 11                            | 1                               | 0                                | 0                                         |

| PCM Time<br>Slot | 11                            | Don't care                      | 1                                | 0                                         |

Table 9: Digital Audio Interface Normal Modes

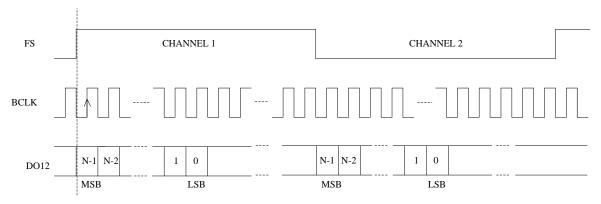

## 6.1 Right-Justified Audio Data

In right-justified mode, the LSB is clocked on the last BCLK rising edge before FS transitions. When FS is HIGH, left channel data is transmitted and when FS is LOW, right channel data is transmitted. This is shown in the figure below where N is the word length.

Figure 19: Right Justified Audio Format

### 6.2 Left-Justified Audio Data

In left-justified mode, the MSB is clocked on the first BCLK rising edge after FS transitions. When FS is HIGH, left channel data is transmitted and when FS is LOW, right channel data is transmitted. This is shown in the figure below.

Figure 20: Left Justified Audio Format

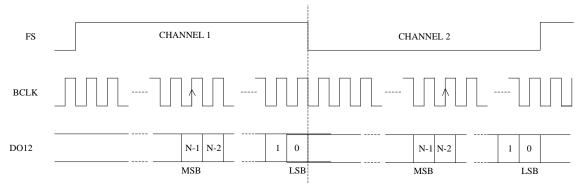

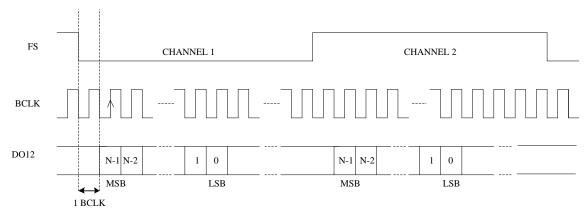

### 6.3 I2S Audio Data Mode

In I2S mode, the MSB is clocked on the second BCLK rising edge after FS transitions. When FS is LOW, left channel data is transmitted and when FS is HIGH, right channel data is transmitted. This is shown in the figure below.

Figure 21: I2S Audio Format

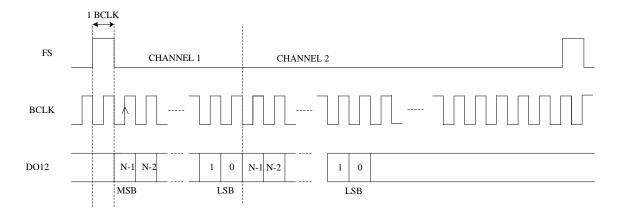

#### 6.4 PCM A Audio Data

In the PCM A mode, left channel data is transmitted first followed immediately by right channel data. The left channel MSB is clocked on the second BCLK rising edge after the FS pulse rising edge, and the right channel MSB is clocked on the next SCLK after the left channel LSB. This is shown in the figure below.

Figure 22: PCM A Audio Format

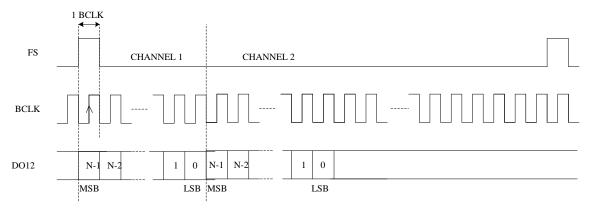

### 6.5 PCM B Audio Data

In the PCM B mode, left channel data is transmitted first followed immediately by right channel data. The left channel MSB is clocked on the first BCLK rising edge after the FS pulse rising edge, and the right channel MSB is clocked on the next SCLK after the left channel LSB. This is shown in the figure below.

Figure 23: PCM B Audio Format

### 6.6 PCM Time Slot Audio Data

The PCM time slot mode is used to delay the time at ADC data are clocked. This increases the flexibility of the NAU85L20 to be used in a wide range of system designs. One key application of this feature is to enable multiple NAU85L20 or other devices to share the audio data bus, thus enabling more than two channels of audio. This feature may also be used to swap left and right channel data, or to cause both the left and right channels to use the same data.

Normally, the ADC data are clocked immediately after the Frame Sync (FS). In the PCM time slot mode, the audio data are delayed by a delay count specified in the device control registers. The left channel MSB is clocked on the BCLK rising edge defined by the delay count set in <a href="PCM\_CTRL2.TSLOT\_L Reg0x12[9:0]">PCM\_CTRL2.TSLOT\_L Reg0x12[9:0]</a>. The right channel MSB is clocked on the BCLK rising edge defined by the delay count set in <a href="PCM\_CTRL3.TSLOT\_R Reg0x13[9:0]">PCM\_CTRL3.TSLOT\_R Reg0x13[9:0]</a>.

Figure 24: PCM Time Slot Audio Format

# 7 Register Map

| REG    | Function         |

|--------|------------------|

| 0      | SW_RESET         |

| 1      | POWER MANAGEMENT |

| 2      | CLOCK_CTRL       |

| 3      | CLOCK_SRC        |

| 4      | FLL1             |

| 5<br>6 | FLL2             |

| 6      | FLL3             |

| 7      | FLL4             |

| 9      | FLL5             |

| 9      | FLL6             |

| Α      | FLL_VCO_RSV      |

| 10     | PCM CTRL0        |

| 11     | PCM_CTRL1        |

| 12     | PCM_CTRL2        |

| 13     | PCM CTRL3        |

| 14     | PCM CTRL4        |

| 20     | ALC CONTROL 1    |

| 21     | ALC_CONTROL_2    |

| 22     | ALC CONTROL 3    |

| 23     | ALC CONTROL 4    |

| 24     | ALC_CONTROL_5    |

| 2D     | ALC GAIN CH12    |

| 2E     | ALC_GAIN_CH34    |

| 2F     | ALC STATUS       |

| 30     | NOTCH FIL1 CH1   |

| 31     | NOTCH_FIL2_CH1   |

| 36     | NOTCH_FIL1_CH2   |

| 37     | NOTCH_FIL2_CH2   |

| 38     | HPF_FILTER_CH12  |

| REG | Function         |

|-----|------------------|

| 39  | HPF_FILTER_CH34  |

| 3A  | ADC SAMPLE RATE  |

| 40  | DIGITAL_GAIN_CH1 |

| 43  | DIGITAL_GAIN_CH  |

| 44  | DIGITAL_MUX      |

| 48  | P2P_CH1          |

| 4B  | P2P CH4          |

| 4C  | PEAK_CH1         |

| 4F  | PEAK_CH4         |

| 50  | GPIO CTRL        |

| 51  | MISC_CTRL        |

| 52  | I2C CTRL         |

| 58  | I2C_DEVICE_ID    |

| 5A  | RST              |

| 60  | VMID CTRL        |

| 61  | MUTE             |

| 64  | ANALOG ADC1      |

| 65  | ANALOG_ADC2      |

| 66  | ANALOG PWR       |

| 67  | MIC_BIAS         |

| 68  | REFERENCE        |

| 69  | FEPGA1           |

| 6C  | FEPGA4           |

| 6D  | PWR              |

|     |                  |

|     |                  |

|     |                  |

|     |                  |

|     |                  |

| Common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R      |          |                                                                      |   |   |   |   |   |   |   | В | it |   |   |   |   |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|----------------------------------------------------------------------|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|