# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# 78K0S/KY1+

8-bit Single-Chip Microcontrollers

μ**PD78F9210** μPD78F9510

μPD78F9211 μPD78F9212  $\mu$ PD78F9210(A)  $\mu$ PD78F9211(A)  $\mu$ PD78F9212(A) μPD78F9210(A2) μPD78F9211(A2) μPD78F9212(A2) μPD78F9511 μPD78F9512

Document No. U16994EJ6V0UD00 (6th edition) Date Published November 2009 NS

© NEC Electronics Corporation 2004 Printed in Japan

[MEMO]

### NOTES FOR CMOS DEVICES

- (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN: Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

- (2) HANDLING OF UNUSED INPUT PINS: Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

- (3) PRECAUTION AGAINST ESD: A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

- (4) STATUS BEFORE INITIALIZATION: Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

- (5) POWER ON/OFF SEQUENCE: In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

- (6) INPUT OF SIGNAL DURING POWER OFF STATE : Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

Windows is a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

HP9000 series 700 and HP-UX are trademarks of Hewlett-Packard Company.

SPARCstation is a trademark of SPARC International, Inc.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

- The information in this document is current as of November, 2009. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree

and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property

or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient

safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anticrime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

- (Note 1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

(M8E0909)

# INTRODUCTION

<R>

| Target Readers         | the 78K0S/KY1+ in order to des<br>programs.<br>The target devices are the following s<br>• 78K0S/KY1+: $\mu$ PD78F9210, 78F9                                                                                                                                                                                                                                                                                                                                        | gineers who wish to understand the functions of<br>ign and develop its application systems an<br>subseries products.<br>211, 78F9212, 78F9210(A), 78F9211(A),<br>10(A2), 78F9211(A2), 78F9212(A2), 78F9511,                                                                                                                                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose                | This manual is intended to give user the <b>Organization</b> below.                                                                                                                                                                                                                                                                                                                                                                                                 | rs on understanding of the functions described i                                                                                                                                                                                                                                                                                                                                                                              |

| Organization           | Two manuals are available for 78K0 (common to the 78K/0S Series).                                                                                                                                                                                                                                                                                                                                                                                                   | S/KY1+: this manual and the Instruction Manua                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 78K0S/KY1+<br>User's Manual                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78K/0S Series<br>Instructions<br>User's Manual                                                                                                                                                                                                                                                                                                                                                                                |

|                        | <ul> <li>Pin functions</li> <li>Internal block functions</li> <li>Interrupts</li> <li>Other internal peripheral functions</li> <li>Electrical specifications</li> </ul>                                                                                                                                                                                                                                                                                             | <ul> <li>CPU function</li> <li>Instruction set</li> <li>Instruction description</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

| How to Use This Manual | It is assumed that the readers of the engineering, logic circuits, and micro                                                                                                                                                                                                                                                                                                                                                                                        | nis manual have general knowledge of electrica                                                                                                                                                                                                                                                                                                                                                                                |

|                        | <ul> <li>revised points. The revised point in the PDF file and specifying it</li> <li>◇ How to read register formats</li> <li>→ For a bit number enclosed in a reserved word in the RA78K0 #pragma sfr directive in the CC</li> <li>◊ To learn the detailed functions of a → See APPENDIX B REGISTER</li> <li>◊ To learn the details of the instruction → Refer to 78K/0S Series Instruation available.</li> <li>◊ To learn the electrical specification</li> </ul> | of the <b>CONTENTS</b> . The mark <r> shows major<br/>ints can be easily searched by copying an "<r><br/>in the "Find what:" field.<br/>angle brackets (&lt;&gt;), the bit name is defined as<br/>0S, and is defined as an sfr variable using th<br/>78K0S.<br/>register whose register name is known<br/>a <b>INDEX</b>.<br/>on functions of the 78K/0S Series<br/><b>ructions User's Manual (U11047E)</b> separatel</r></r> |

| Conventions | Data significance:<br>Active low representation | Higher digits on the left and lower digits on the right : xxx (overscore over pin or signal name) |

|-------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|

|             | Note:                                           | Footnote for item marked with Note in the text                                                    |

|             | Caution:                                        | Information requiring particular attention                                                        |

|             | Remark:                                         | Supplementary information                                                                         |

|             | Numerical representation                        | : Binary ×××× or ××××B                                                                            |

|             |                                                 | Decimal XXXX                                                                                      |

|             |                                                 | Hexadecimal XXXXH                                                                                 |

|             |                                                 |                                                                                                   |

**Related Documents** The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                            | Document No. |

|------------------------------------------|--------------|

| 78K0S/KY1+ User's Manual                 | This manual  |

| 78K/0S Series Instructions User's Manual | U11047E      |

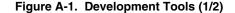

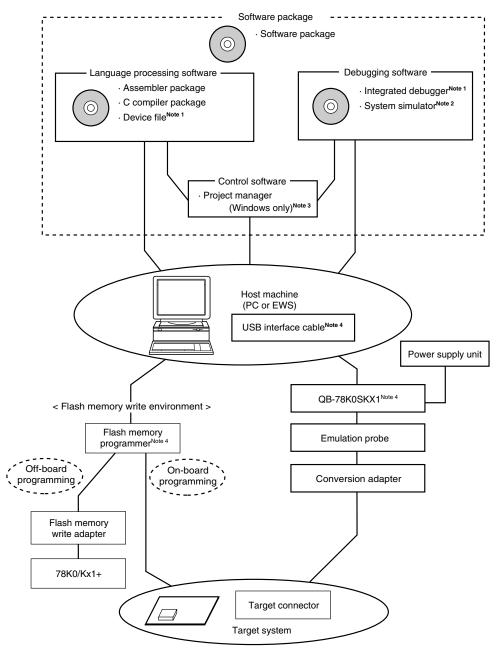

# <R> Documents Related to Development Software Tools (User's Manuals)

| Document Name                           |                              | Document No. |

|-----------------------------------------|------------------------------|--------------|

| RA78K0S Ver.2.00 Assembler Package      | Operation                    | U17391E      |

|                                         | Language                     | U17390E      |

|                                         | Structured Assembly Language | U17389E      |

| CC78K0S Ver.2.00 C Compiler             | Operation                    | U17416E      |

|                                         | Language                     | U17415E      |

| SM+ System Simulator                    | Operation                    | U18601E      |

|                                         | User Open Interface          | U18212E      |

| ID78K0S-QB Ver.3.00 Integrated Debugger | Operation                    | U18493E      |

| PM+ Ver.6.30                            |                              | U18416E      |

#### Documents Related to Development Hardware Tools (User's Manuals)

| Document Name                                             | Document No. |

|-----------------------------------------------------------|--------------|

| QB-78K0SKX1 In-Circuit Emulator                           | U18219E      |

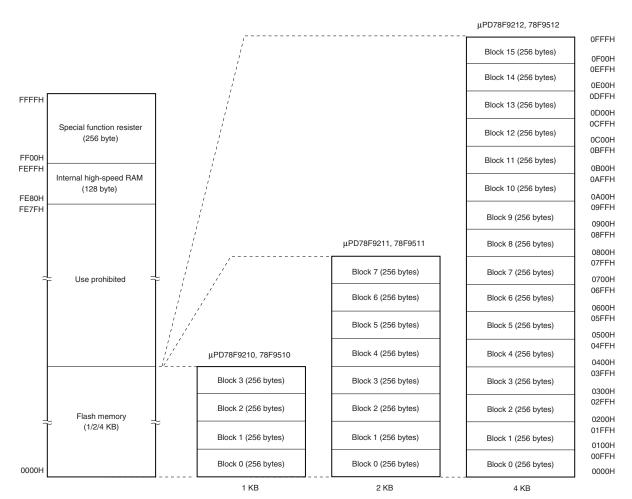

| QB-MINI2 On-Chip Debug Emulator with Programming Function | U18371E      |

# Documents Related to Flash Memory Writing (User's Manuals)

|         | Document Name                  |           | Document No. |

|---------|--------------------------------|-----------|--------------|

|         | PG-FP5 Flash Memory Programmer |           | U18865E      |

| <r></r> | QB-Programmer Programming GUI  | Operation | U18527E      |

# Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

#### **Other Related Documents**

| Document Name                                                                      | Document No. |

|------------------------------------------------------------------------------------|--------------|

| SEMICONDUCTOR SELECTION GUIDE - Products and Packages -                            | X13769X      |

| Semiconductor Device Mount Manual                                                  | Note         |

| Quality Grades on NEC Semiconductor Devices                                        | C11531E      |

| NEC Semiconductor Device Reliability/Quality Control System                        | C10983E      |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

Note See the "Semiconductor Device Mount Manual" website (http://www.necel.com/pkg/en/mount/index.html).

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

# CONTENTS

| CHAPT | rer 1   | OVERVIEW                               | 14 |

|-------|---------|----------------------------------------|----|

| 1.1   | Featu   | res                                    | 14 |

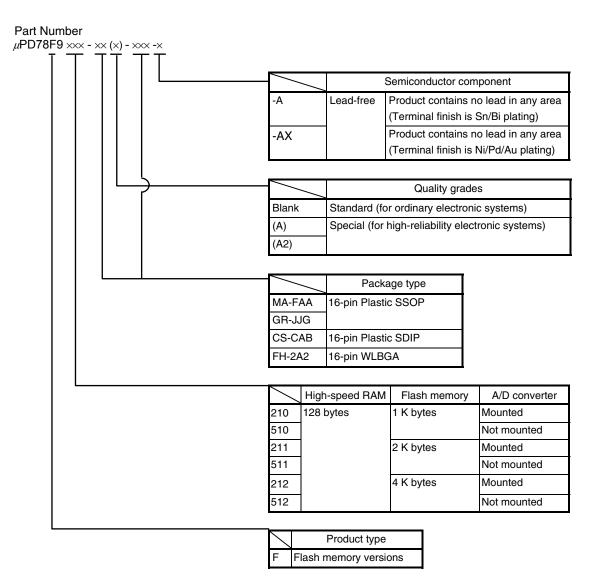

| 1.2   | Order   | ing Information                        | 16 |

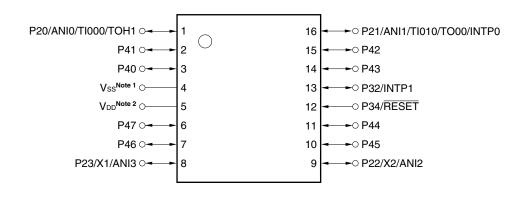

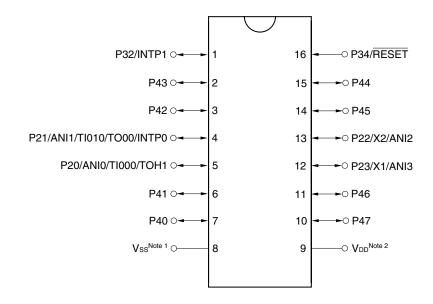

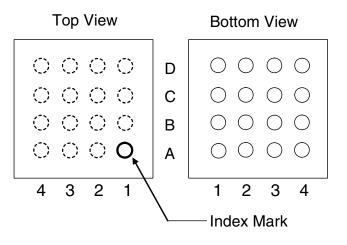

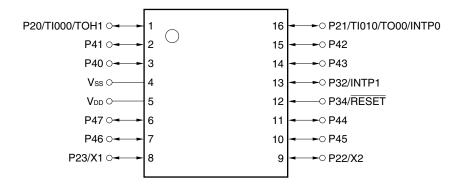

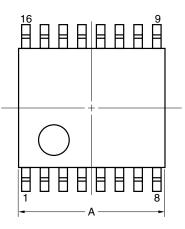

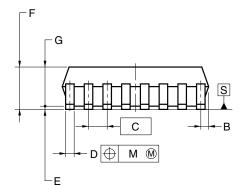

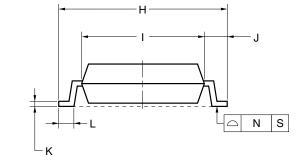

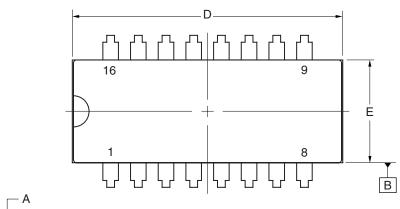

| 1.3   | Pin Co  | onfiguration (Top View)                | 17 |

|       | 1.3.1   | μPD78F921x                             | 17 |

|       | 1.3.2   | μPD78F951x                             | 19 |

| 1.4   | 78K0S   | S/Kx1+ Product Lineup                  | 20 |

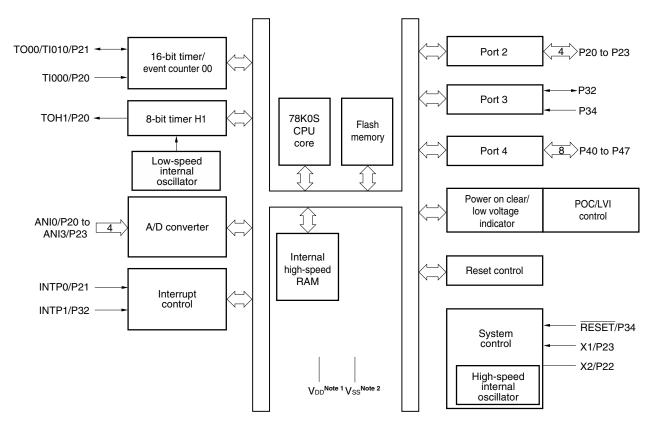

| 1.5   | Block   | Diagram                                | 21 |

|       | 1.5.1   | μPD78F921x                             | 21 |

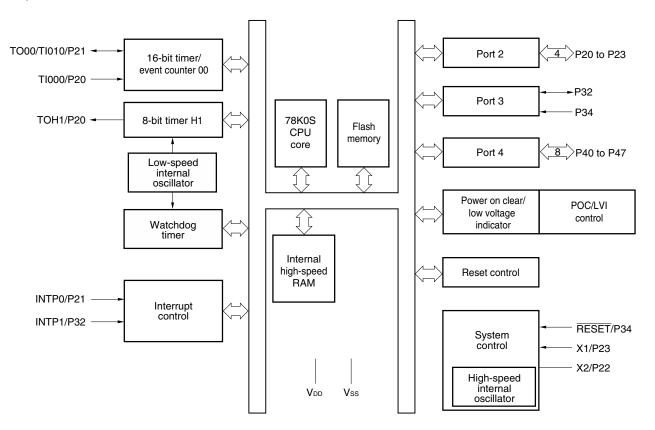

|       | 1.5.2   | μPD78F951x                             | 22 |

| 1.6   | Funct   | ional Outline                          | 23 |

| СНАРТ | TER 2   | PIN FUNCTIONS                          | 24 |

| 2.1   | Pin Fu  | Inction List                           | 24 |

|       | 2.1.1   | μPD78F921x                             | 24 |

|       | 2.1.2   | μPD78F951x                             | 26 |

| 2.2   | Pin Fu  | inctions                               | 27 |

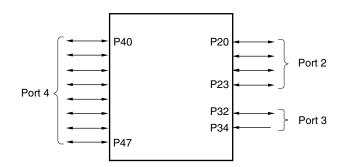

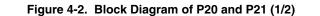

|       | 2.2.1   | P20 to P23 (Port 2)                    | 27 |

|       | 2.2.2   | P32 and P34 (Port 3)                   | 28 |

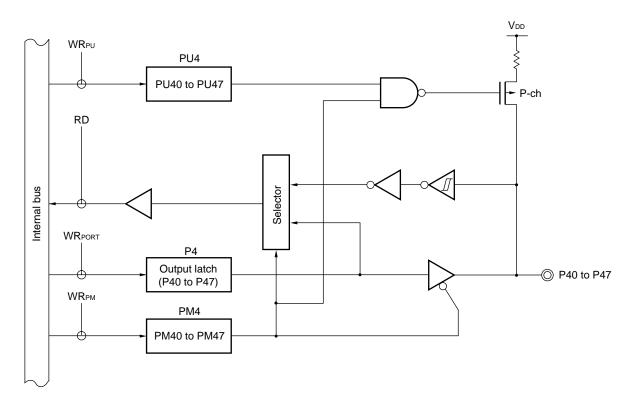

|       | 2.2.3   | P40 to P47 (Port 4)                    | 28 |

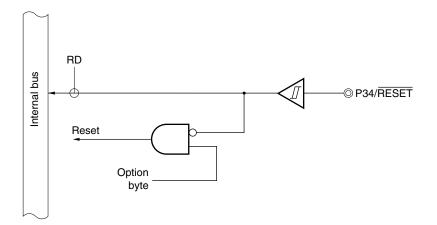

|       | 2.2.4   | RESET                                  | 28 |

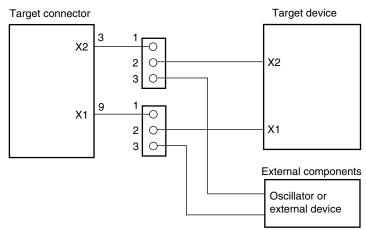

|       | 2.2.5   | X1 and X2                              | 28 |

|       | 2.2.6   | VDD                                    | 28 |

|       | 2.2.7   | Vss                                    | 28 |

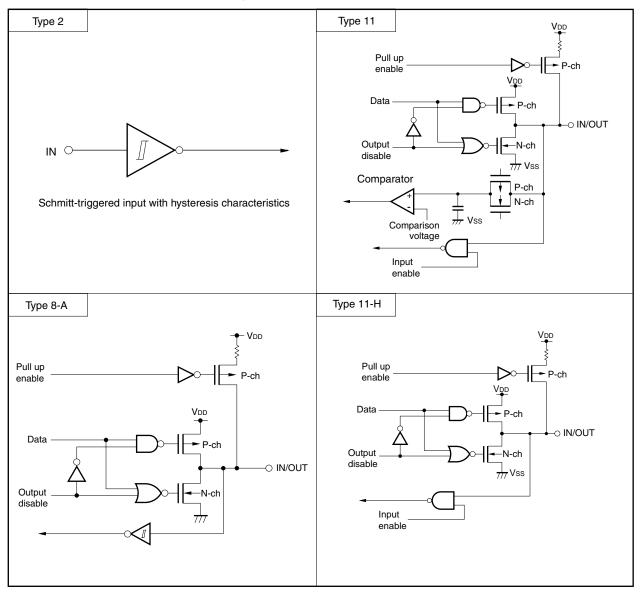

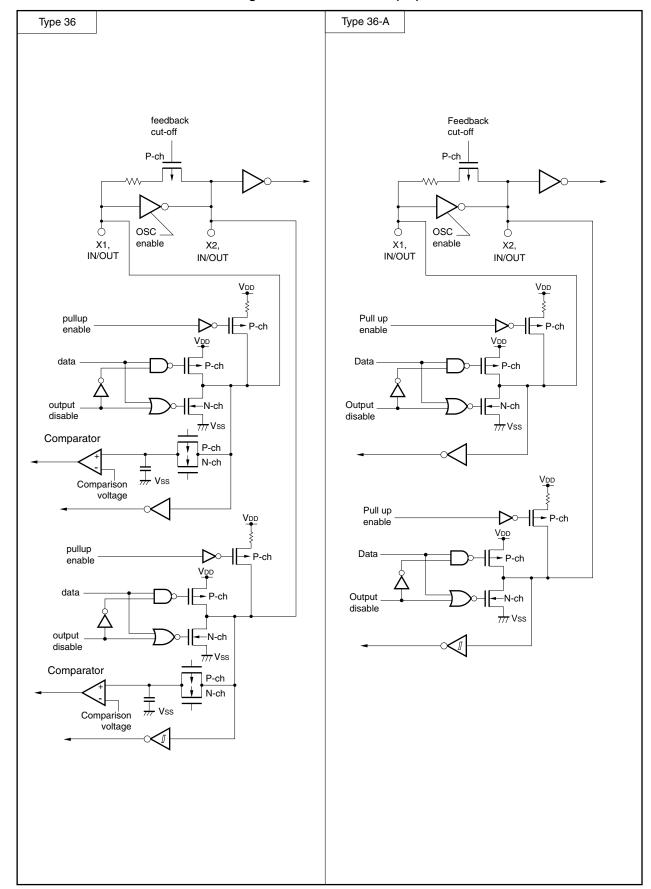

| 2.3   | Pin I/C | Circuits and Connection of Unused Pins | 29 |

| СНАРТ | TER 3   | CPU ARCHITECTURE                       | 32 |

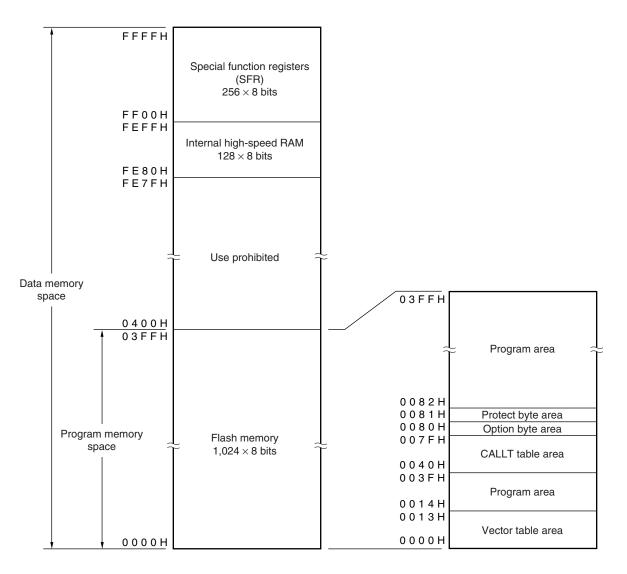

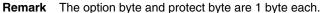

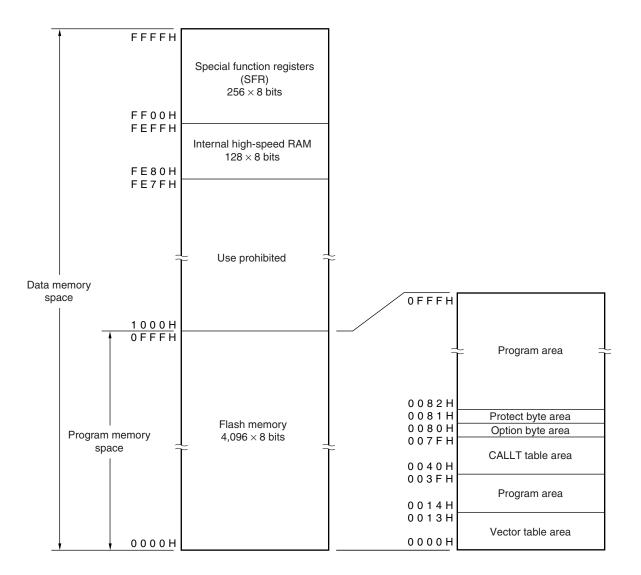

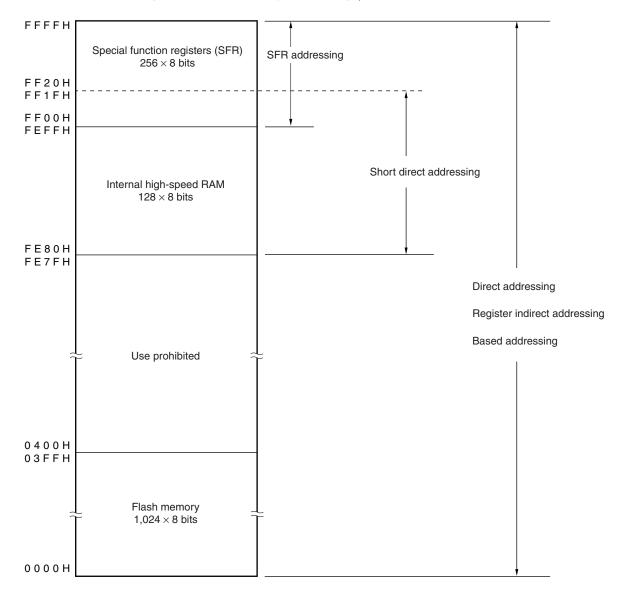

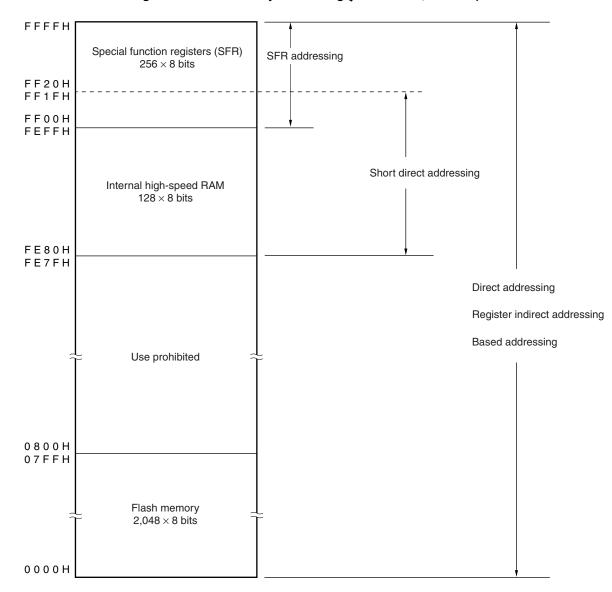

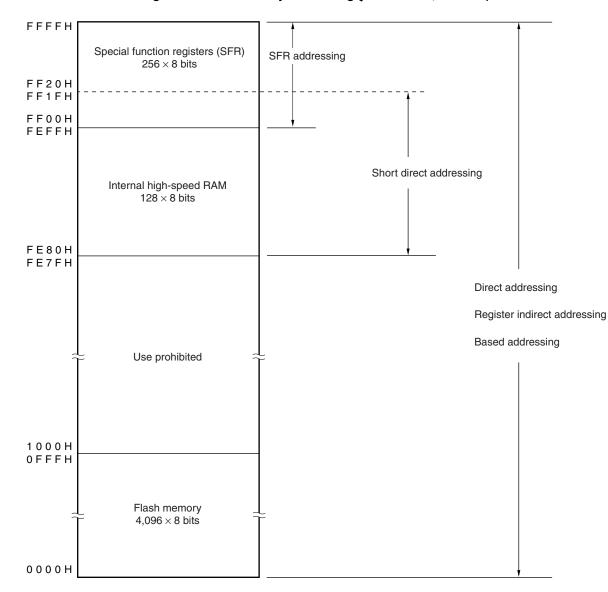

| 3.1   | Memo    | ry Space                               | 32 |

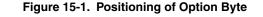

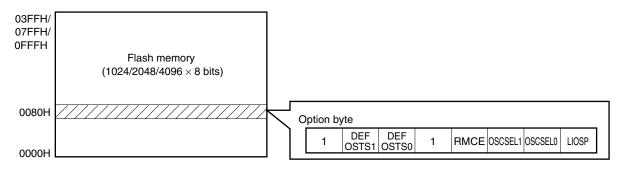

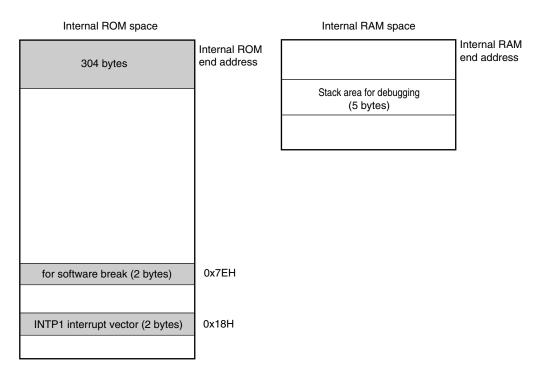

|       | 3.1.1   | Internal program memory space          | 35 |

|       | 3.1.2   | Internal data memory space             | 36 |

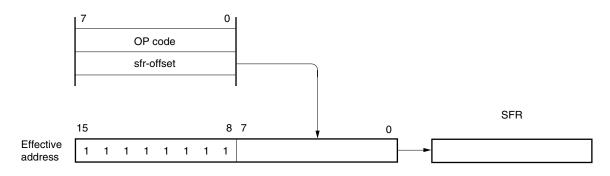

|       | 3.1.3   | Special function register (SFR) area   | 36 |

|       | 3.1.4   | Data memory addressing                 | 36 |

| 3.2   | Proce   | ssor Registers                         | 39 |

|       | 3.2.1   | Control registers                      | 39 |

|       | 3.2.2   | General-purpose registers              | 42 |

|       | 3.2.3   | Special function registers (SFRs)      | 43 |

| 3.3   | Instru  | ction Address Addressing               | 47 |

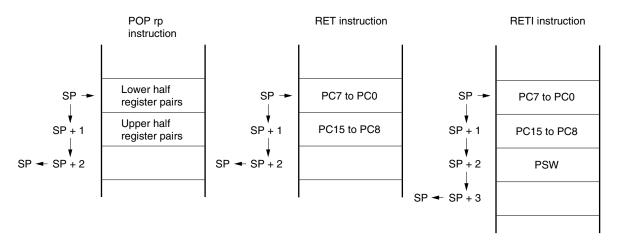

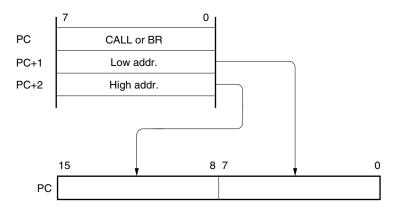

|       | 3.3.1   | Relative addressing                    | 47 |

|       | 3.3.2   | Immediate addressing                   | 48 |

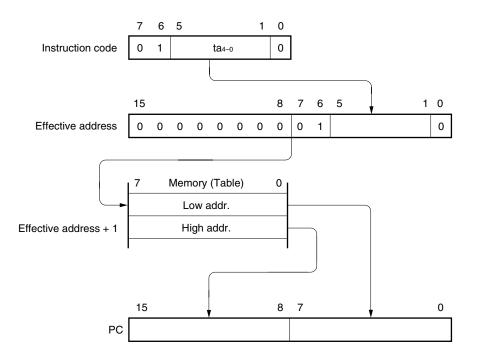

|       | 3.3.3   | Table indirect addressing              | 48 |

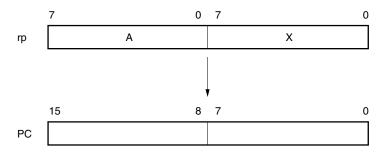

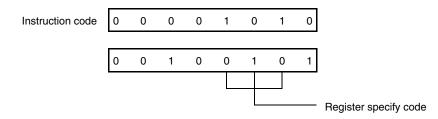

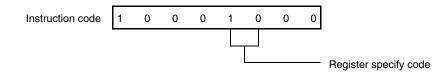

|       | 3.3.4   | Register addressing                    | 49 |

| 3.4   | Opera  | nd Address Addressing                                          | 50 |

|-------|--------|----------------------------------------------------------------|----|

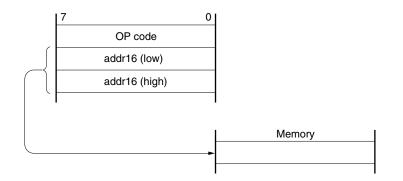

|       | 3.4.1  | Direct addressing                                              | 50 |

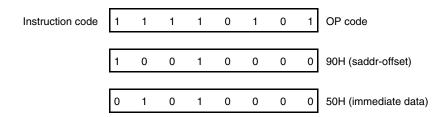

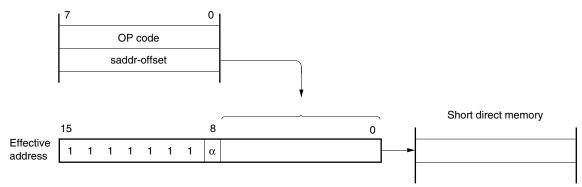

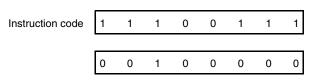

|       | 3.4.2  | Short direct addressing                                        | 51 |

|       | 3.4.3  | Special function register (SFR) addressing                     |    |

|       | 3.4.4  | Register addressing                                            |    |

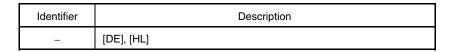

|       | 3.4.5  | Register indirect addressing                                   |    |

|       | 3.4.6  | Based addressing                                               |    |

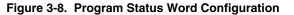

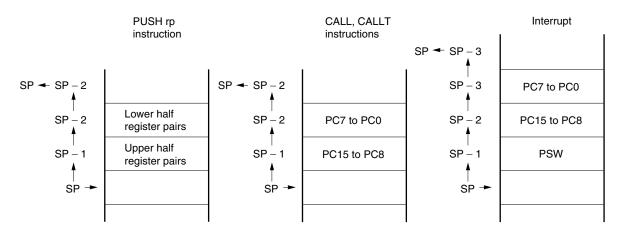

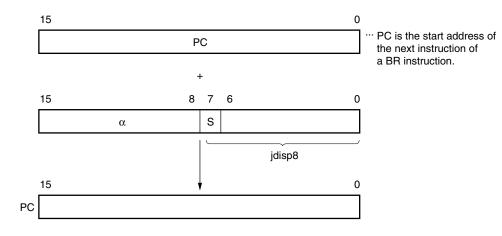

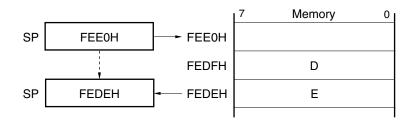

|       | 3.4.7  | Stack addressing                                               |    |

|       |        |                                                                |    |

| CHAP  | FER 4  | PORT FUNCTIONS                                                 | 57 |

|       |        | ions of Ports                                                  |    |

| 4.2   |        | configuration                                                  |    |

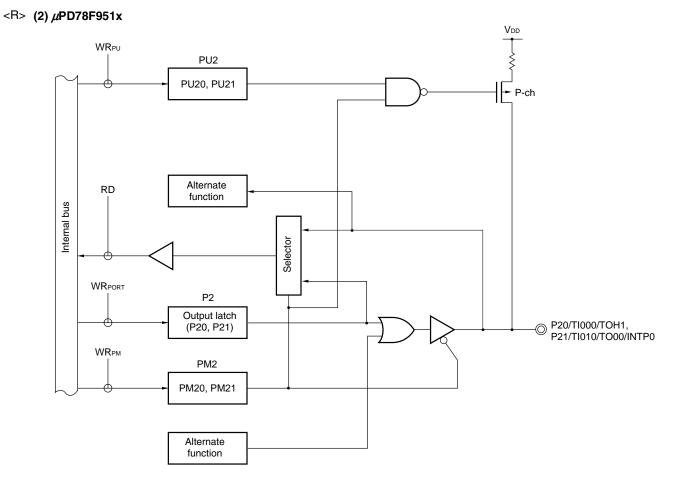

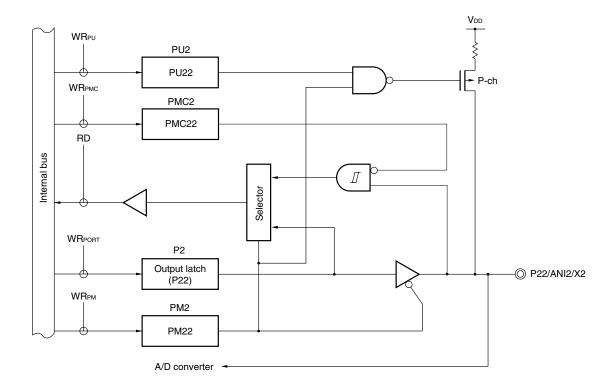

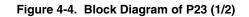

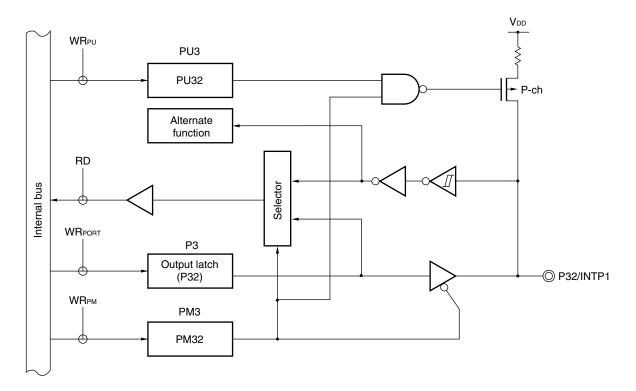

|       |        | Port 2                                                         |    |

|       |        | Port 3                                                         |    |

|       |        | Port 4                                                         |    |

|       | -      | ters Controlling Port Functions                                |    |

| 4.4   | -      | tion of Port Function                                          |    |

|       |        | Writing to I/O port                                            |    |

|       |        | Reading from I/O port                                          |    |

|       | 4.4.3  | Operations on I/O port                                         | 72 |

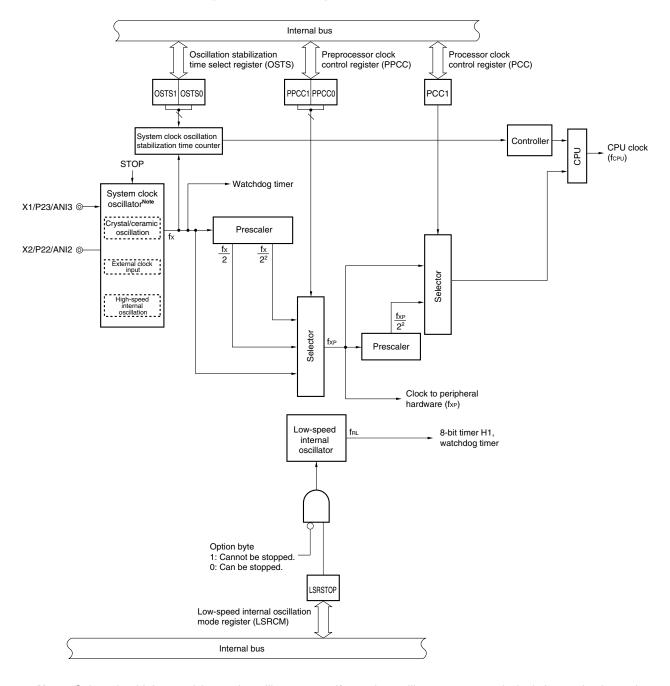

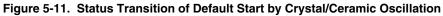

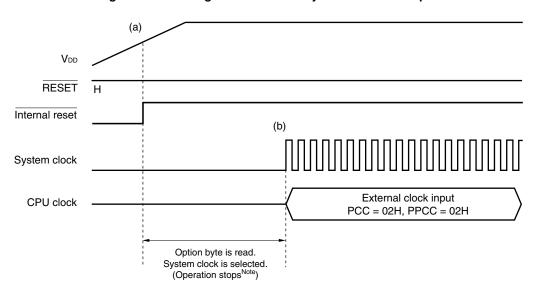

| СНАРТ | FER 5  | CLOCK GENERATORS                                               | 73 |

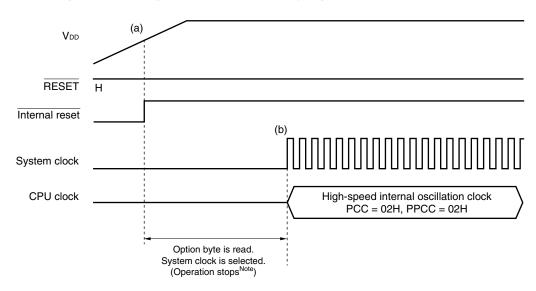

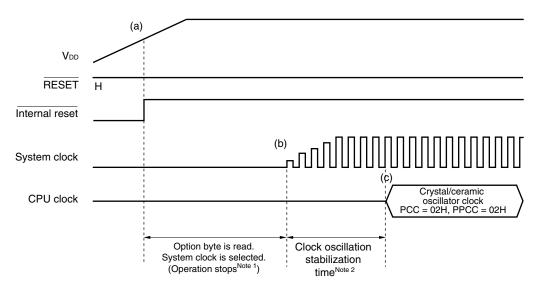

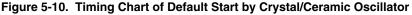

| 5.1   | Functi | ions of Clock Generators                                       | 73 |

|       | 5.1.1  | System clock oscillators                                       | 73 |

|       |        | Clock oscillator for interval time generation                  |    |

| 5.2   |        | guration of Clock Generators                                   |    |

| 5.3   | Regist | ters Controlling Clock Generators                              | 76 |

| 5.4   | Syster | n Clock Oscillators                                            | 79 |

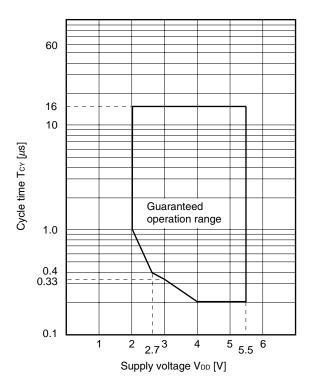

|       | 5.4.1  | High-speed internal oscillator                                 | 79 |

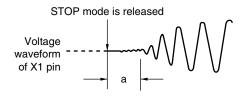

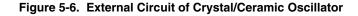

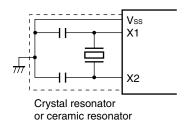

|       | 5.4.2  | Crystal/ceramic oscillator                                     | 79 |

|       | 5.4.3  | External clock input circuit                                   |    |

|       | 5.4.4  | Prescaler                                                      |    |

| 5.5   | Opera  | tion of CPU Clock Generator                                    | 82 |

| 5.6   | Opera  | tion of Clock Generator Supplying Clock to Peripheral Hardware | 88 |

|       |        | 16 DIT TIMED/EVENT COUNTED 00                                  | 00 |

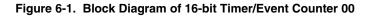

|       |        | 16-BIT TIMER/EVENT COUNTER 00                                  |    |

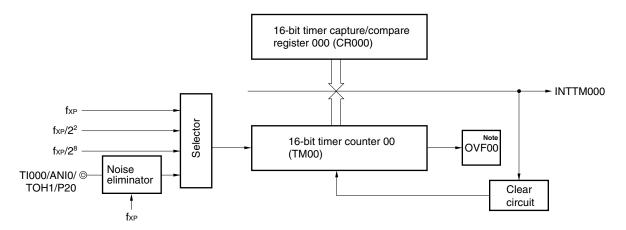

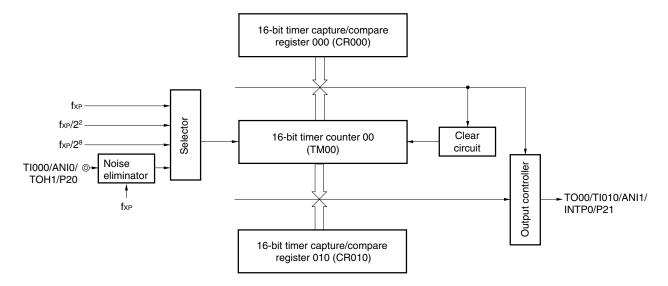

|       |        | ions of 16-bit Timer/Event Counter 00                          |    |

|       |        | guration of 16-bit Timer/Event Counter 00                      |    |

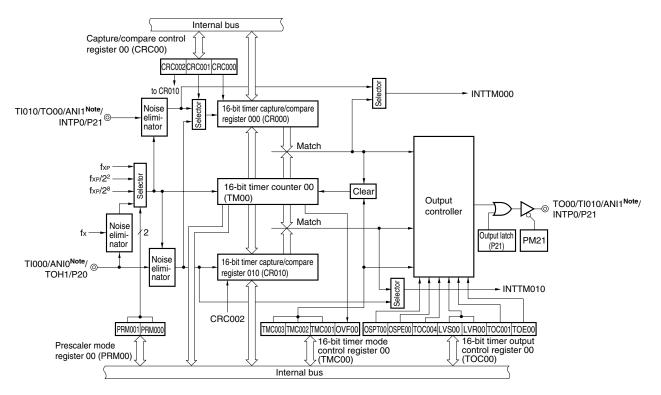

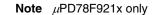

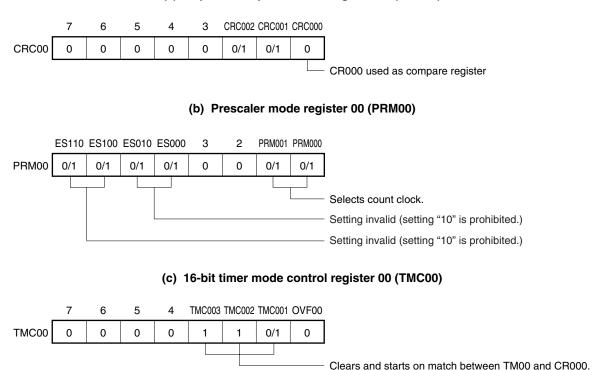

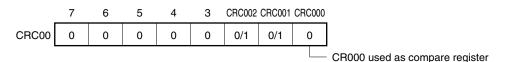

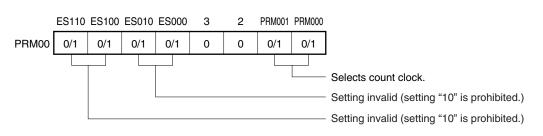

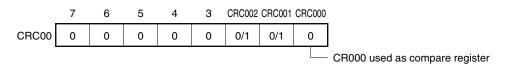

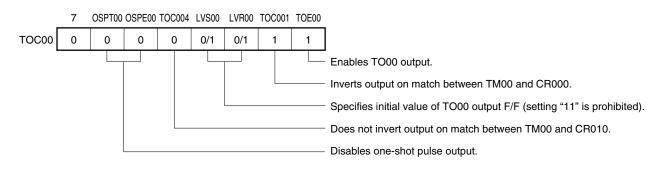

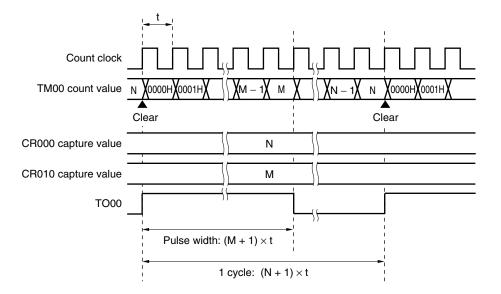

|       |        | ters to Control 16-bit Timer/Event Counter 00                  |    |

| 0.4   | -      | tion of 16-bit Timer/Event Counter 00                          |    |

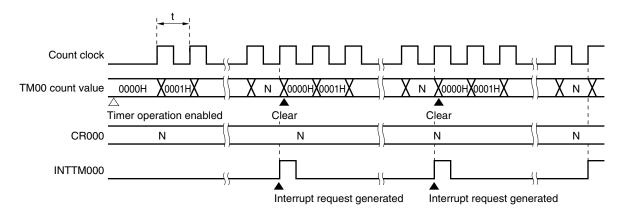

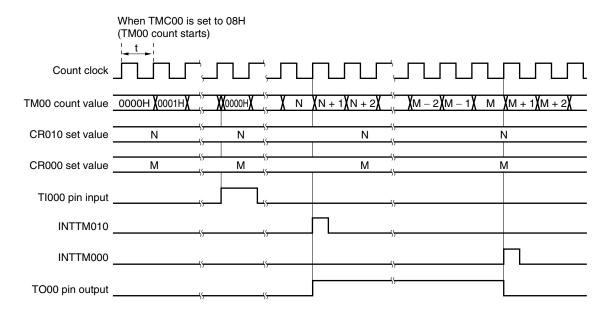

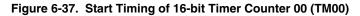

|       |        | Interval timer operation                                       |    |

|       |        | External event counter operation                               |    |

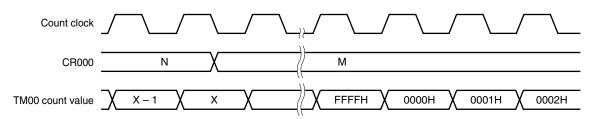

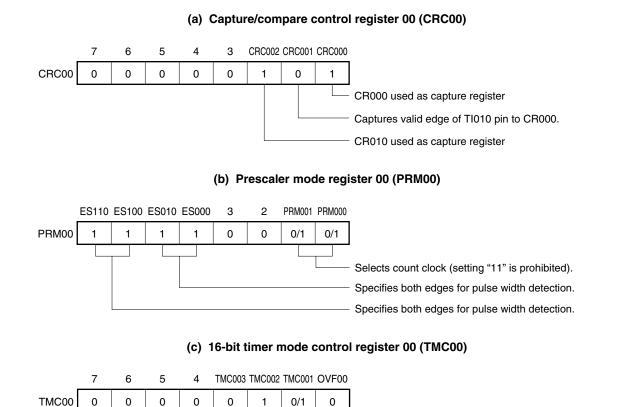

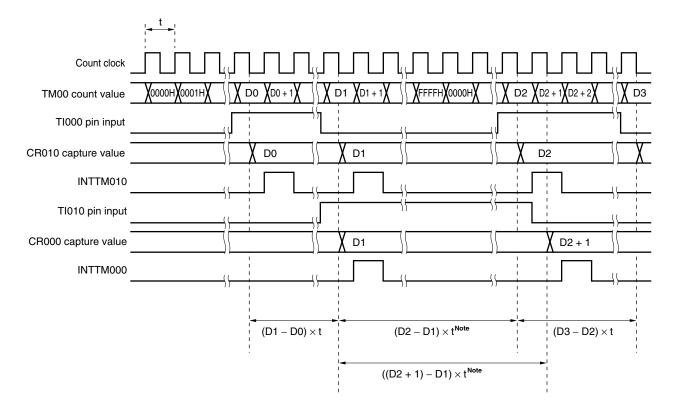

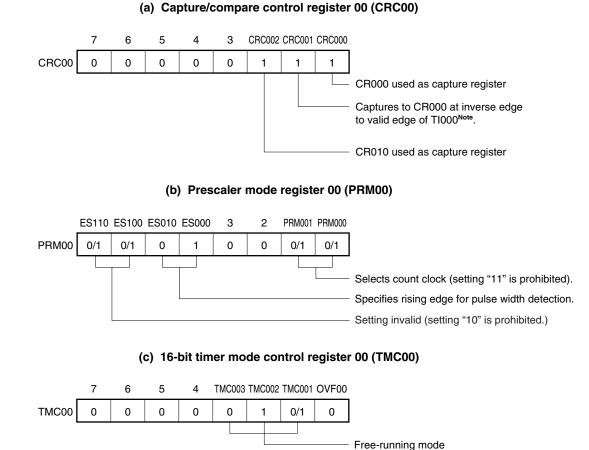

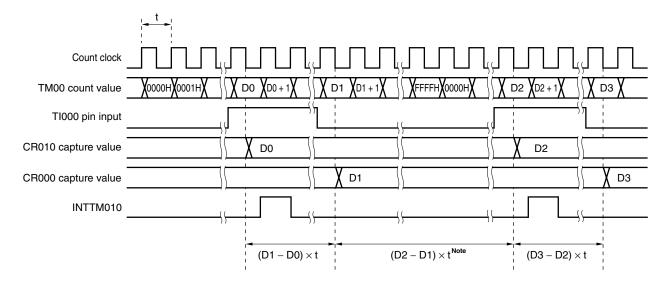

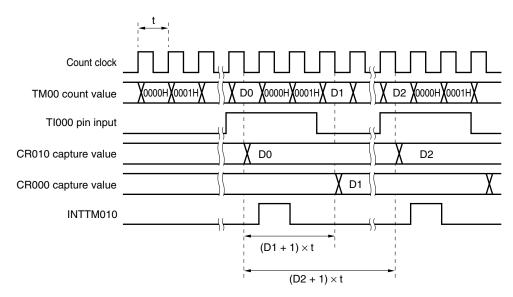

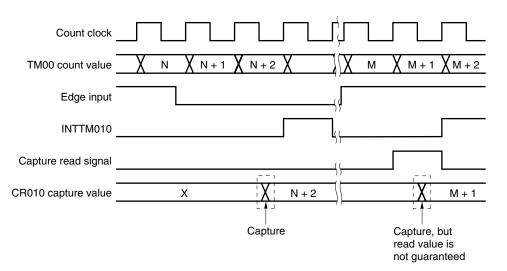

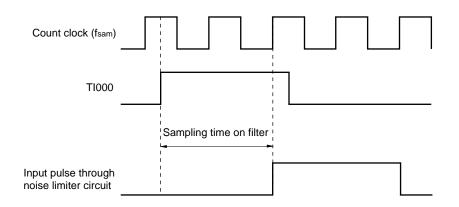

|       |        | Pulse width measurement operations                             |    |

|       |        | Square-wave output operation                                   |    |

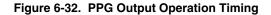

|       | 6.4.5  | PPG output operations                                          |    |

|            | One-shot pulse output operation<br>ons Related to 16-bit Timer/Event Counter 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CHAPTER 7  | 8-BIT TIMER H1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 131 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

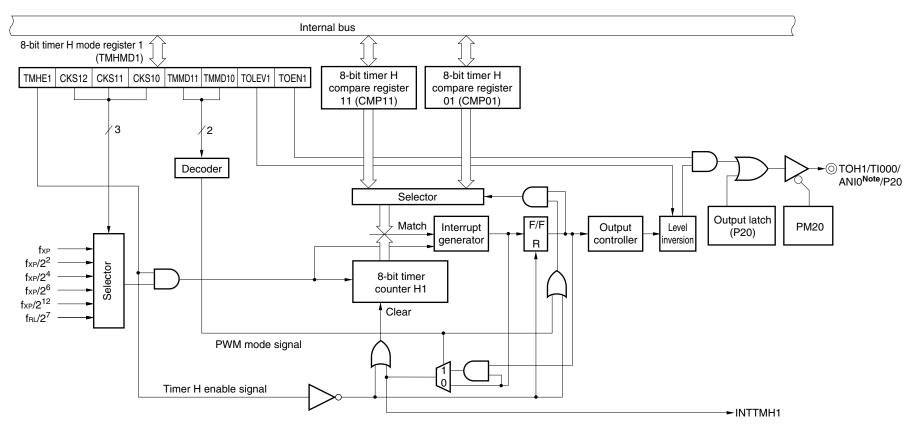

|            | tions of 8-bit Timer H1<br>guration of 8-bit Timer H1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

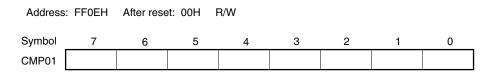

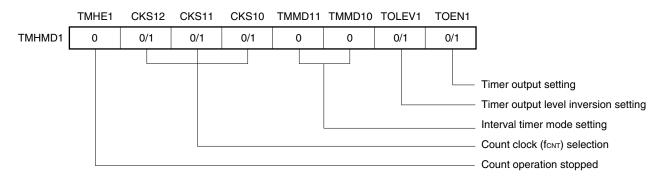

|            | sters Controlling 8-bit Timer H1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| -          | ation of 8-bit Timer H1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

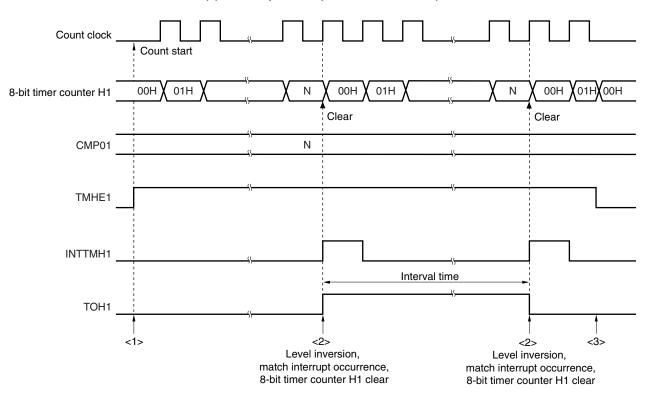

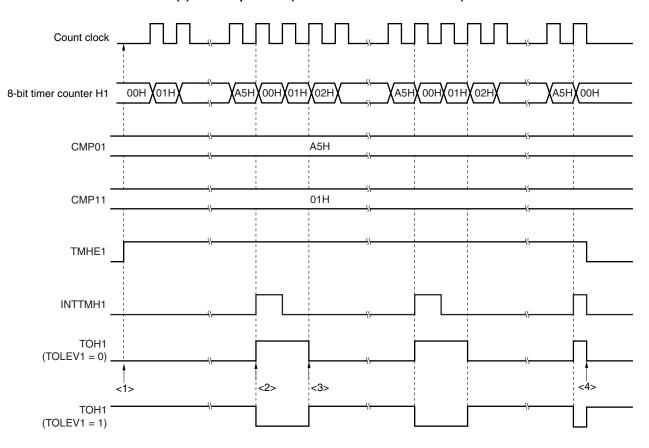

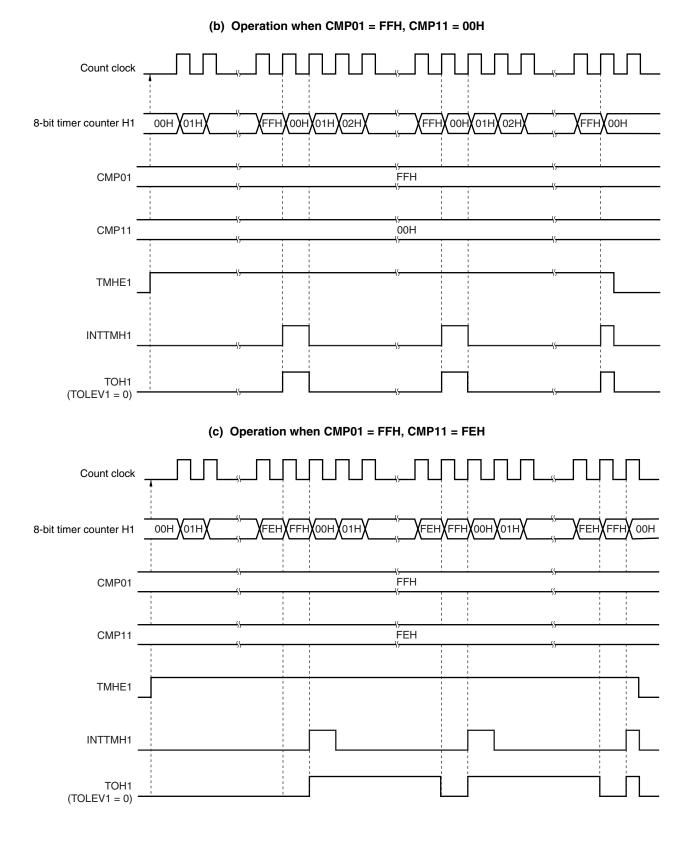

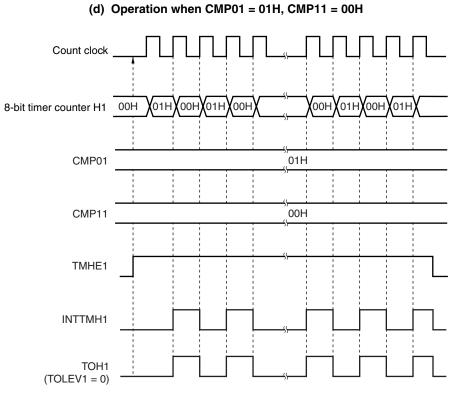

| •          | Operation as interval timer/square-wave output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

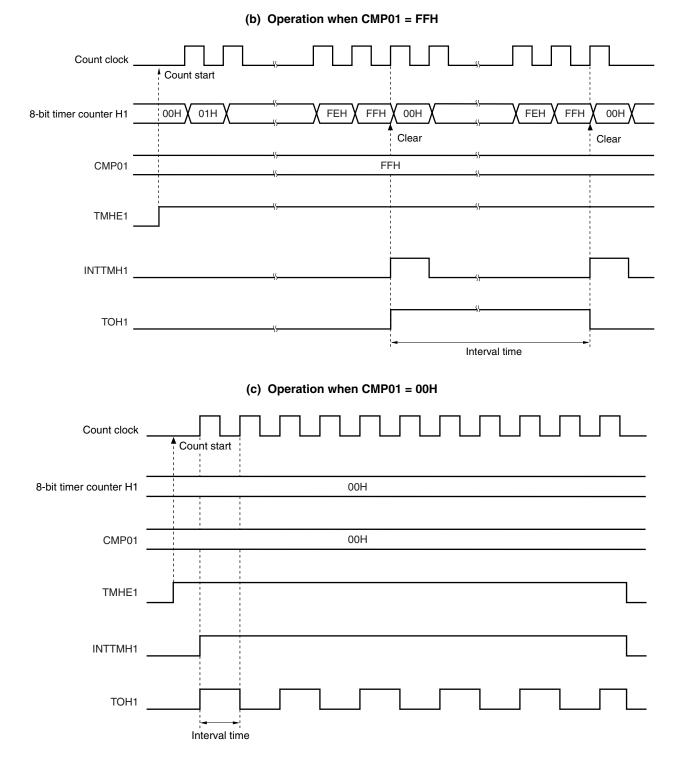

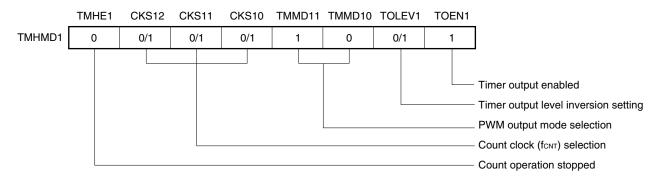

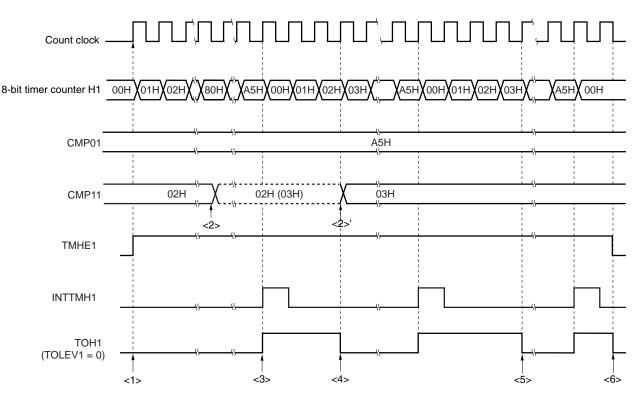

|            | 2 Operation as PWM output mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 7.4.2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

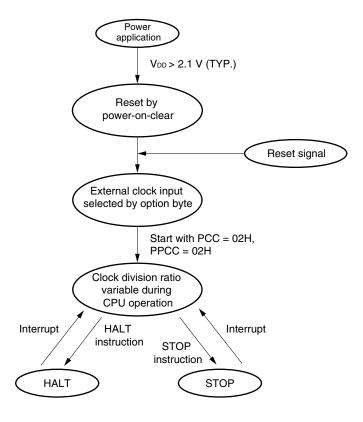

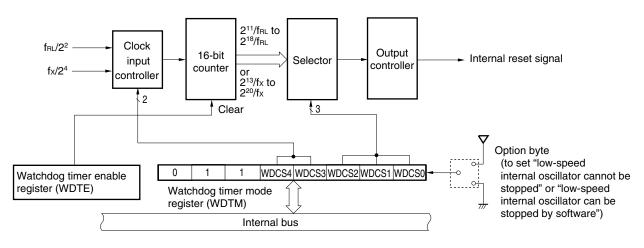

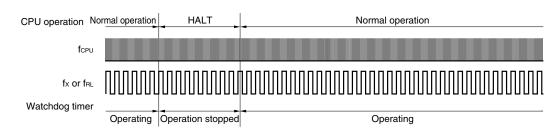

| CHAPTER 8  | WATCHDOG TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 146 |

|            | tions of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | guration of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| •          | ters Controlling Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| -          | ation of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

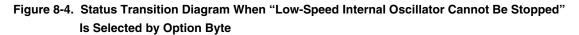

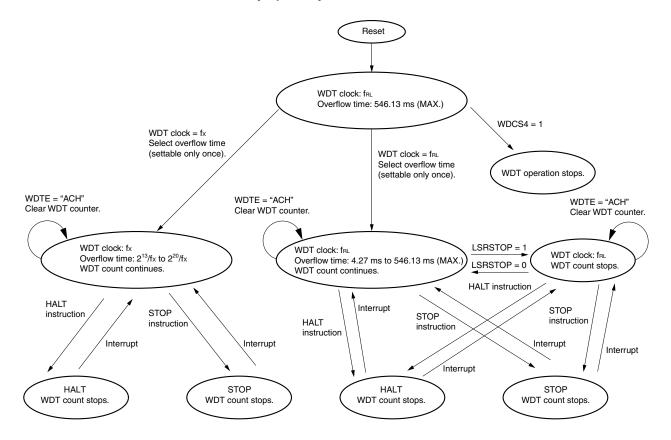

| 8.4.1      | Watchdog timer operation when "low-speed internal oscillator cannot be stopped" is sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|            | option byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

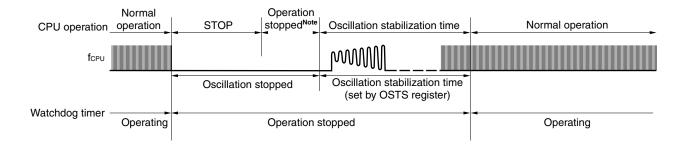

| 8.4.2      | and the second sec |     |

|            | selected by option byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

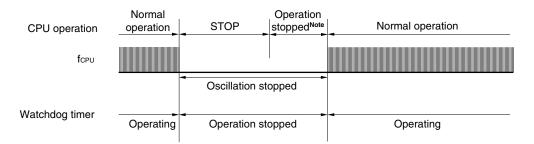

| 8.4.3      | 8 Watchdog timer operation in STOP mode (when "low-speed internal oscillator can be sto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | software" is selected by option byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

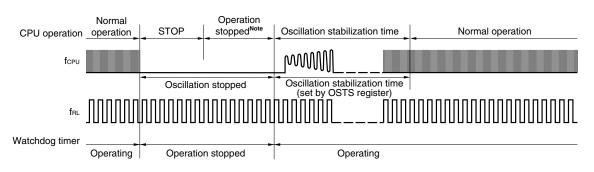

| 8.4.4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | software" is selected by option byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 156 |

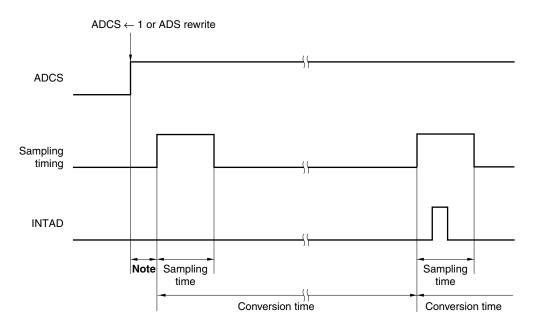

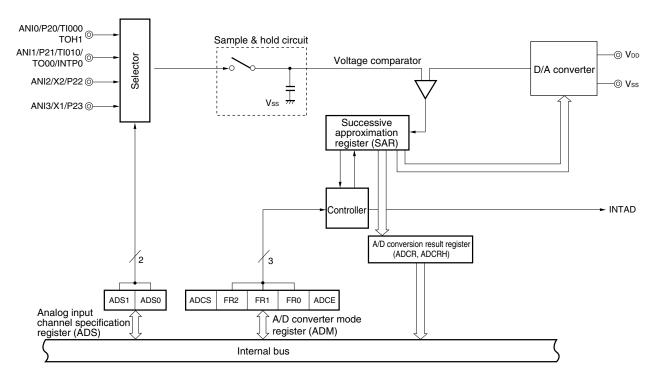

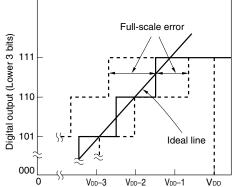

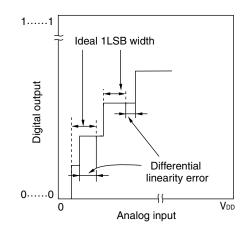

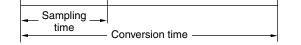

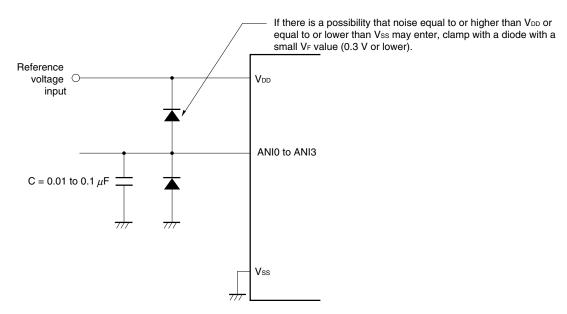

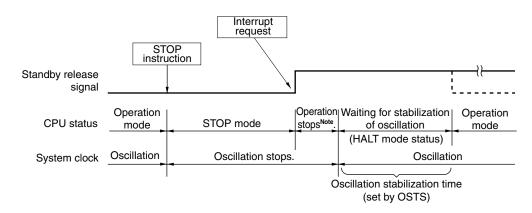

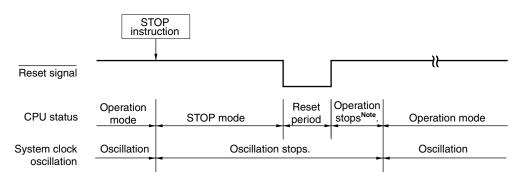

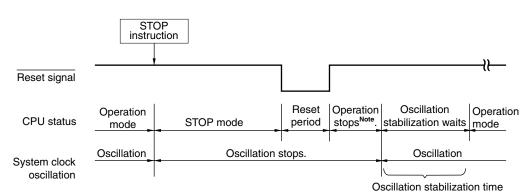

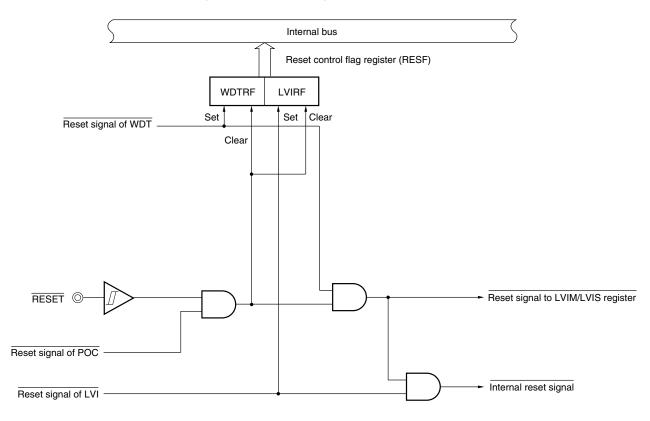

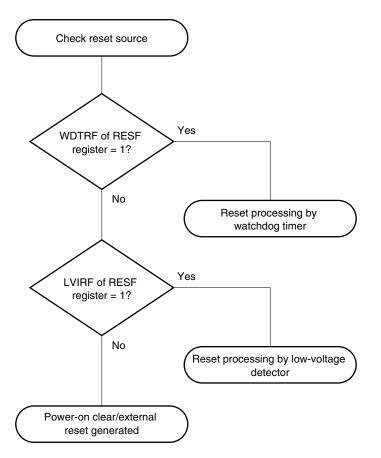

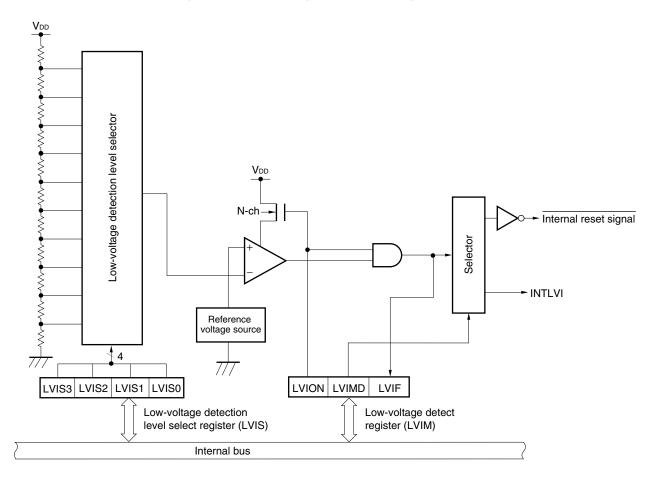

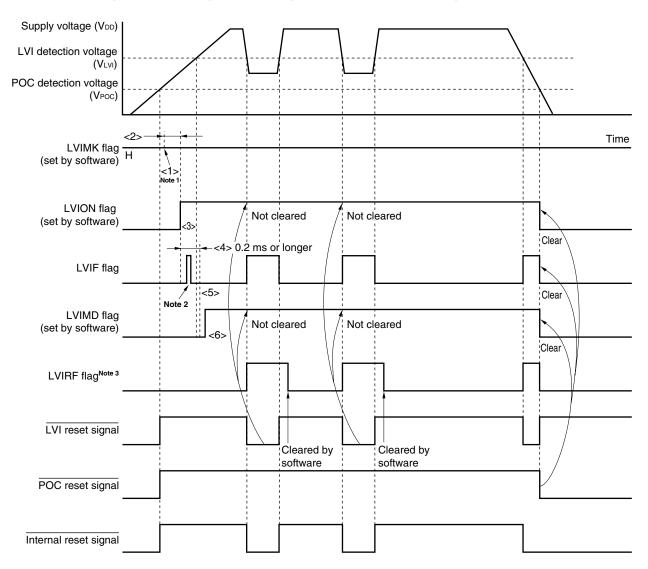

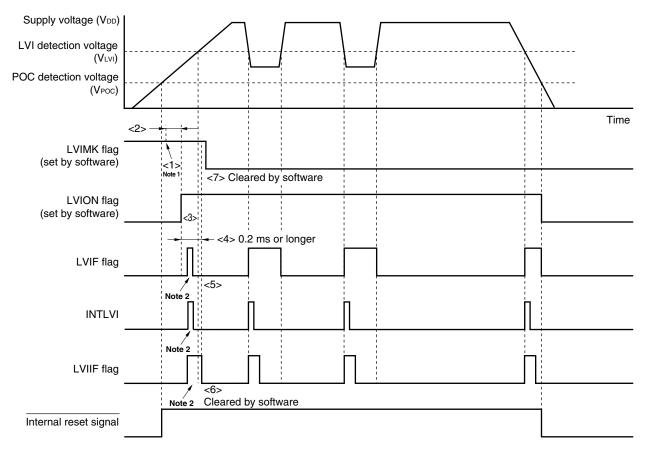

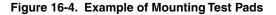

| CHAPTER 9  | A/D CONVERTER (µPD78F921x ONLY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 157 |