# HCPL-316J

# 2.5 Amp Gate Drive Optocoupler with Integrated (V<sub>CE</sub>) Desaturation Detection and Fault Status Feedback

# **Data Sheet**

# **Description**

Avago's 2.5 Amp Gate Drive Optocoupler with Integrated Desaturation ( $V_{CE}$ ) Detection and Fault Status Feedback makes IGBT  $V_{CE}$  fault protection compact, affordable, and easy-to-implement while satisfying worldwide safety and regulatory requirements.

#### **Features**

- 2.5 A maximum peak output current

- Drive IGBTs up to  $I_C = 150 \text{ A}$ ,  $V_{CE} = 1200 \text{ V}$

- Optically isolated, FAULT status feedback

- SO-16 package

- CMOS/TTL compatible

- 500 ns max. switching speeds

# Features (continued)

- "Soft" IGBT turn-off

- Integrated fail-safe IGBT protection

- Desat (V<sub>CE</sub>) detection

- Under Voltage Lock-Out protection (UVLO) with hysteresis

- User configurable: inverting, noninverting, auto-reset, auto-shutdown

- Wide operating V<sub>CC</sub> range: 15 to 30 Volts

- -40°C to +100°C operating temperature range

- 15 kV/μs min. Common Mode Rejection (CMR) at V<sub>CM</sub>=1500 V

- Regulatory approvals: UL, CSA, IEC/EN/DIN EN 60747-5-2 (1230 V<sub>peak</sub> Working Voltage)

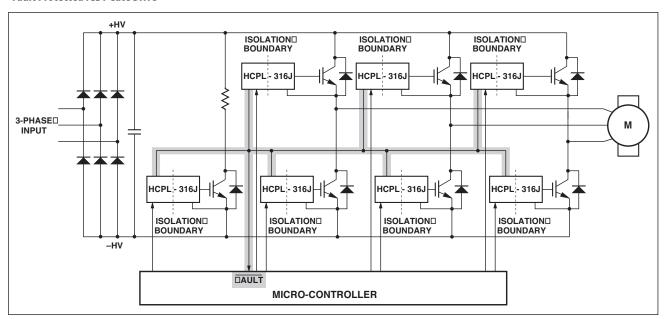

#### **Fault Protected IGBT Gate Drive**

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

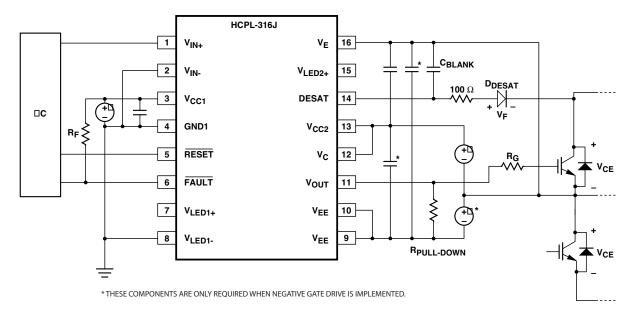

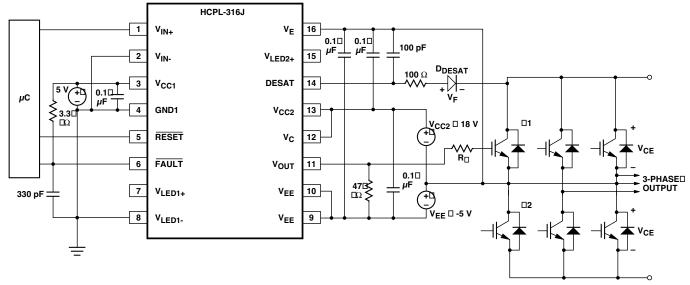

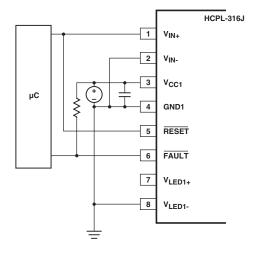

#### **Typical Fault Protected IGBT Gate Drive Circuit**

The HCPL-316J is an easy-to-use, intelligent gate driver which makes IGBT  $V_{CE}$  fault protection compact, affordable, and easy-to-implement. Features such as user configurable inputs, integrated  $V_{CE}$  detection, under volt-

age lockout (UVLO), "soft" IGBT turn-off and isolated fault feedback provide maximum design flexibility and circuit protection.

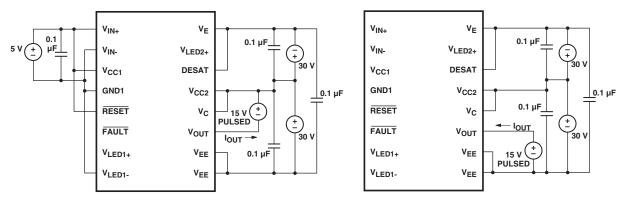

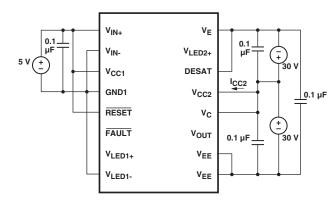

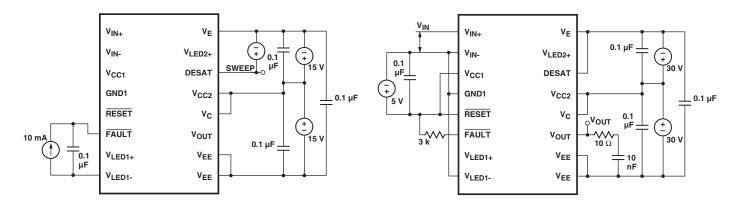

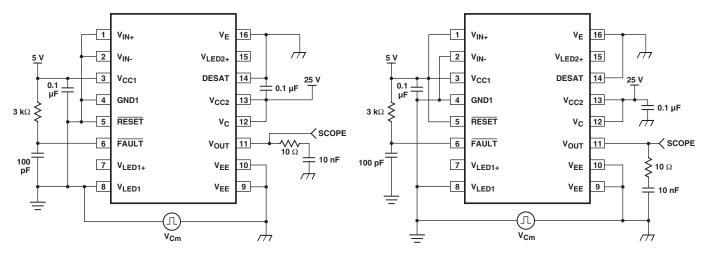

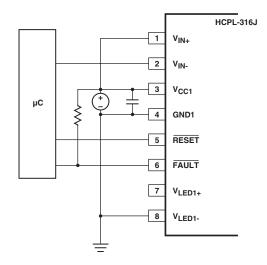

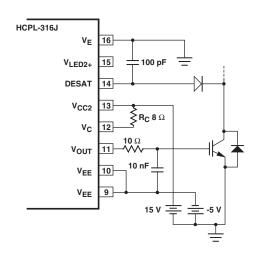

Figure 1. Typical desaturation protected gate drive circuit, noninverting.

#### **Description of Operation during Fault Condition**

- DESAT terminal monitors the IGBT V<sub>CE</sub> voltage through D<sub>DESAT</sub>.

- When the voltage on the DESAT terminal exceeds 7 volts, the IGBT gate voltage (V<sub>OUT</sub>) is slowly lowered.

- 3. FAULT output goes low, notifying the microcontroller of the fault condition.

- 4. Microcontroller takes appropriate action.

#### **Output Control**

The outputs (V<sub>OUT</sub> and FAULT) of the HCPL-316J are controlled by the combination of V<sub>IN</sub>, UVLO and a detected IGBT Desat condition. As indicated in the below table, the HCPL-316J can be configured as inverting or non-inverting using the V<sub>IN+</sub> or V<sub>IN-</sub> inputs respectively. When an inverting configuration is desired, V<sub>IN+</sub> must be held high and V<sub>IN</sub>- toggled. When a non-inverting configuration is desired, V<sub>IN-</sub> must be held low and V<sub>IN+</sub> toggled. Once UVLO is not active ( $V_{CC2} - V_E > V_{UVLO}$ ),  $V_{OUT}$  is allowed to go high, and the DESAT (pin 14) detection feature of the HCPL-316J will be the primary source of IGBT protection. UVLO is needed to ensure DESAT is functional. Once V<sub>U-</sub> VLO+ > 11.6 V, DESAT will remain functional until V<sub>UVLO-</sub> < 12.4 V. Thus, the DESAT detection and UVLO features of the HCPL-316J work in conjunction to ensure constant IGBT protection.

|           |           | UVLO              | Desat Condition<br>Detected on | Pin 6<br>(FAULT) |                  |

|-----------|-----------|-------------------|--------------------------------|------------------|------------------|

| $V_{IN+}$ | $V_{IN-}$ | $(V_{CC2} - V_E)$ | Pin 14                         | Output           | V <sub>OUT</sub> |

| Χ         | Χ         | Active            | Χ                              | Χ                | Low              |

| X         | Χ         | Χ                 | Yes                            | Low              | Low              |

| Low       | Χ         | Χ                 | Х                              | Х                | Low              |

| X         | High      | Х                 | Χ                              | Х                | Low              |

| High      | Low       | Not Active        | No                             | High             | High             |

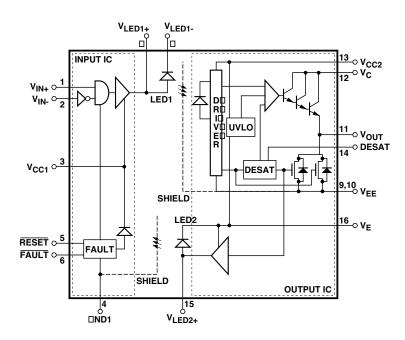

### **Product Overview Description**

The HCPL-316J is a highly integrated power control device that incorporates all the necessary components for a complete, isolated IGBT gate drive circuit with fault protection and feedback into one SO-16 package. TTL input logic levels allow direct interface with a microcontroller, and an optically isolated power output stage drives IGBTs with power ratings of up to 150 A and 1200 V. A high speed internal optical link minimizes the propagation delays between the microcontroller and the IGBT while allowing the two systems to operate at very large common mode voltage differences that are common in industrial motor drives and other power switching applications. An output IC provides local protection for the IGBT to prevent damage during overcurrents, and a second optical link provides a fully isolated fault status feedback signal for the microcontroller. A built in "watchdog" circuit monitors the power stage supply voltage to prevent IGBT caused by insufficient gate drive voltages. This integrated IGBT gate driver is designed to increase the performance and reliability of a motor drive without the cost, size, and complexity of a discrete design.

Two light emitting diodes and two integrated circuits housed in the same SO-16 package provide the input control circuitry, the output power stage, and two optical channels. The input Buffer IC is designed on a bipolar process, while the output Detector IC is designed manufactured on a high voltage BiCMOS/Power DMOS

process. The forward optical signal path, as indicated by LED1, transmits the gate control signal. The return optical signal path, as indicated by LED2, transmits the fault status feedback signal. Both optical channels are completely controlled by the input and output ICs respective-ly, making the internal isolation boundary transparent to the microcontroller.

Under normal operation, the input gate control signal directly controls the IGBT gate through the isolated output detector IC. LED2 remains off and a fault latch in the input buffer IC is disabled. When an IGBT fault is detected, the output detector IC immediately begins a "soft" shutdown sequence, reducing the IGBT current to zero in a controlled manner to avoid potential IGBT damage from inductive overvoltages. Simultaneously, this fault status is transmitted back to the input buffer IC via LED2, where the fault latch disables the gate control input and the active low fault output alerts the microcontroller.

During power-up, the Under Voltage Lockout (UVLO) feature prevents the application of insufficient gate voltage to the IGBT, by forcing the HCPL-316J's output low. Once the output is in the high state, the DESAT (V<sub>CE</sub>) detection feature of the HCPL-316J provides IGBT protection. Thus, UVLO and DESAT work in conjunction to provide constant IGBT protection.

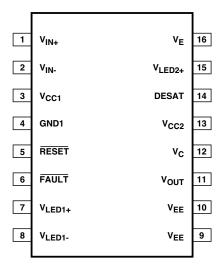

# Package Pin Out

# **Pin Descriptions**

| Symbol              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbol             | Description                                                                                                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN+</sub>    | Noninverting gate drive voltage output (V <sub>OUT</sub> ) control input.                                                                                                                                                                                                                                                                                                                                                                              | V <sub>E</sub>     | Common (IGBT emitter) output supply voltage.                                                                                                                                                                               |

| V <sub>IN-</sub>    | Inverting gate drive voltage output (V <sub>OUT</sub> ) control input.                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>LED2+</sub> | LED 2 anode. This pin must be left unconnected for guaranteed data sheet performance. (For optical coupling testing only.)                                                                                                 |

| V <sub>CC1</sub>    | Positive input supply voltage. (4.5 V to 5.5 V)                                                                                                                                                                                                                                                                                                                                                                                                        | DESAT              | Desaturation voltage input. When the voltage on DESAT exceeds an internal reference voltage of 7V while the IGBT is on, FAULT output is changed from a high impedance state to a logic low state within 5 µs. See Note 25. |

| GND1                | Input Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>CC2</sub>   | Positive output supply voltage.                                                                                                                                                                                            |

| RESET               | FAULT reset input. A logic low input for at least 0.1 µs, asynchronously resets FAULT output high and enables V <sub>IN</sub> . Synchronous control of RESET relative to V <sub>IN</sub> is required. RESET is not affected by UVLO. Asserting RESET while V <sub>OUT</sub> is high does not affect V <sub>OUT</sub> .                                                                                                                                 | Vc                 | Collector of output pull-up triple-darlington transistor. It is connected to V <sub>CC2</sub> directly or through a resistor to limit output turn-on current.                                                              |

| FAULT               | Fault output. FAULT changes from a high impedance state to a logic low output within 5 µs of the voltage on the DESAT pin exceeding an internal reference voltage of 7 V. FAULT output remains low until RESET is brought low. FAULT output is an open collector which allows the FAULT outputs from all HCPL-316Js in a circuit to be connected together in a "wired OR" forming a single fault bus for interfacing directly to the micro-controller. | Vouт               | Gate drive voltage output.                                                                                                                                                                                                 |

| V <sub>LED1+</sub>  | LED 1 anode. This pin must be left unconnected for guaranteed data sheet performance. (For optical coupling testing only.)                                                                                                                                                                                                                                                                                                                             | V <sub>EE</sub>    | Output supply voltage.                                                                                                                                                                                                     |

| V <sub>LED1</sub> - | LED 1 cathode. This pin must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                                                                                                                                                                                                            |

# **Ordering Information**

HCPL-316J is UL Recognized with 5000 Vrms for 1 minute per UL1577.

|             | Op:               | tion                  |         |                  |                |                            |              |

|-------------|-------------------|-----------------------|---------|------------------|----------------|----------------------------|--------------|

| Part number | RoHS<br>Compliant | Non RoHS<br>Compliant | Package | Surface<br>Mount | Tape<br>& Reel | IEC/EN/DIN EN<br>60747-5-2 | Quantity     |

| LICDL 2161  | -000E             | No option             | 50.16   | Χ                |                | Х                          | 45 per tube  |

| HCPL-316J   | -500E             | #500                  | SO-16   | X                | Х              | Х                          | 850 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

#### Example 1:

HCPL-316J-500E to order product of SO-16 Surface Mount package in Tape and Reel packaging with IEC/EN/DIN EN 60747-5-2 Safety Approval in RoHS compliant.

#### Example 2:

HCPL-316J to order product of SO-16 Surface Mount package in tube packaging with IEC/EN/DIN EN 60747-5-2 Safety Approval and non RoHS compliant.

Option datasheets are available. Contact your Avago sales representative or authorized distributor for information.

Remarks: The notation '#XXX' is used for existing products, while (new) products launched since 15th July 2001 and RoHS compliant option will use '-XXXE'.

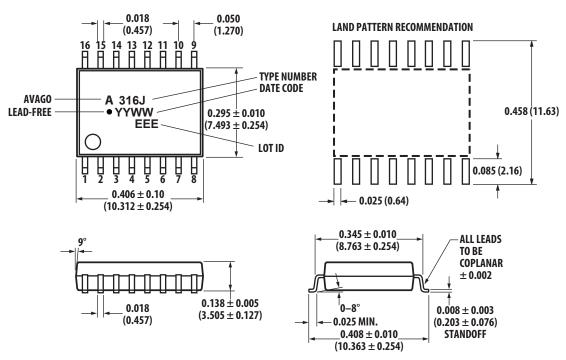

# Package Outline Drawings 16-Lead Surface Mount

Dimensions in inches (millimeters)

#### **Notes:**

Initial and continued variation in the color of the HCPL-316J's white mold compound is normal and does note affect device performance or reliability.

Floating Lead Protrusion is 0.25 mm (10 mils) max.

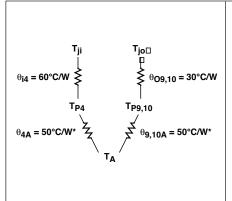

# **Package Characteristics**

All specifications and figures are at the nominal (typical) operating conditions of  $V_{CC1} = 5 \text{ V}$ ,  $V_{CC2} - V_{EE} = 30 \text{ V}$ ,  $V_{E} - V_{EE} = 0 \text{ V}$ , and  $T_{A} = +25 ^{\circ}\text{C}$ .

| Parameter                            | Symbol             | Min. | Тур.             | Max. | Units            | Test Conditions            | Note  |

|--------------------------------------|--------------------|------|------------------|------|------------------|----------------------------|-------|

| Input-Output Momentary               | V <sub>ISO</sub>   | 5000 |                  |      | V <sub>rms</sub> | RH < 50%, t = 1 min.,      | 1, 2, |

| Withstand Voltage                    |                    |      |                  |      |                  | $T_A = 25^{\circ}C$        | 3     |

| Resistance (Input-Output)            | R <sub>I-O</sub>   |      | >10 <sup>9</sup> |      | Ω                | V <sub>I-O</sub> = 500 Vdc | 3     |

| Capacitance (Input-Output)           | C <sub>I-O</sub>   |      | 1.3              |      | рF               | f = 1 MHz                  |       |

| Output IC-to-Pins 9 &10              | θ <sub>09-10</sub> |      | 30               |      | °C/W             | T <sub>A</sub> = 100°C     |       |

| Thermal Resistance                   |                    |      |                  |      |                  |                            |       |

| Input IC-to-Pin 4 Thermal Resistance | $\theta_{l4}$      |      | 60               |      |                  |                            |       |

# **Recommended Pb-Free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision). Non-Halide Flux should be used.

# **Regulatory Information**

The HCPL-316J has been approved by the following organizations:

#### **IEC/EN/DIN EN 60747-5-2**

Approved under: IEC 60747-5-5:1997 + A1:2002 EN 60747-5-2:2001 + A1:2002 DIN EN 60747-5-2 (VDE 0884 Teil 2):2003-01.

#### UL

Recognized under UL 1577, component recognition program, File E55361.

#### CSA

Approved under CSA Component Acceptance Notice #5, File CA 88324.

#### IEC/EN/DIN EN 60747-5-2 Insulation Characteristics\*

| Description                                                                       | Symbol                  | Characteristic | Unit              |

|-----------------------------------------------------------------------------------|-------------------------|----------------|-------------------|

| Installation classification per DIN VDE 0110/1.89, Table 1                        |                         |                |                   |

| for rated mains voltage ≤ 150 Vrms                                                |                         | I - IV         |                   |

| for rated mains voltage ≤ 300 Vrms                                                |                         | I - IV         |                   |

| for rated mains voltage ≤ 600 Vrms                                                |                         | I - IV         |                   |

| for rated mains voltage ≤ 1000Vrms                                                |                         | I - III        |                   |

| Climatic Classification                                                           |                         | 55/100/21      |                   |

| Pollution Degree (DIN VDE 0110/1.89)                                              |                         | 2              |                   |

| Maximum Working Insulation Voltage                                                | V <sub>IORM</sub>       | 1230           | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method b**                                          |                         |                |                   |

| $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1$ sec,       | $V_{PR}$                | 2306           | $V_{PEAK}$        |

| Partial Discharge < 5 pC                                                          |                         |                |                   |

| Input to Output Test Voltage, Method a**                                          |                         |                |                   |

| $V_{IORM} \times 1.6 = V_{PR}$ , Type and Sample Test, $t_m = 10$ sec,            | $V_{PR}$                | 1968           | $V_{PEAK}$        |

| Partial Discharge < 5 pC                                                          |                         |                |                   |

| Highest Allowable Overvoltage** (Transient Overvoltage t <sub>ini</sub> = 60 sec) | V <sub>IOTM</sub>       | 8000           | V <sub>PEAK</sub> |

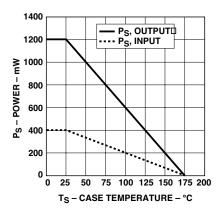

| Safety-limiting values – maximum values allowed in the event of a failure,        |                         |                |                   |

| also see Figure 2.                                                                |                         |                |                   |

| Case Temperature                                                                  | $T_S$                   | 175            | °C                |

| Input Power                                                                       | P <sub>S</sub> , INPUT  | 400            | mW                |

| Output Power                                                                      | P <sub>S</sub> , OUTPUT | 1200           | mW                |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V                 | R <sub>S</sub>          | >109           | Ω                 |

<sup>\*</sup>Isolation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in application. Surface mount classification is class A in accordance with CECCOO802.

<sup>\*\*</sup>Refer to the optocoupler section of the Isolation and Control Components Designer's Catalog, under Product Safety Regulations section IEC/EN/DIN EN 60747-5-2, for a detailed description of Method a and Method b partial discharge test profiles.

Figure 2. Dependence of safety limiting values on temperature.

# **Insulation and Safety Related Specifications**

| Parameter                                            | Symbol | Value | Units | Conditions                                                                                                                         |

|------------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap<br>(Clearance)              | L(101) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External Tracking<br>(Creepage)              | L(102) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal Plastic Gap<br>(Internal Clearance) |        | 0.5   | mm    | Through insulation distance conductor to conductor, usually the straight line distance thickness between the emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking Index)  | CTI    | >175  | Volts | DIN IEC 112/VDE 0303 Part 1                                                                                                        |

| Isolation Group                                      |        | Illa  |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                       |

# **Absolute Maximum Ratings**

| Parameter                         | Symbol                                | Min.                  | Max.                                     | Units | Note |

|-----------------------------------|---------------------------------------|-----------------------|------------------------------------------|-------|------|

| Storage Temperature               | T <sub>s</sub>                        | -55                   | 125                                      | °C    |      |

| Operating Temperature             | T <sub>A</sub>                        | -40                   | 100                                      | -     |      |

| Output IC Junction Temperature    | Тј                                    |                       | 125                                      | -     | 4    |

| Peak Output Current               | I <sub>o(peak)</sub>                  |                       | 2.5                                      | А     | 5    |

| Fault Output Current              | I <sub>FAULT</sub>                    |                       | 8.0                                      | mA    |      |

| Positive Input Supply Voltage     | V <sub>CC1</sub>                      | -0.5                  | 5.5                                      | Volts |      |

| Input Pin Voltages                | $V_{IN+}$ , $V_{IN-}$ and $V_{RESET}$ | -0.5                  | V <sub>CC1</sub>                         | -     |      |

| Total Output Supply Voltage       | (V <sub>CC2</sub> - V <sub>EE</sub> ) | -0.5                  | 35                                       | -     |      |

| Negative Output Supply Voltage    | (V <sub>E</sub> - V <sub>EE</sub> )   | -0.5                  | 15                                       | -     | 6    |

| Positive Output Supply Voltage    | (V <sub>CC2</sub> - V <sub>E</sub> )  | -0.5                  | 35 - (V <sub>E</sub> - V <sub>EE</sub> ) | -     |      |

| Gate Drive Output Voltage         | V <sub>o(peak)</sub>                  | -0.5                  | V <sub>CC2</sub>                         | -     |      |

| Collector Voltage                 | Vc                                    | V <sub>EE</sub> + 5 V | V <sub>CC2</sub>                         | -     |      |

| DESAT Voltage                     | V <sub>DESAT</sub>                    | V <sub>E</sub>        | V <sub>E</sub> + 10                      | -     |      |

| Output IC Power Dissipation       | P <sub>O</sub>                        |                       | 600                                      | mW    | 4    |

| Input IC Power Dissipation        | P <sub>I</sub>                        |                       | 150                                      | -     |      |

| Solder Reflow Temperature Profile | See                                   | Package Outline       | Drawings section                         |       |      |

# **Recommended Operating Conditions**

| Parameter                      | Symbol                                | Min.                | Max.                                     | Units | Note |

|--------------------------------|---------------------------------------|---------------------|------------------------------------------|-------|------|

| Operating Temperature          | T <sub>A</sub>                        | -40                 | +100                                     | °C    |      |

| Input Supply Voltage           | V <sub>CC1</sub>                      | 4.5                 | 5.5                                      | Volts | 28   |

| Total Output Supply Voltage    | (V <sub>CC2</sub> - V <sub>EE</sub> ) | 15                  | 30                                       | -     | 9    |

| Negative Output Supply Voltage | (V <sub>E</sub> - V <sub>EE</sub> )   | 0                   | 15                                       | -     | 6    |

| Positive Output Supply Voltage | (V <sub>CC2</sub> - V <sub>E</sub> )  | 15                  | 30 - (V <sub>E</sub> - V <sub>EE</sub> ) | -     |      |

| Collector Voltage              | V <sub>C</sub>                        | V <sub>EE</sub> + 6 | V <sub>CC2</sub>                         | -     |      |

# **Electrical Specifications (DC)**

Unless otherwise noted, all typical values at  $T_A=25^{\circ}\text{C}$ ,  $V_{CC1}=5\text{ V}$ , and  $V_{CC2}-V_{EE}=30\text{ V}$ ,  $V_E-V_{EE}=0\text{ V}$ ; all Minimum/Maximum specifications are at Recommended Operating Conditions.

| Parameter                                       | Symbol                                                         | Min.                 | Тур.                 | Max.                 | Units | Test Conditions                                                                    | Fig.              | Note      |

|-------------------------------------------------|----------------------------------------------------------------|----------------------|----------------------|----------------------|-------|------------------------------------------------------------------------------------|-------------------|-----------|

| Logic Low Input Voltages                        | V <sub>IN+L</sub> , V <sub>IN-L</sub> ,<br>V <sub>RESETL</sub> |                      |                      | 0.8                  | V     |                                                                                    |                   |           |

| Logic High Input Voltages                       | V <sub>IN+H</sub> , V <sub>IN-H</sub> ,<br>V <sub>RESETH</sub> | 2.0                  |                      |                      | _     |                                                                                    |                   |           |

| Logic Low Input Currents                        | I <sub>IN+L</sub> , I <sub>IN-L</sub> ,<br>I <sub>RESETL</sub> | -0.5                 | -0.4                 |                      | mA    | V <sub>IN</sub> = 0.4 V                                                            |                   |           |

| FAULT Logic Low Output<br>Current               | I <sub>FAULTL</sub>                                            | 5.0                  | 12                   |                      | _     | $V_{FAULT} = 0.4 V$                                                                | 30                |           |

| FAULT Logic High Output<br>Current              | I <sub>FAULTH</sub>                                            | -40                  |                      |                      | μΑ    | V <sub>FAULT</sub> = V <sub>CC1</sub>                                              | 31                |           |

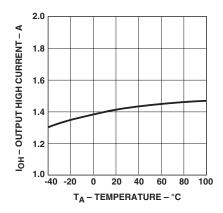

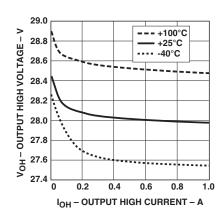

| High Level Output Current                       | I <sub>OH</sub>                                                | -0.5                 | -1.5                 |                      | А     | V <sub>OUT</sub> = V <sub>CC2</sub> - 4 V                                          | 3, 8,             | 7         |

|                                                 |                                                                | -2.0                 |                      |                      | _     | $V_{OUT} = V_{CC2} - 15 \text{ V}$                                                 | 32                | 5         |

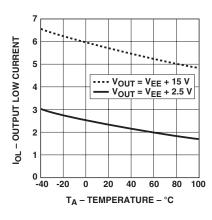

| Low Level Output Current                        | I <sub>OL</sub>                                                | 0.5                  | 2.3                  |                      | -     | $V_{OUT} = V_{EE} + 2.5 \text{ V}$                                                 | 4, 9,             | 7         |

|                                                 |                                                                | 2.0                  |                      |                      | _     | $V_{OUT} = V_{EE} + 15 \text{ V}$                                                  | 33                | 5         |

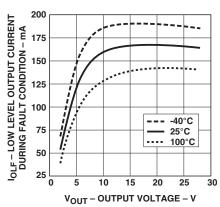

| Low Level Output Current During Fault Condition | I <sub>OLF</sub>                                               | 90                   | 160                  | 230                  | mA    | $V_{OUT} - V_{EE} = 14 V$                                                          | 5, 34             | 8         |

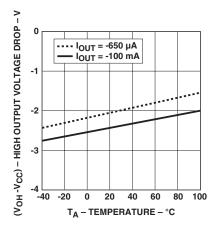

| High Level Output Voltage                       | V <sub>OH</sub>                                                | V <sub>C</sub> - 3.5 | V <sub>C</sub> - 2.5 | V <sub>C</sub> - 1.5 | V     | I <sub>OUT</sub> = -100 mA                                                         | 6, 8,             | 9, 10, 11 |

|                                                 |                                                                | V <sub>C</sub> -2.9  | V <sub>C</sub> - 2.0 | V <sub>C</sub> - 1.2 | _     | I <sub>OUT</sub> = -650 μA                                                         | 35                |           |

|                                                 |                                                                |                      |                      | V <sub>C</sub>       | _     | I <sub>OUT</sub> = 0                                                               |                   |           |

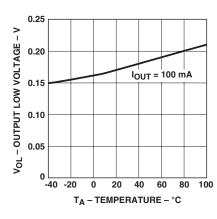

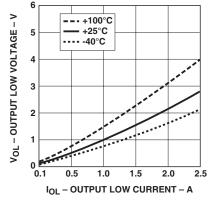

| Low Level Output Voltage                        | V <sub>OL</sub>                                                |                      | 0.17                 | 0.5                  | _     | I <sub>OUT</sub> = 100 mA                                                          | 7, 9,<br>36       | 26        |

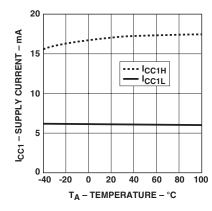

| High Level Input Supply<br>Current              | Ісс1н                                                          |                      | 17                   | 22                   | mA    | $V_{IN+} = V_{CC1} = 5.5 \text{ V},$<br>$V_{IN-} = 0 \text{ V}$                    | 10, 37<br>38      |           |

| Low Level Input Supply<br>Current               | I <sub>CCIL</sub>                                              |                      | 6                    | 11                   | _     | $V_{IN+} = V_{IN-} = 0 V,$<br>$V_{CC1} = 5.5 V$                                    | _                 |           |

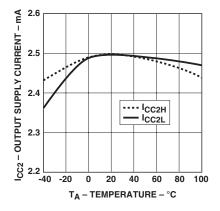

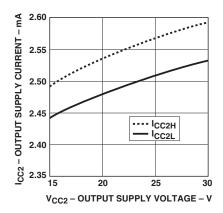

| Output Supply Current                           | I <sub>CC2</sub>                                               |                      | 2.5                  | 5                    | _     | V <sub>OUT</sub> open                                                              | 11, 12,<br>39, 40 | 11        |

| Low Level Collector Current                     | I <sub>CL</sub>                                                |                      | 0.3                  | 1.0                  | _     | I <sub>OUT</sub> = 0                                                               | 15, 59            | 27        |

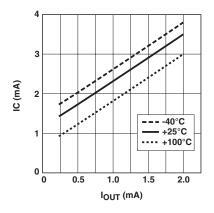

| High Level Collector Current                    | I <sub>CH</sub>                                                |                      | 0.3                  | 1.3                  | _     | I <sub>OUT</sub> = 0                                                               | 15,58             | 27        |

|                                                 |                                                                |                      | 1.8                  | 3.0                  | _     | $I_{OUT} = -650 \mu\text{A}$                                                       | 15,57             |           |

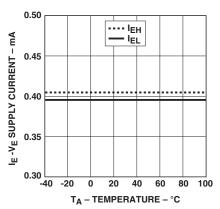

| V <sub>E</sub> Low Level Supply<br>Current      | I <sub>EL</sub>                                                | -0.7                 | -0.4                 | 0                    | _     |                                                                                    | 14, 61            |           |

| V <sub>E</sub> High Level Supply<br>Current     | I <sub>EH</sub>                                                | -0.5                 | -0.14                | 0                    | _     |                                                                                    | 14, 40            | 25        |

| Blanking Capacitor                              | I <sub>CHG</sub>                                               | -0.13                | -0.25                | -0.33                | _     | V <sub>DESAT</sub> = 0 - 6 V                                                       | 13, 41            | 11, 12    |

| Charging Current                                |                                                                | -0.18                | -0.25                | -0.33                | _     | $V_{DESAT} = 0 - 6 \text{ V},$<br>$T_A = 25^{\circ}\text{C} - 100^{\circ}\text{C}$ | _                 |           |

| Blanking Capacitor<br>Discharge Current         | I <sub>DSCHG</sub>                                             | 10                   | 50                   |                      | _     | $V_{DESAT} = 7 V$                                                                  | 42                |           |

| UVLO Threshold                                  | V <sub>UVLO+</sub>                                             | 11.6                 | 12.3                 | 13.5                 | V     | V <sub>OUT</sub> > 5 V                                                             | 43                | 9, 11, 13 |

|                                                 | V <sub>UVLO-</sub>                                             |                      | 11.1                 | 12.4                 | _     | V <sub>OUT</sub> < 5 V                                                             |                   | 9, 11, 14 |

| UVLO Hysteresis                                 | (V <sub>UVLO+</sub> -<br>V <sub>UVLO-</sub> )                  | 0.4                  | 1.2                  |                      | _     | -                                                                                  | _                 |           |

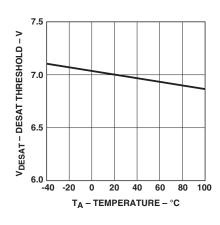

| DESAT Threshold                                 | V <sub>DESAT</sub>                                             | 6.5                  | 7.0                  | 7.5                  | _     | $V_{CC2} - V_E > V_{UVLO}$                                                         | 16, 44            | 11        |

|                                                 |                                                                |                      |                      |                      |       |                                                                                    |                   |           |

# Switching Specifications (AC)

Unless otherwise noted, all typical values at  $T_A=25^{\circ}\text{C}$ ,  $V_{CC1}=5\text{ V}$ , and  $V_{CC2}-V_{EE}=30\text{ V}$ ,  $V_E-V_{EE}=0\text{ V}$ ; all Minimum/Maximum specifications are at Recommended Operating Conditions.

| Parameter                                                      | Symbol                                        | Min.  | Тур. | Max. | Units | Test Conditions                                                          | Fig.                   | Note  |

|----------------------------------------------------------------|-----------------------------------------------|-------|------|------|-------|--------------------------------------------------------------------------|------------------------|-------|

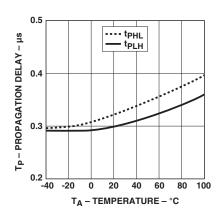

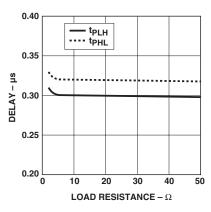

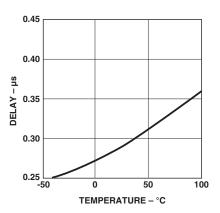

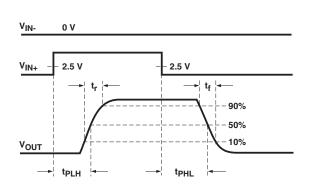

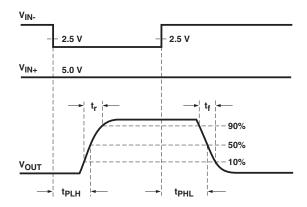

| V <sub>IN</sub> to High Level Output<br>Propagation Delay Time | t <sub>PLH</sub>                              | 0.10  | 0.30 | 0.50 | μs    | Rg = $10 \Omega$<br>Cg = $10 \text{ nF}$ ,                               | 17,18,19,<br>20,21,22, | 15    |

| V <sub>IN</sub> to Low Level Output<br>Propagation Delay Time  | t <sub>PHL</sub>                              | 0.10  | 0.32 | 0.50 | _     | f = 10 kHz,<br>Duty Cycle = 50%                                          | 45,54,55               |       |

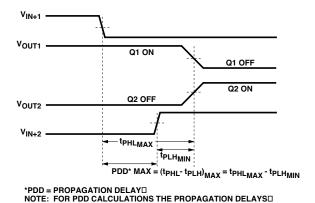

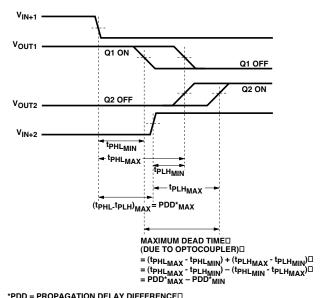

| Pulse Width Distortion                                         | PWD                                           | -0.30 | 0.02 | 0.30 | _     |                                                                          |                        | 16,17 |

| Propagation Delay Difference<br>Between Any Two Parts          | (t <sub>PHL</sub> - t <sub>PLH</sub> )<br>PDD | -0.35 |      | 0.35 | _     |                                                                          |                        | 17,18 |

| 10% to 90% Rise Time                                           | t <sub>r</sub>                                |       | 0.1  |      | _     |                                                                          | 45                     |       |

| 90% to 10% Fall Time                                           | t <sub>f</sub>                                |       | 0.1  |      | _     |                                                                          |                        |       |

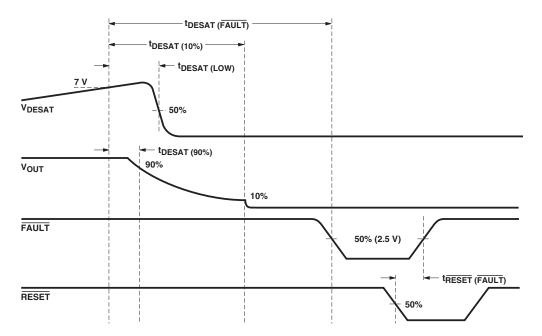

| DESAT Sense to 90% V <sub>OUT</sub> Delay                      | t <sub>DESAT</sub> (90%)                      |       | 0.3  | 0.5  | _     | Rg = $10 \Omega$ ,<br>Cg = $10 \text{ nF}$                               | 23,56                  | 19    |

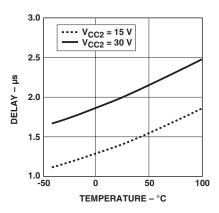

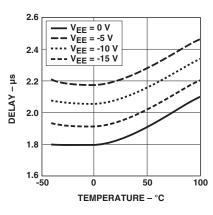

| DESAT Sense to 10% V <sub>OUT</sub> Delay                      | t <sub>DESAT(10%)</sub>                       |       | 2.0  | 3.0  | _     | V <sub>CC2</sub> - V <sub>EE</sub> = 30 V                                | 24,28,<br>46,56        | -     |

| DESAT Sense to Low Level FAULT<br>Signal Delay                 | t <sub>DESAT(FAULT)</sub>                     |       | 1.8  | 5    | _     |                                                                          | 25,47,<br>56           | 20    |

| DESAT Sense to DESAT Low<br>Propagation Delay                  | t <sub>DESAT(LOW)</sub>                       |       | 0.25 |      | _     |                                                                          | 56                     | 21    |

| RESET to High Level FAULT Signal Delay                         | treset(FAULT)                                 | 3     | 7    | 20   | _     |                                                                          | 26,27,<br>56           | 22    |

| RESET Signal Pulse Width                                       | PWRESET                                       | 0.1   |      |      | _     |                                                                          |                        |       |

| UVLO to V <sub>OUT</sub> High Delay                            | t <sub>UVLO ON</sub>                          |       | 4.0  |      | _     | $V_{CC2} = 1.0 \text{ ms}$                                               | 49                     | 13    |

| UVLO to V <sub>OUT</sub> Low Delay                             | tuvlo off                                     |       | 6.0  |      | _     | ramp                                                                     |                        | 14    |

| Output High Level Common Mode<br>Transient Immunity            | CM <sub>H</sub>                               | 15    | 30   |      | kV/μs | $T_A = 25$ °C,<br>$V_{CM} = 1500 \text{ V},$<br>$V_{CC2} = 30 \text{ V}$ | 50,51,<br>52,53        | 23    |

| Output Low Level Common Mode<br>Transient Immunity             | CM <sub>L</sub>                               | 15    | 30   |      | _     | $T_A = 25$ °C,<br>$V_{CM} = 1500 \text{ V},$<br>$V_{CC2} = 30 \text{ V}$ |                        | 24    |

#### Notes

- 1. In accordance with UL1577, each optocoupler is proof tested by applying an insulation test voltage ≥6000 Vrms for 1 second. This test is performed before the 100% production test for partial discharge (method b) shown in IEC/EN/DIN EN 60747-5-2 Insulation Characteristic Table, if applicable.

- 2. The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating refer to your equipment level safety specification or IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table.

- 3. Device considered a two terminal device: pins 1 8 shorted together and pins 9 16 shorted together.

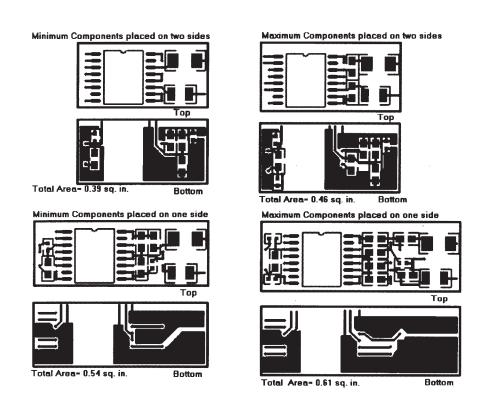

- 4. In order to achieve the absolute maximum power dissipation specified, pins 4, 9, and 10 require ground plane connections and may require airflow. See the Thermal Model section in the application notes at the end of this data sheet for details on how to estimate junction temperature and power dissipation. In most cases the absolute maximum output IC junction temperature is the limiting factor. The actual power dissipation achievable will depend on the application environment (PCB Layout, air flow, part placement, etc.). See the Recommended PCB Layout section in the application notes for layout considerations. Output IC power dissipation is derated linearly at 10 mW/°C above 90°C. Input IC power dissipation does not require derating.

- 5. Maximum pulse width = 10  $\mu$ s, maximum duty cycle = 0.2%. This value is intended to allow for component tolerances for designs with  $I_O$  peak minimum = 2.0 A. See Applications section for additional details on  $I_{OH}$  peak. Derate linearly from 3.0 A at +25°C to 2.5 A at +100°C. This compensates for increased  $I_{OPEAK}$  due to changes in  $V_{OL}$  over temperature.

- 6. This supply is optional. Required only when negative gate drive is implemented.

- 7. Maximum pulse width =  $50 \mu s$ , maximum duty cycle = 0.5%.

- 8. See the Slow IGBT Gate Discharge During Fault Condition section in the applications notes at the end of this data sheet for further details.

- 9. 15 V is the recommended minimum operating positive supply voltage  $(V_{CC2} V_E)$  to ensure adequate margin in excess of the maximum  $V_{U-VLO+}$  threshold of 13.5 V. For High Level Output Voltage testing,  $V_{OH}$  is measured with a dc load current. When driving capacitive loads,  $V_{OH}$  will approach  $V_{CC}$  as  $I_{OH}$  approaches zero units.

- 10. Maximum pulse width = 1.0 ms, maximum duty cycle = 20%.

- 11. Once V<sub>OUT</sub> of the HCPL-316J is allowed to go high (V<sub>CC2</sub> V<sub>E</sub> > V<sub>UVLO</sub>), the DESAT detection feature of the HCPL-316J will be the primary source of IGBT protection. UVLO is needed to ensure DESAT is functional. Once V<sub>UVLO+</sub> > 11.6 V, DESAT will remain functional until V<sub>UVLO-</sub> < 12.4 V. Thus, the DESAT detection and UVLO features of the HCPL-316J work in conjunction to ensure constant IGBT protection.

- 12. See the Blanking Time Control section in the applications notes at the end of this data sheet for further details.

- 13. This is the "increasing" (i.e. turn-on or "positive going" direction) of V<sub>CC2</sub>-V<sub>E</sub>.

- 14. This is the "decreasing" (i.e. turn-off or "negative going" direction) of  $V_{CC2}$ - $V_E$ .

- 15. This load condition approximates the gate load of a 1200 V/75A IGBT.

- 16. Pulse Width Distortion (PWD) is defined as  $\left|t_{PHL}-t_{PLH}\right|$  for any given unit.

- 17. As measured from  $V_{IN+}$ ,  $V_{IN-}$  to  $V_{OUT}$ .

- 18. The difference between tpHL and tpLH between any two HCPL-316J parts under the same test conditions.

- 19. Supply Voltage Dependent.

- 20. This is the amount of time from when the DESAT threshold is exceeded, until the FAULT output goes low.

- 21. This is the amount of time the DESAT threshold must be exceeded before V<sub>OUT</sub> begins to go low, and the FAULT output to go low.

- 22. This is the amount of time from when <u>RESET</u> is asserted low, until <u>FAULT</u> output goes high. The minimum <u>specification</u> of 3 µs is the guaranteed minimum <u>FAULT</u> signal pulse width when the HCPL-316J is configured for Auto-Reset. See the Auto-Reset section in the applications notes at the end of this data sheet for further details.

- 23. Common mode transient immunity in the high state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in the high state (i.e.,  $V_O > 15$  V or <u>FAULT</u> > 2 V). A 100 pF and a 3K  $\Omega$  pull-up resistor is needed in fault detection mode.

- 24. Common mode transient immunity in the low state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in a low state (i.e.,  $V_{CM} < 1.0 \text{ V}$  or FAULT < 0.8 V).

- 25. Does not include LED2 current during fault or blanking capacitor discharge current.

- 26. To clamp the output voltage at V<sub>CC</sub> 3 V<sub>BE</sub>, a pull-down resistor between the output and V<sub>EE</sub> is recommended to sink a static current of 650 μA while the output is high. See the Output Pull-Down Resistor section in the application notes at the end of this data sheet if an output pull-down resistor is not used.

- 27. The recommended output pull-down resistor between  $V_{OUT}$  and  $V_{EE}$  does not contribute any output current when  $V_{OUT} = V_{EE}$ .

- 28. In most applications  $V_{CC1}$  will be powered up first (before  $V_{CC2}$ ) and powered down last (after  $V_{CC2}$ ). This is desirable for maintaining control of the IGBT gate. In applications where  $V_{CC2}$  is powered up first, it is important to ensure that  $V_{in+}$  remains low until  $V_{CC1}$  reaches the proper operating voltage (minimum 4.5 V) to avoid any momentary instability at the output during  $V_{CC1}$  ramp-up or ramp-down.

#### **Performance Plots**

Figure 3. I<sub>OH</sub> vs. temperature.

Figure 4. I<sub>OL</sub> vs. temperature.

Figure 5.  $I_{OLF}$  vs.  $V_{OUT}$ .

Figure 6.  $V_{OH}$  vs. temperature.

Figure 7.  $V_{\text{OL}}$  vs. temperature.

Figure 8. V<sub>OH</sub> vs. I<sub>OH</sub>.

Figure 9: V<sub>OL</sub> vs. I<sub>OL</sub>.

Figure 10.  $I_{CC1}$  vs. temperature.

Figure 11:  $I_{CC2}$  vs. t emperature.

-0.15

-0.15

-0.20

-0.25

-0.30

-40 -20 0 20 40 60 80 100

T<sub>A</sub> - TEMPERATURE - °C

Figure 12. I<sub>CC2</sub> vs. V<sub>CC2</sub>.

Figure 13. I<sub>CHG</sub> vs. temperature.

Figure 14. I<sub>E</sub> vs. temperature.

Figure 15. I<sub>C</sub> vs. I<sub>OUT</sub>.

Figure 16. DESAT threshold vs. temperature.

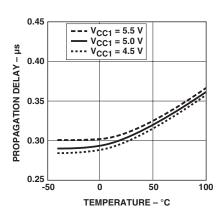

Figure 17. Propagation delay vs. temperature.

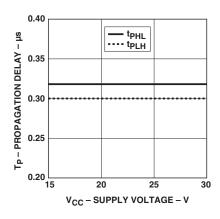

Figure 18. Propagation delay vs. supply voltage.

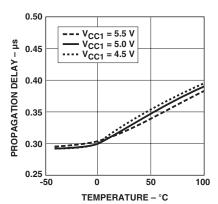

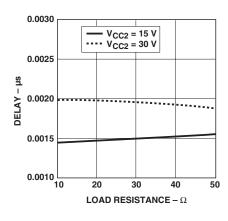

Figure 19.  $V_{\text{IN}}$  to high propagation delay vs. temperature.

Figure 20.  $\ensuremath{V_{\text{IN}}}$  to low propagation delay vs. temperature.

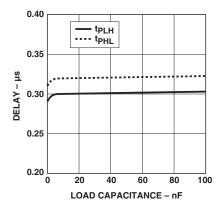

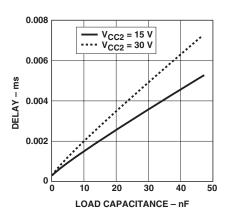

Figure 21. Propagation delay vs. load capacitance.

$\label{eq:Figure 22.Propagation delay vs. load resistance.}$

Figure 23. DESAT sense to 90%  $\mbox{\ensuremath{V_{out}}}$  delay vs. temperature.

Figure 24. DESAT sense to 10%  $\ensuremath{\text{V}_{\text{out}}}$  delay vs. temperature.

Figure 25. DESAT sense to low level fault signal delay vs. temperature.

Figure 26. DESAT sense to  $10\%\,V_{out}$  delay vs. load capacitance.

Figure 27. DESAT sense to 10%  $\ensuremath{V_{out}}$  delay vs. load resistance.

Figure 28. RESET to high level fault signal delay vs. temperature.

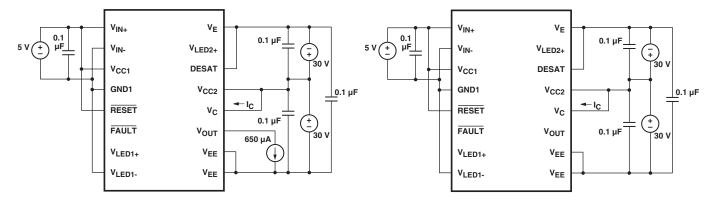

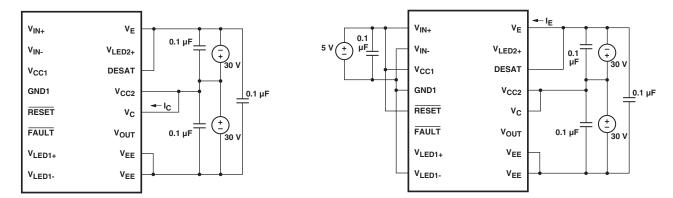

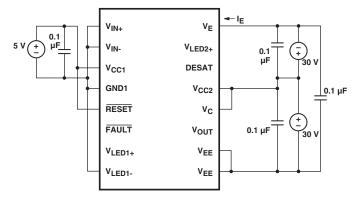

# **Test Circuit Diagrams**

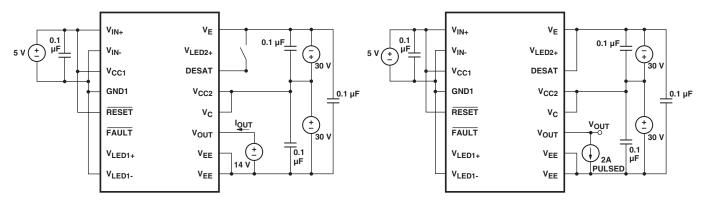

Figure 30. IFAULTL test circuit.

Figure 31. IFAULTH test circuit.

Figure 32. I<sub>OH</sub> pulsed test circuit.

Figure 33. I<sub>OL</sub> pulsed test circuit.

Figure 34. l<sub>OLF</sub> test circuit.

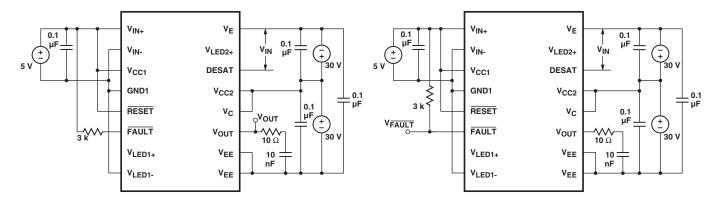

Figure 35.  $V_{OH}$  pulsed test circuit.

Figure 36. V<sub>OL</sub> test circuit.

Figure 37.  $I_{\text{CC1H}}$  test circuit.

Figure 38. I<sub>CC1L</sub> test circuit.

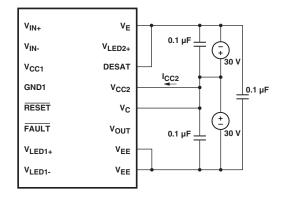

Figure 39. I<sub>CC2H</sub> test circuit.

Figure 40.  $I_{\text{CC2L}}$  test circuit.

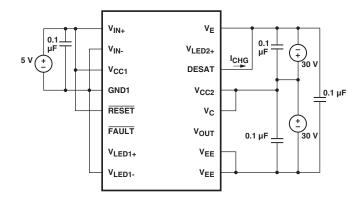

Figure 41.  $I_{CHG}$  pulsed test circuit.

Figure 42. I<sub>DSCHG</sub> test circuit.

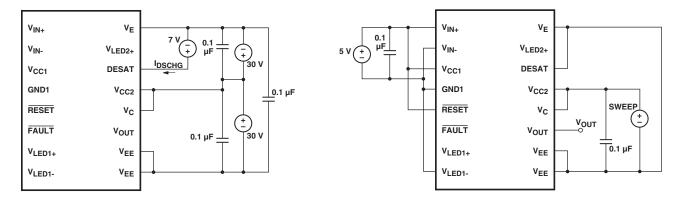

Figure 43. UVLO threshold test circuit.

Figure 44. DESAT threshold test circuit.

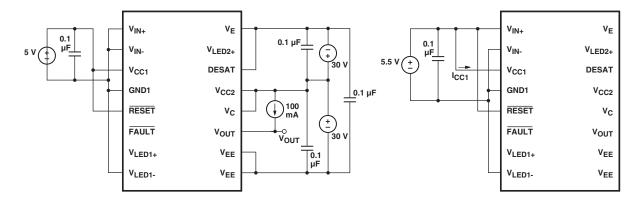

Figure 45. t<sub>PLH</sub>, t<sub>PHL</sub>, t<sub>r</sub>, t<sub>f</sub> test circuit.

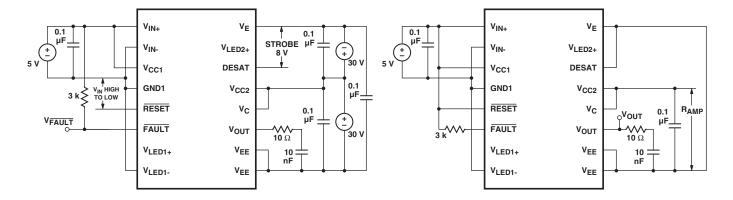

Figure 46.  $t_{DESAT(10\%)}$  test circuit.

Figure 47.  $t_{DESAT(F\overline{AULT})}$  test circuit.

Figure 48. t<sub>RESET(FAULT)</sub> test circuit.

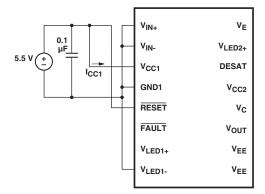

Figure 49. UVLO delay test circuit.

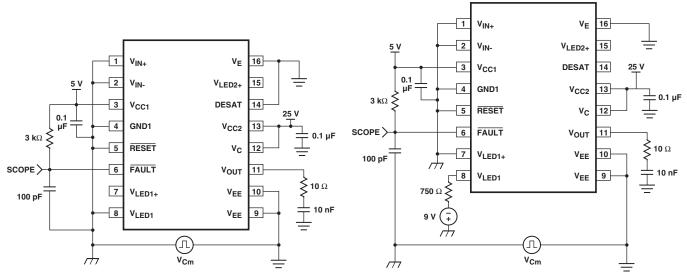

Figure 50. CMR test circuit, LED2 off.

Figure 51. CMR test circuit, LED2 on.

Figure 52. CMR test circuit, LED1 off.

Figure 53. CMR test circuit, LED1 on.

Figure 54.  $V_{OUT}$  propagation delay waveforms, noninverting configuration.

Figure 55.  $V_{\text{OUT}}$  propagation delay waveforms, inverting configuration.

Figure 56. Desat, V<sub>OUT</sub>, fault, reset delay waveforms.

Figure 57. I<sub>CH</sub> test circuit.

Figure 58. I<sub>CH</sub> test circuit.

Figure 59.  $I_{\text{CL}}$  test circuit.

Figure 60. I<sub>EH</sub> test circuit.

Figure 61. I<sub>EL</sub> test circuit.

# **Typical Application/Operation**

#### Introduction to Fault Detection and Protection

The power stage of a typical three phase inverter is susceptible to several types of failures, most of which are potentially destructive to the power IGBTs. These failure modes can be grouped into four basic categories: phase and/or rail supply short circuits due to user misconnect or bad wiring, control signal failures due to noise or computational errors, overload conditions induced by the load, and component failures in the gate drive circuitry. Under any of these fault conditions, the current through the IGBTs can increase rapidly, causing excessive power dissipation and heating. The IGBTs become damaged when the current load approaches the saturation current of the device, and the collector to emitter voltage rises above the saturation voltage level. The drastically increased power dissipation very quickly overheats the power device and destroys it. To prevent damage to the drive, fault protection must be implemented to reduce or turn-off the overcurrents during a fault condition.

A circuit providing fast local fault detection and shutdown is an ideal solution, but the number of required components, board space consumed, cost, and complexity have until now limited its use to high performance drives. The features which this circuit must have are high speed, low cost, low resolution, low power dissipation, and small size.

**Applications Information**The HCPL-316J satisfies these criteria by combining a high speed, high output current driver, high voltage optical isolation between the input and output, local IGBT desaturation detection and shut down, and an optically isolated fault status feedback signal into a single 16-pin surface mount package.

The fault detection method, which is adopted in the HCPL-316J, is to monitor the saturation (collector) voltage of the IGBT and to trigger a local fault shutdown sequence if the collector voltage exceeds a predetermined threshold. A small gate discharge device slowly reduces the high short circuit IGBT current to prevent damaging voltage spikes. Before the dissipated energy can reach destructive levels, the IGBT is shut off. During the off state of the IGBT, the fault detect circuitry is simply disabled to prevent false 'fault' signals.

The alternative protection scheme of measuring IGBT current to prevent desaturation is effective if the short circuit capability of the power device is known, but this method will fail if the gate drive voltage decreases enough to only partially turn on the IGBT. By directly measuring the collector voltage, the HCPL-316J limits the power dissipation in the IGBT even with insufficient gate drive voltage. Another more subtle advantage of the desaturation detection method is that power dissipation in the IGBT is monitored, while the current sense method relies on a preset current threshold to predict the safe limit of operation. Therefore, an overly-conservative overcurrent threshold is not needed to protect the IGBT.

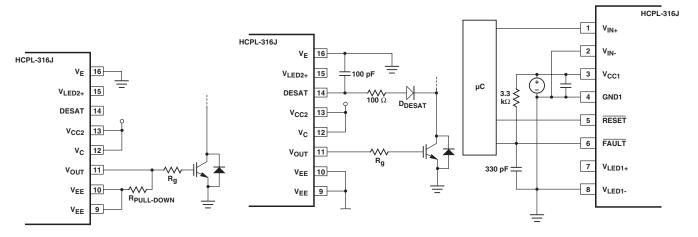

### **Recommended Application Circuit**

The HCPL-316J has both inverting and non-inverting gate control inputs, an active low reset input, and an open collector fault output suitable for wired 'OR' applications. The recommended application circuit shown in Figure 62 illustrates a typical gate drive implementation using the HCPL-316J.

The four supply bypass capacitors (0.1  $\mu$ F) provide the large transient currents necessary during a switching transition. Because of the transient nature of the charging currents, a low current (5 mA) power supply suffices. The desat diode and 100 pF capacitor are the necessary external components for the fault detection circuitry. The gate resistor (10  $\Omega$ ) serves to limit gate charge current and indirectly control the IGBT collector voltage rise and fall times. The open collector fault output has a passive 3.3 k $\Omega$  pull-up resistor and a 330 pF filtering capacitor. A 47 k $\Omega$  pulldown resistor on V<sub>OUT</sub> provides a more predictable high level output voltage (V<sub>OH</sub>). In this application, the IGBT gate driver will shut down when a fault is detected and will not resume switching until the microcontroller applies a reset signal.

Figure 62. Recommended application circuit.

# **Description of Operation/Timing**

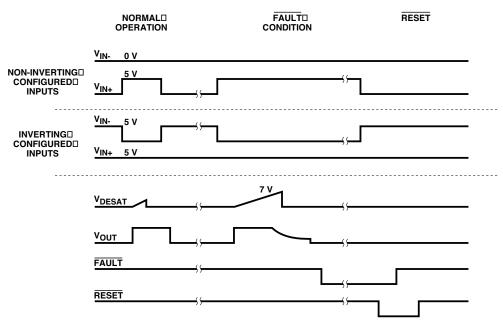

Figure 63 below illustrates input and output waveforms under the conditions of normal operation, a desat fault condition, and normal reset behavior.

### **Normal Operation**

During normal operation,  $V_{OUT}$  of the HCPL-316J is controlled by either  $V_{IN+}$  or  $V_{IN-}$ , with the IGBT collector-to-emitter voltage being monitored through  $D_{DESAT}$ . The FAULT output is high and the RESET input should be held high. See Figure 63.

### **Fault Condition**

When the voltage on the DESAT pin exceeds 7V while the IGBT is on, V<sub>OUT</sub> is slowly brought low in order to "softly" turn-off the IGBT and prevent large di/dt induced voltages. Also activated is an internal feedback channel which brings the FAULT output low for the purpose of notifying the micro-controller of the fault condition. See Figure 63.

#### Reset

The FAULT output remains low until RESET is brought low. See Figure 63. While asserting the RESET pin (LOW), the input pins must be asserted for an output low state ( $V_{IN+}$  is LOW or  $V_{IN-}$  is HIGH). This may be accomplished either by software control (i.e. of the microcontroller) or hardware control (see Figures 73 and 74).

Figure 63. Timing diagram.

# **Slow IGBT Gate Discharge During Fault Condition**

When a desaturation fault is detected, a weak pull-down device in the HCPL-316J output drive stage will turn on to 'softly' turn off the IGBT. This device slowly discharges the IGBT gate to prevent fast changes in drain current that could cause damaging voltage spikes due to lead and wire inductance. During the slow turn off, the large output pull-down device remains off until the output voltage falls below  $V_{\text{EE}} + 2$  Volts, at which time the large pull down device clamps the IGBT gate to  $V_{\text{EE}}$ .

# **DESAT Fault Detection Blanking Time**

The DESAT fault detection circuitry must remain disabled for a short time period following the turn-on of the IGBT to allow the collector voltage to fall below the DESAT the shold. This time period, called the DESAT blanking time, is controlled by the internal DESAT charge current, the DESAT voltage threshold, and the external DESAT capacitor. The nominal blanking time is calculated in terms of external capacitance (CBLANK), FAULT threshold voltage (V<sub>DESAT</sub>), and DESAT charge current (I<sub>CHG</sub>) as t<sub>BLANK</sub> =  $C_{BLANK} \times V_{DESAT}/I_{CHG}$ . The nominal blanking time with the recommended 100 pF capacitor is 100 pF\*7V  $/250 \,\mu\text{A} = 2.8 \,\mu\text{sec}$ . The capacitance value can be scaled slightly to adjust the blanking time, though a value smaller than 100 pF is not recommended. This nominal blanking time also represents the longest time it will take for the HCPL-316J to respond to a DESAT fault condition. If the IGBT is turned on while the collector and emitter are shorted to the supply rails (switching into a short), the soft shut-down sequence will begin after approximately 3 usec. If the IGBT collector and emitter are shorted to the supply rails after the IGBT is already on, the response time will be much quicker due to the parasitic parallel capacitance of the DESAT diode. The recommended 100 pF capacitor should provide adequate blanking as well as fault response times for most applications.

# **Under Voltage Lockout**

The HCPL-316J Under Voltage Lockout (UVLO) feature is designed to prevent the application of insufficient gate voltage to the IGBT by forcing the HCPL-316J output low during power-up. IGBTs typically require gate voltages of 15 V to achieve their rated  $V_{CE(ON)}$  voltage. At gate voltages below 13 V typically, their on-voltage increases dramatically, especially at higher currents. At very low gate voltages (below 10 V), the IGBT may operate in the linear region and quickly overheat. The UVLO function causes the output to be clamped whenever insufficient operating supply (V<sub>CC2</sub>) is applied. Once V<sub>CC2</sub> exceeds V<sub>UVLO+</sub> (the positive-going UVLO threshold), the UVLO clamp is released to allow the device output to turn on in response to input signals. As V<sub>CC2</sub> is increased from 0 V (at some level below V<sub>UVLO+</sub>), first the DESAT protection circuitry becomes active. As V<sub>CC2</sub> is further increased (above V<sub>UVLO+</sub>), the UVLO clamp is released. Before the time the UVLO clamp is released, the DESAT protection is already active. Therefore, the UVLO and DESAT FAULT DETECTION features work together to provide seamless protection regardless of supply voltage ( $V_{CC2}$ ).

#### **Behavioral Circuit Schematic**

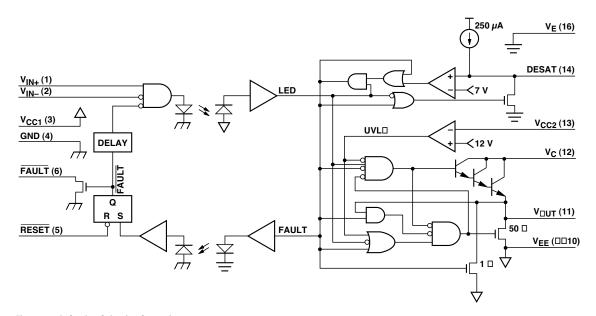

The functional behavior of the HCPL-316J is represented by the logic diagram in Figure 64 which fully describes the interaction and sequence of internal and external signals in the HCPL-316J.

# Input IC

In the normal switching mode, no output fault has been detected, and the low state of the fault latch allows the input signals to control the signal LED. The fault output is in the open-collector state, and the state of the Reset pin does not affect the control of the IGBT gate. When a fault is detected, the FAULT output and signal input are both latched. The fault output changes to an active low state, and the signal LED is forced off (output LOW). The latched condition will persist until the Reset pin is pulled low.

### **Output IC**

Three internal signals control the state of the driver output: the state of the signal LED, as well as the UVLO and Fault signals. If no fault on the IGBT collector is detected, and the supply voltage is above the UVLO threshold, the LED signal will control the driver output state. The driver stage logic includes an interlock to ensure that the pull-up and pull-down devices in the output stage are never on at the same time. If an undervoltage condition is detected, the output will be actively pulled low by the 50x DMOS device, regardless of the LED state. If an IGBT desaturation fault is detected while the signal LED is on, the Fault signal will latch in the high state. The triple darlington AND the 50x DMOS device are disabled, and a smaller 1x DMOS pull-down device is activated to slowly discharge the IGBT gate. When the output drops below two volts, the 50x DMOS device again turns on, clamping the IGBT gate firmly to Vee. The Fault signal remains latched in the high state until the signal LED turns off.

Figure 64. Behavioral circuit schematic.

Figure 65. Output pull-down resistor.

Figure 66. DESAT pin protection.

Figure 67. FAULT pin CMR protection.

# **Other Recommended Components**

The application circuit in Figure 62 includes an output pull-down resistor, a DESAT pin protection resistor, a FAULT pin capacitor (330 pF), and a FAULT pin pull-up resistor.

### **Output Pull-Down Resistor**

During the output high transition, the output voltage rapidly rises to within 3 diode drops of  $V_{CC2}$ . If the output current then drops to zero due to a capacitive load, the output voltage will slowly rise from roughly  $V_{CC2}$ -3( $V_{BE}$ ) to  $V_{CC2}$  within a period of several microseconds. To limit the output voltage to  $V_{CC2}$ -3( $V_{BE}$ ), a pull-down resistor between the output and  $V_{EE}$  is recommended to sink a static current of several 650  $\mu$ A while the output is high. Pull-down resistor values are dependent on the amount of positive supply and can be adjusted according to the formula,  $R_{pull-down} = [V_{CC2}$ -3\*( $V_{BE}$ )]/650  $\mu$ A.

#### **DESAT Pin Protection**

The freewheeling of flyback diodes connected across the IGBTs can have large instantaneous forward voltage transients which greatly exceed the nominal forward voltage of the diode. This may result in a large negative voltage spike on the DESAT pin which will draw substantial current out of the IC if protection is not used. To limit this current to levels that will not damage the IC, a 100 ohm resistor should be inserted in series with the DESAT diode. The added resistance will not alter the DESAT threshold or the DESAT blanking time.

# **Capacitor on FAULT Pin for High CMR**

Rapid common mode transients can affect the fault pin voltage while the fault output is in the high state. A 330 pF capacitor (Fig. 66) should be connected between the fault pin and ground to achieve adequate CMOS noise margins at the specified CMR value of 15 kV/µs. The added capacitance does not increase the fault output delay when a desaturation condition is detected.

### **Pull-up Resistor on FAULT Pin**

The FAULT pin is an open-collector output and therefore requires a pull-up resistor to provide a high-level signal.

#### Driving with Standard CMOS/TTL for High CMR

Capacitive coupling from the isolated high voltage circuitry to the input referred circuitry is the primary CMR limitation. This coupling must be accounted for to achieve high CMR performance. The input pins  $V_{\text{IN-}}$  and  $V_{\text{IN-}}$  must have active drive signals to prevent unwanted switching of the output under extreme common mode transient conditions. Input drive circuits that use pull-up or pull-down resistors, such as open collector configurations, should be avoided. Standard CMOS or TTL drive circuits are recommended.

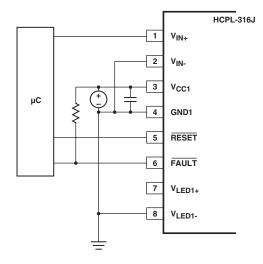

# User-Configuration of the HCPL-316J Input Side

The  $V_{IN+}$ ,  $V_{IN-}$ ,  $\overline{FAULT}$  and  $\overline{RESET}$  input pins make a wide variety of gate control and fault configurations possible, depending on the motor drive requirements. The HCPL-316J has both inverting and noninverting gate control inputs, an open collector fault output suitable for wired 'OR' applications and an active low reset input.

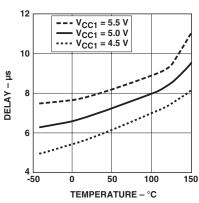

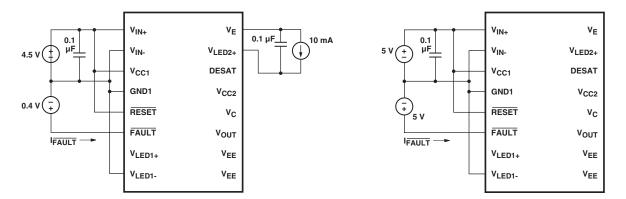

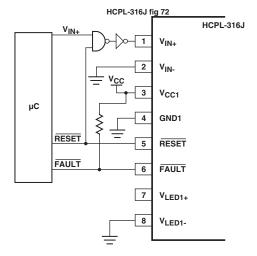

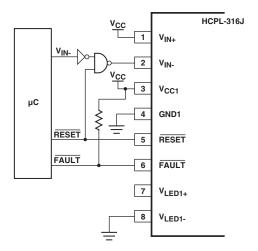

# Driving Input pf HCPL-316J in Non-Inverting/Inverting Mode

The Gate Drive Voltage Output of the HCPL-316J can be configured as inverting or non-inverting using the  $V_{\rm IN-}$  and  $V_{\rm IN+}$  inputs. As shown in Figure 68, when a non-inverting configuration is desired,  $V_{\rm IN-}$  is held low by connecting it to GND1 and  $V_{\rm IN+}$  is toggled. As shown in Figure 69, when an inverting configuration is desired,  $V_{\rm IN+}$  is held high by connecting it to  $V_{\rm CC1}$  and  $V_{\rm IN-}$  is toggled.

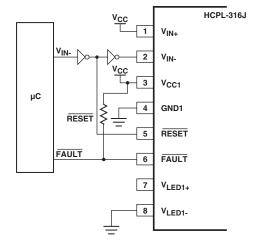

#### Local Shutdown, Local Reset

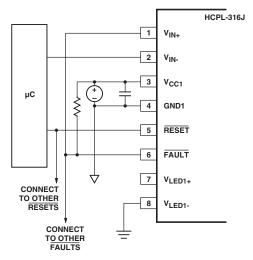

As shown in Figure 70, the fault output of each HCPL-316J gate driver is polled separately, and the individual reset lines are asserted low independently to reset the motor controller after a fault condition.

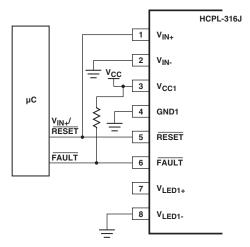

#### Global-Shutdown, Global Reset

As shown in Figure 71, when configured for inverting operation, the HCPL-316J can be configured to shutdown automatically in the event of a fault condition by tying the FAULT output to V<sub>IN+</sub>. For high reliability drives, the open collector FAULT outputs of each HCPL-316J can be wire 'OR'ed together on a common fault bus, forming a single fault bus for interfacing directly to the micro-controller. When any of the six gate drivers detects a fault, the fault output signal will disable all six HCPL-316J gate drivers simultaneously and thereby provide protection against further catastrophic failures.

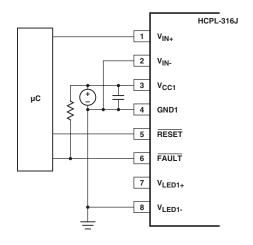

Figure 68. Typical input configuration, noninverting.

Figure 69. Typical Input Configuration, Inverting.

Figure 70. Local shutdown, local reset configuration.

#### **Auto-Reset**

As shown in Figure 72, when the inverting  $V_{IN-}$  input is connected to ground (non-inverting configuration), the HCPL-316J can be configured to reset automatically by connecting RESET to V<sub>IN+</sub>. In this case, the gate control signal is applied to the non-inverting input as well as the reset input to reset the fault latch every switching cycle. During normal operation of the IGBT, asserting the reset input low has no effect. Following a fault condition, the gate driver remains in the latched fault state until the gate control signal changes to the 'gate low' state and resets the fault latch. If the gate control signal is a continuous PWM signal, the fault latch will always be reset by the next time the input signal goes high. This configuration protects the IGBT on a cycle-by-cycle basis and automatically resets before the next 'on' cycle. The fault outputs can be wire 'OR'ed together to alert the microcontroller, but this signal would not be used for control purposes in this (Auto-Reset) configuration. When the HCPL- 316J is configured for Auto-Reset, the guaranteed minimum FAULT signal pulse width is 3 µs.

Figure 71. Global-shutdown, global reset configuration.

Figure 73a. Safe hardware reset for noninverting input configuration (automatically resets for every V<sub>IN+</sub> input).

#### **Resetting Following a Fault Condition**

To resume normal switching operation following a fault condition (FAULT output low), the RESET pin must first be asserted low in order to release the internal fault latch and reset the FAULT output (high). Prior to asserting the RESET pin low, the input (VIN) switching signals must be configured for an output (VOL) low state. This can be handled directly by the microcontroller or by hardwiring to synchronize the RESET signal with the appropriate input signal. Figure 73a shows how to connect the RESET to the V<sub>IN+</sub> signal for safe automatic reset in the noninverting input configuration. Figure 73b shows how to configure the V<sub>IN+</sub>/RESET signals so that a RESET signal from the microcontroller causes the input to be in the "output-off" state. Similarly, Figures 73c and 73d show automatic RESET and microcontroller RESET safe configurations for the inverting input configuration.

Figure 72. Auto-reset configuration.

Figure 73b. Safe hardware reset for noninverting input configuration.

# User-Configuration of the HCPL-316J Output Side R<sub>G</sub> and Optional Resistor R<sub>C</sub>:

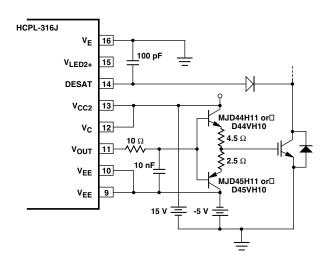

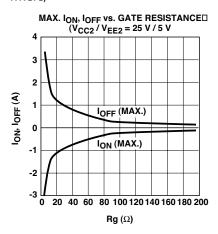

The value of the gate resistor  $R_G$  (along with  $V_{CC2}$  and  $V_{EE}$ ) determines the maximum amount of gate-charging/discharging current ( $I_{ON,PEAK}$  and  $I_{OFF,PEAK}$ ) and thus should be carefully chosen to match the size of the IGBT being driven. Often it is desirable to have the peak gate charge current be somewhat less than the peak discharge current ( $I_{ON,PEAK} < I_{OFF,PEAK}$ ). For this condition, an optional resistor ( $R_C$ ) can be used along with  $R_G$  to independently determine  $I_{ON,PEAK}$  and  $I_{OFF,PEAK}$  without using a steering diode. As an example, refer to Figure 74. Assuming that  $R_G$  is already determined and that the design  $I_{OH,PEAK} =$

0.5 A, the value of  $R_{\text{C}}$  can be estimated in the following wav:

$$R_C + R_G = \frac{[V_{CC2} - V_{OH} - (V_{EE})]}{I_{OH,PEAK}}$$

$$= \frac{[4 \text{ V} - (-5 \text{ V})]}{0.5 \text{ A}}$$

$$= 18 \Omega$$

$$R_C = 8 \Omega$$

See "Power and Layout Considerations" section for more information on calculating value of R<sub>G</sub>.

Figure 73c. Safe hardware reset for inverting input configuration.

Figure 73d. Safe hardware reset for inverting input configuration (automatically resets for every V<sub>IN</sub>. input).

Figure 74. Use of R<sub>C</sub> to further limit I<sub>ON,PEAK</sub>.

# Higher Output Current Using an External Current Buffer:

To increase the IGBT gate drive current, a non-inverting current buffer (such as the npn/pnp buffer shown in Figure 75) may be used. Inverting types are not compatible with the desatura-tion fault protection circuitry and should be avoided. To preserve the slow IGBT turn-off feature during a fault condition, a 10 nF capacitor should be connected from the buffer input to  $V_{EE}$  and a 10  $\Omega$  resistor inserted between the output and the common npn/pnp base. The MJD44H11/MJD45H11 pair is appropriate for currents up to 8A maximum. The D44VH10/D45VH10 pair is appropriate for currents up to 15 A maximum.

Figure 75. Current buffer for increased drive current.

#### **DESAT Diode and DESAT Threshold**

The DESAT diode's function is to conduct forward current, allowing sensing of the IGBT's saturated collectorto-emitter voltage, V<sub>CESAT</sub>, (when the IGBT is "on") and to block high voltages (when the IGBT is "off"). During the short period of time when the IGBT is switching, there is commonly a very high dV<sub>CE</sub>/dt voltage ramp rate across the IGBT's collector-to-emitter. This results in I<sub>CHARGE</sub> (= C<sub>D-DESAT</sub> x dV<sub>CE</sub>/dt) charging current which will charge the blanking capacitor, CBLANK. In order to minimize this charging current and avoid false DESAT triggering, it is best to use fast response diodes. Listed in the below table are fast-recovery diodes that are suitable for use as a DESAT diode (DDESAT). In the recommended application circuit shown in Figure 62, the voltage on pin 14 (DESAT) is  $V_{DESAT} = V_F + V_{CE}$ , (where  $V_F$  is the forward ON voltage of D<sub>DESAT</sub> and V<sub>CE</sub> is the IGBT collector-toemitter voltage). The value of VCE which triggers DESAT to signal a FAULT condition, is nominally 7V - V<sub>F</sub>. If desired, this DESAT threshold voltage can be decreased by using multiple DESAT diodes in series. If n is the number of DESAT diodes then the nominal threshold value becomes  $V_{CE,FAULT(TH)} = 7 V - n \times V_F$ . In the case of using two diodes instead of one, diodes with half of the total required maximum reverse-voltage rating may be chosen.

|             |               |                      | Mary Davidson Valtana                                    |                           |

|-------------|---------------|----------------------|----------------------------------------------------------|---------------------------|

| Part Number | Manufacturer  | t <sub>rr</sub> (ns) | Max. Reverse Voltage<br>Rating, V <sub>RRM</sub> (Volts) | Package Type              |

| MUR1100E    | Motorola      | 75                   | 1000                                                     | 59-04 (axial leaded)      |

| MURS160T3   | Motorola      | 75                   | 600                                                      | Case 403A (surface mount) |

| UF4007      | General Semi. | 75                   | 1000                                                     | DO-204AL (axial leaded)   |

| BYM26E      | Philips       | 75                   | 1000                                                     | SOD64 (axial leaded)      |

| BYV26E      | Philips       | 75                   | 1000                                                     | SOD57 (axial leaded)      |

| BYV99       | Philips       | 75                   | 600                                                      | SOD87 (surface mount)     |

#### **Power/Layout Considerations**

# Operating Within the Maximum Allowable Power Ratings (Adjusting Value of $R_{\mbox{\scriptsize G}}$ ):

When choosing the value of  $R_{\text{G}}$ , it is important to confirm that the power dissipation of the HCPL-316J is within the maximum allowable power rating.

The steps for doing this are:

1. Calculate the minimum desired R<sub>G</sub>;

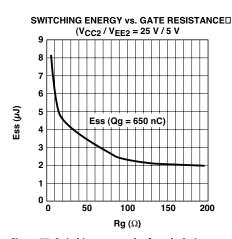

- Calculate total power dissipation in the part referring to Figure 77. (Average switching energy supplied to HCPL-316J per cycle vs. R<sub>G</sub> plot);

- 3. Compare the input and output power dissipation calculated in step #2 to the maximum recommended dissipation for the HCPL-316J. (If the maximum recommended level has been exceeded, it may be necessary to raise the value of R<sub>G</sub> to lower the switching power and repeat step #2.)

As an example, the total input and output power dissipation can be calculated given the following conditions:

- I<sub>ON, MAX</sub> ~ 2.0 A

- V<sub>CC2</sub> = 18 V

- $V_{FF} = -5 V$

- f<sub>CARRIER</sub> = 15 kHz

#### Step 1: Calculate R<sub>G</sub> minimum from I<sub>OL</sub> peak specification:

To find the peak charging  $I_{OL}$  assume that the gate is initially charged the steady-state value of  $V_{EE}$ . Therefore apply the following relationship:

$$R_G = \frac{[V_{OH}@650 \, \mu A - (V_{OL} + V_{EE})]}{I_{OL,PEAK}}$$

$$= \frac{[V_{CC2} - 1 - (V_{OL} + V_{EE})]}{I_{OL,PEAK}}$$

$$= \frac{18 \, V - 1 \, V - (1.5 \, V + (-5 \, V))}{2.0 \, A}$$

$$= 10.25 \, \Omega$$

$$\approx 10.5 \, \Omega \text{ (for a 1% resistor)}$$

(Note from Figure 76 that the real value of  $I_{OL}$  may vary from the value calculated from the simple model shown.)

#### Step 2: Calculate total power dissipation in the HCPL-316J:

The HCPL-316J total power dissipation  $(P_T)$  is equal to the sum of the input-side power  $(P_I)$  and output-side power  $(P_O)$ :

$$\begin{split} P_T &= P_I + P_O \\ P_I &= I_{CC1} * V_{CC1} \\ P_O &= P_{O(BIAS)} + P_{O,SWTICH} \\ &= I_{CC2} * (V_{CC2} - V_{EE}) + E_{SWITCH} * f_{SWITCH} \\ \text{where,} \end{split}$$

Figure 76. Typical peak  $l_{ON}$  and  $l_{OFF}$  currents vs. Rg (for HCPL-316J output driving an IGBT rated at 600 V/100 A.

$P_{O(BIAS)}$  = steady-state power dissipation in the HC-PL-316J due to biasing the device.

$P_{O(SWITCH)}$  = transient power dissipation in the HC-PL-316J due to charging and discharging power device gate.

$E_{SWITCH}$  = Average Energy dissipated in HCPL-316J due to switching of the power device over one switching cycle ( $\mu$ J/cycle).