# DACx3701 10-Bit and 8-Bit, Voltage-Output Smart DACs With Nonvolatile Memory and PMBus<sup>™</sup> Compatible I<sup>2</sup>C Interface With GPI Control

## 1 Features

- 1 LSB INL and DNL (10-bit and 8-bit)

- Wide operating range

- Power supply: 1.8 V to 5.5 V

- Temperature range: -40°C to +125°C

- General-purpose input (GPI) based function trigger

- PMBus<sup>™</sup> compatible I<sup>2</sup>C interface

- Standard, fast, and fast mode plus

- Four device address options configured using the broadcast address

- 1.62-V V<sub>IH</sub> with V<sub>DD</sub> = 5.5 V

- User-programmable nonvolatile memory (NVM/ EEPROM)

- Save and recall all register settings

- Programmable waveform generation: Square, triangular, and sawtooth

- Pulse-width modulation (PWM) output using triangular waveform and FB pin

- Preprogrammed medical-alarm tone-generation mode: low-, medium-, and high-priority alarms

- Digital slew rate control

- Internal reference

- Very low power: 0.2 mA at 1.8 V ٠

- Flexible start-up: High impedance or 10K-GND

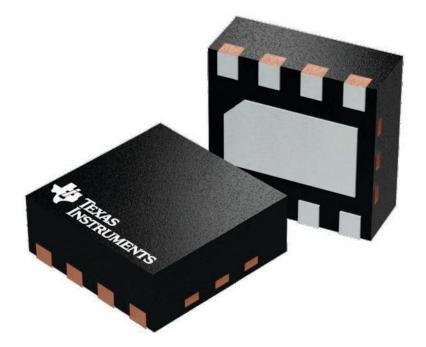

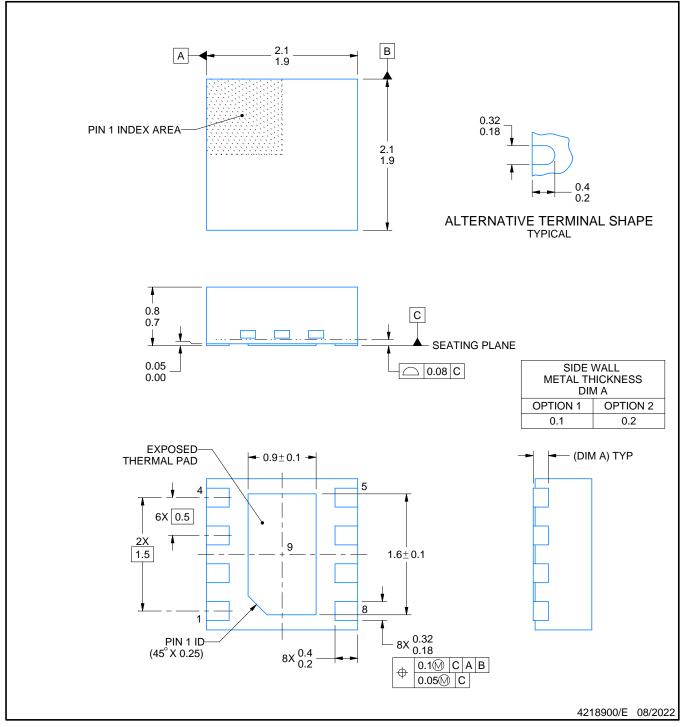

- Tiny package: 8-pin WSON (2 mm × 2 mm) ٠

## 2 Applications

- Oven •

- Ventilators

- Infusion pump

- Anesthesia delivery systems

- Surgical equipment ٠

- Rack server

- Exit and emergency lighting

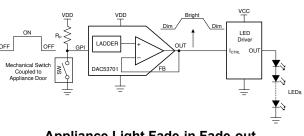

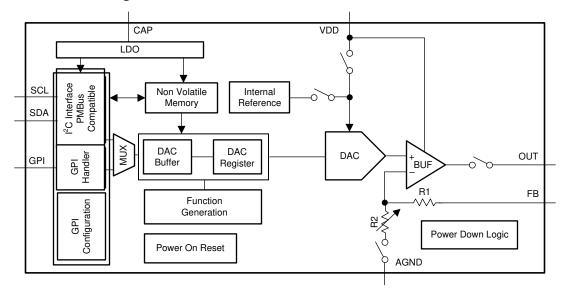

## **Functional Block Diagram**

## **3 Description**

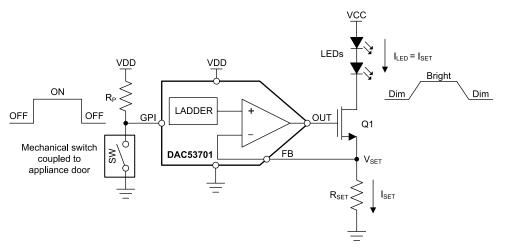

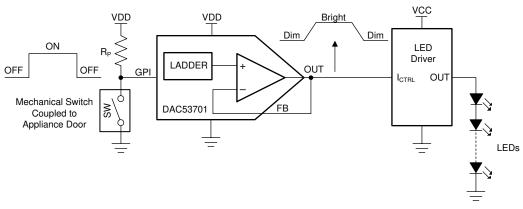

The 10-bit DAC53701 and 8-bit DAC43701 (DACx3701) are a pin-compatible family of buffered voltage-output smart digital-to-analog converters (DACs). These devices consume very low power, and are available in a tiny 8-pin WSON package. The feature set combined with the tiny package and low power make the DACx3701 an excellent choice for applications such as appliance door fade-in fade-out, processorless LED dimming with PWM input, generalpurpose bias point generation, voltage margining and scaling, PWM signal generation, and medical alarm tone generation.

These devices have nonvolatile memory (NVM), an internal reference, a PMBus-compatible I<sup>2</sup>C interface, and a general-purpose input. The DACx3701 operates with either an internal reference or with the power supply as a reference, and provides a full-scale output of 1.8 V to 5.5 V.

The DACx3701 are smart DAC devices because of their advanced integrated features. With force-sense output, GPI based function trigger, medical alarm, PWM output, and NVM capabilities, smart DACs enable system performance and control without the use of software.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |  |  |

|-------------|------------------------|-------------------|--|--|

| DAC53701    | WSON (8)               | 2.00 mm × 2.00 mm |  |  |

| DAC43701    | W30N (8)               |                   |  |  |

For all available packages, see the package option (1)addendum at the end of the data sheet.

Appliance Light Fade-in Fade-out

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, 🚳 intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 Features1                                                        |

|--------------------------------------------------------------------|

| 2 Applications1                                                    |

| 3 Description1                                                     |

| 4 Revision History2                                                |

| 5 Device Comparison Table                                          |

| 6 Pin Configuration and Functions                                  |

| 7 Specifications                                                   |

| 7.1 Absolute Maximum Ratings4                                      |

| 7.2 ESD Ratings 4                                                  |

| 7.3 Recommended Operating Conditions4                              |

| 7.4 Thermal Information4                                           |

| 7.5 Electrical Characteristics5                                    |

| 7.6 Timing Requirements: I <sup>2</sup> C Standard Mode7           |

| 7.7 Timing Requirements: I <sup>2</sup> C Fast Mode7               |

| 7.8 Timing Requirements: I <sup>2</sup> C Fast Mode Plus8          |

| 7.9 Timing Requirements: GPI8                                      |

| 7.10 Timing Diagram8                                               |

| 7.11 Typical Characteristics: V <sub>DD</sub> = 5.5 V (Reference   |

| = V <sub>DD</sub> ) or V <sub>DD</sub> = 5 V (Internal Reference)9 |

| 7.12 Typical Characteristics: V <sub>DD</sub> = 1.8 V (Reference   |

| = V <sub>DD</sub> ) or V <sub>DD</sub> = 2 V (Internal Reference)  |

| 7.13 Typical Characteristics13                                     |

| 8 Detailed Description18                                           |

| 8.1 Overview                                          | .18 |

|-------------------------------------------------------|-----|

| 8.2 Functional Block Diagram                          | .18 |

| 8.3 Feature Description                               | .19 |

| 8.4 Device Functional Modes                           |     |

| 8.5 Programming                                       | 29  |

| 8.6 Register Map                                      |     |

| 9 Application and Implementation                      |     |

| 9.1 Application Information                           |     |

| 9.2 Typical Applications                              |     |

| 10 Power Supply Recommendations                       |     |

| 11 Layout                                             |     |

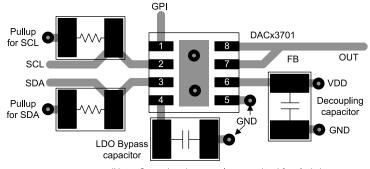

| 11.1 Layout Guidelines                                |     |

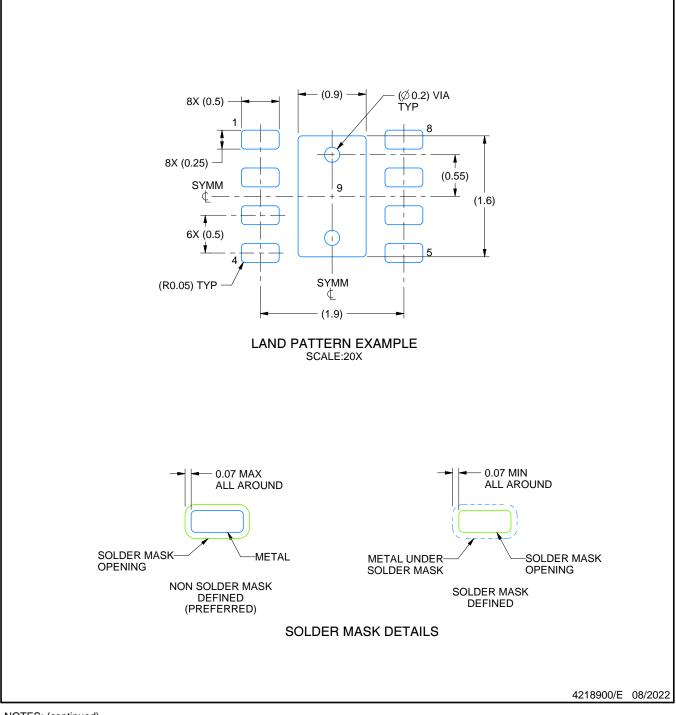

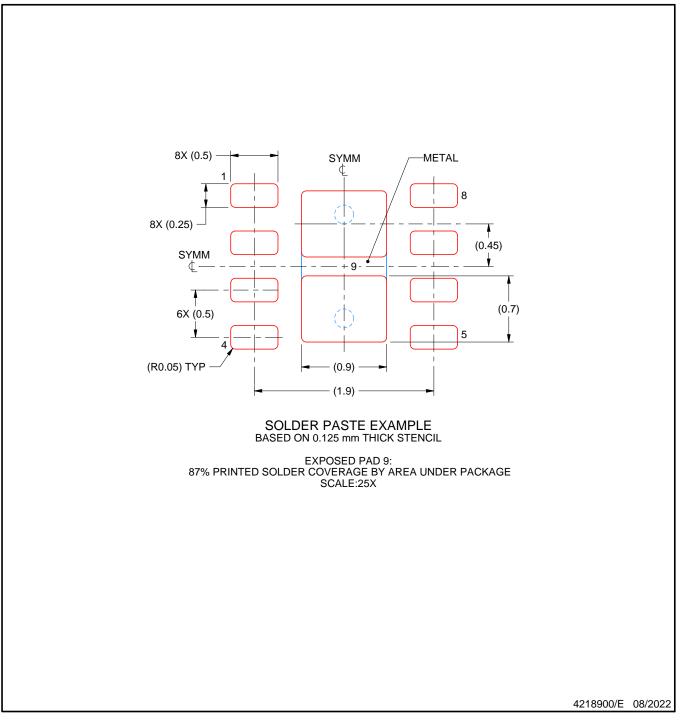

| 11.2 Layout Example                                   | 49  |

| 12 Device and Documentation Support                   |     |

| 12.1 Documentation Support                            |     |

| 12.2 Receiving Notification of Documentation Updates. | .50 |

| 12.3 Support Resources                                |     |

| 12.4 Trademarks                                       |     |

| 12.5 Electrostatic Discharge Caution                  | .50 |

| 12.6 Glossary                                         |     |

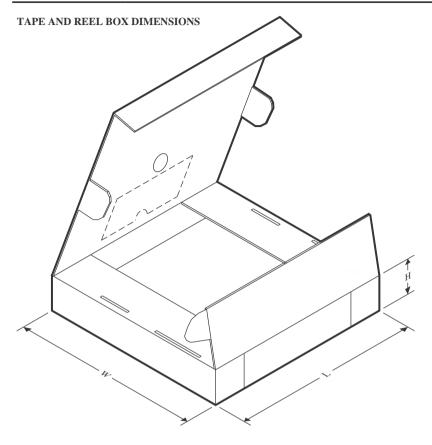

| 13 Mechanical, Packaging, and Orderable               |     |

| Information                                           | 50  |

|                                                       |     |

# **4 Revision History**

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2020 | *        | Initial release. |

## **5** Device Comparison Table

| DEVICE   | RESOLUTION |

|----------|------------|

| DAC53701 | 10-bit     |

| DAC43701 | 8-bit      |

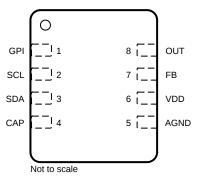

## **6** Pin Configuration and Functions

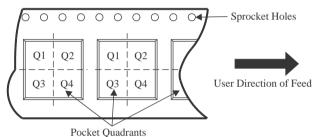

## Figure 6-1. DSG Package, 8-Pin WSON, Top View

#### Table 6-1. Pin Functions

| P    | IN  | TYPE         | DESCRIPTION                                                                                                                                                    |

|------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. |              | DESCRIPTION                                                                                                                                                    |

| AGND | 5   | Ground       | Ground reference point for all circuitry on the device                                                                                                         |

| САР  | 4   | Input        | External capacitor for the internal LDO. Connect a capacitor (approximately 1.5 $\mu F)$ between CAP and AGND.                                                 |

| FB   | 7   | Input        | Voltage-feedback pin                                                                                                                                           |

| GPI  | 1   | Input        | General-purpose input                                                                                                                                          |

| OUT  | 8   | Output       | Analog output voltage from DAC                                                                                                                                 |

| SCL  | 2   | Input        | Serial interface clock. This pin must be connected to the supply voltage with an external pullup resistor.                                                     |

| SDA  | 3   | Input/output | Data are clocked into or out of the input register. This pin is a bidirectional, and must be connected to the supply voltage with an external pullup resistor. |

| VDD  | 6   | Power        | Analog supply voltage: 1.8 V to 5.5 V                                                                                                                          |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                            |   | MIN  | MAX                   | UNIT |

|------------------|------------------------------------------------------------|---|------|-----------------------|------|

| V <sub>DD</sub>  | Supply voltage, V <sub>DD</sub> to A <sub>GND</sub>        | - | -0.3 | 6                     | V    |

|                  | Digital input(s) to A <sub>GND</sub>                       | - | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                  | CAP to A <sub>GND</sub>                                    | - | -0.3 | 1.65                  | V    |

|                  | V <sub>FB</sub> to A <sub>GND</sub>                        | - | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                  | V <sub>OUT</sub> to A <sub>GND</sub>                       | - | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                  | Current into any pin except the power pins and the OUT pin |   | -10  | 10                    | mA   |

| TJ               | Junction temperature                                       |   | -40  | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature                                        |   | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                             |                                 | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------|---------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC | JS-001, all pins <sup>(1)</sup> | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC       | pins 1, 4, 5, 8 <sup>(2)</sup>  | ±750  | V    |

|                    |                         | specification JESD22-C101                   | pins 2, 3, 6, 7 <sup>(2)</sup>  | ±500  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                                        | MIN  | NOM | MAX | UNIT |

|-----------------|--------------------------------------------------------|------|-----|-----|------|

| V <sub>DD</sub> | Positive supply voltage to ground (A <sub>GND</sub> )  | 1.71 |     | 5.5 | V    |

| V <sub>IH</sub> | Digital input high voltage, 1.7 V < $V_{DD} \le 5.5$ V | 1.62 |     |     | V    |

| VIL             | Digital input low voltage                              |      |     | 0.4 | V    |

| T <sub>A</sub>  | Ambient temperature                                    | -40  |     | 125 | °C   |

#### 7.4 Thermal Information

|                       |                                                                                                                                                                              | DACx3701   |      |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|

|                       | C(top)Junction-to-case (top) thermal resistanceBJunction-to-board thermal resistanceTJunction-to-top characterization parameterBJunction-to-board characterization parameter | DSG (WSON) | UNIT |

|                       |                                                                                                                                                                              | 8 PINS     |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance                                                                                                                                       | 49         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                                                                                                                                    | 50         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance                                                                                                                                         | 24.1       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter                                                                                                                                   | 1.1        | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter                                                                                                                                 | 24.1       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                                                                                                                                 | 8.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

all minimum/maximum specifications at  $T_A = -40^{\circ}$ C to +125°C and typical specifications at  $T_A = 25^{\circ}$ C, 1.8 V  $\leq V_{DD} \leq 5.5$  V, DAC reference tied to VDD, gain = 1x, DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|      | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                | MIN  | TYP     | MAX | UNIT    |

|------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----|---------|

| STAT | IC PERFORMANCE                                        |                                                                                                                                                                                |      |         |     |         |

|      | Resolution                                            | DAC53701                                                                                                                                                                       | 10   |         |     | Pito    |

|      | Resolution                                            | DAC43701                                                                                                                                                                       | 8    |         |     | Bits    |

| NL   | Relative accuracy <sup>(1)</sup>                      |                                                                                                                                                                                | -1   |         | 1   | LSB     |

| DNL  | Differential nonlinearity <sup>(1)</sup>              |                                                                                                                                                                                | -1   |         | 1   | LSB     |

|      |                                                       | Code 0d into DAC, external reference, $V_{DD}$ = 5.5 V                                                                                                                         |      | 6       | 12  |         |

|      | Zero-code error                                       | Code 0d into DAC, internal reference, gain = 4x, $V_{DD}$ = 5.5 V                                                                                                              |      | 6       | 15  | mV      |

|      | Zero-code-error temperature coefficient               |                                                                                                                                                                                |      | ±10     |     | µV/°C   |

|      | Offset error <sup>(4)</sup>                           |                                                                                                                                                                                | -0.5 | 0.25    | 0.5 | %FSR    |

|      | Offset-error temperature coefficient <sup>(4)</sup>   |                                                                                                                                                                                |      | ±0.0003 |     | %FSR/°C |

|      | Gain error <sup>(4)</sup>                             |                                                                                                                                                                                | -0.5 | 0.25    | 0.5 | %FSR    |

|      | Gain-error temperature coefficient <sup>(4)</sup>     |                                                                                                                                                                                |      | ±0.0008 |     | %FSR/°C |

|      | Full-scale error                                      | $1.8 \ V \leq V_{DD} \prec 2.7 \ V, \ code \ 1023 d \ into \ DAC \ for \ 10-bit resolution, \ code \ 255 d \ into \ DAC \ for \ 8-bit \ resolution, \ no headroom$             | –1   | 0.5     | 1   | %FSR    |

|      |                                                       | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ , code 1023d into DAC for 10-bit resolution, code 255d into DAC for 8-bit resolution, no headroom                   | -0.5 | 0.25    | 0.5 | /01 51  |

|      | Full-scale-error temperature coefficient              |                                                                                                                                                                                |      | ±0.0008 |     | %FSR/°C |

| ουτι | PUT CHARACTERISTICS                                   |                                                                                                                                                                                |      |         |     |         |

|      | Output voltage                                        | Reference tied to V <sub>DD</sub>                                                                                                                                              | 0    |         | 5.5 | V       |

| CL   | Capacitive load <sup>(2)</sup>                        | R <sub>L</sub> = Infinite, phase margin = 30°                                                                                                                                  |      |         | 1   | nF      |

|      |                                                       | $R_L = 5 k\Omega$ , phase margin = 30°                                                                                                                                         |      |         | 2   |         |

|      | Load regulation                                       | DAC at midscale, –10 mA $\leq$ I <sub>OUT</sub> $\leq$ 10 mA, V <sub>DD</sub> = 5.5 V                                                                                          |      | 0.4     |     | mV/mA   |

|      |                                                       | $V_{DD}$ = 1.8 V, full-scale output shorted to $A_{GND}$ or zero-scale output shorted to $V_{DD}$                                                                              |      | 10      |     |         |

|      | Short circuit current                                 | $V_{DD}$ = 2.7 V, full-scale output shorted to $A_{GND}$ or zero-scale output shorted to $V_{DD}$                                                                              |      | 25      |     | mA      |

|      |                                                       | $V_{DD}$ = 5.5 V, full-scale output shorted to $A_{GND}$ or zero-scale output shorted to $V_{DD}$                                                                              |      | 50      |     |         |

|      |                                                       | To $V_{DD}$ (DAC output unloaded, internal reference = 1.21 V), $V_{DD} \ge 1.21 \times \text{gain} + 0.2 \text{ V}$                                                           | 0.2  |         |     | V       |

|      | Output voltage headroom <sup>(1)</sup> <sup>(2)</sup> | To $V_{DD}$ (DAC output unloaded, reference tied to $V_{DD}$ )                                                                                                                 | 0.8  |         |     |         |

|      |                                                       | To $V_{DD}$ (I <sub>LOAD</sub> = 10 mA at $V_{DD}$ = 5.5 V, I <sub>LOAD</sub> = 3 mA at $V_{DD}$ = 2.7 V, I <sub>LOAD</sub> = 1 mA at $V_{DD}$ = 1.8 V), DAC code = full scale | 10   |         |     | %FSR    |

|      |                                                       | DAC output enabled and DAC code = midscale                                                                                                                                     |      | 0.25    |     |         |

|      | V <sub>OUT</sub> dc output impedance                  | DAC output enabled and DAC code = 8d for 10-bit resolution and code = 2d for 8-bit resolution                                                                                  |      | 0.25    |     | Ω       |

|      |                                                       | DAC output enabled and DAC code = 1016d for 10-bit resolution and code = 254d for 8-bit resolution                                                                             |      | 0.26    |     |         |

## 7.5 Electrical Characteristics (continued)

all minimum/maximum specifications at  $T_A = -40^{\circ}$ C to +125°C and typical specifications at  $T_A = 25^{\circ}$ C, 1.8 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, DAC reference tied to VDD, gain = 1x, DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|                | PARAMETER                                                              | TEST CONDITIONS                                                                                                       | MIN | TYP   | MAX | UNIT             |

|----------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------------------|

| Zo             | V <sub>FB</sub> dc output impedance <sup>(3)</sup>                     | DAC output enabled, DAC reference tied to VDD (gain = $1x$ ) or internal reference (gain = $1.5x$ or $2x$ )           | 160 | 200   | 240 | kΩ               |

|                |                                                                        | DAC output enabled, internal $V_{REF}$ , gain = 3x or 4x                                                              | 192 | 240   | 288 |                  |

|                | V <sub>OUT</sub> + V <sub>FB</sub> dc output<br>leakage <sup>(2)</sup> | At start up, measured when DAC output is disabled and held at $V_{DD}$ / 2 for $V_{DD}$ = 5.5 V                       |     |       | 7   | nA               |

|                | Power supply rejection ratio (dc)                                      | Internal V <sub>REF</sub> , gain = 2x, DAC at midscale;<br>V <sub>DD</sub> = 5 V $\pm$ 10%                            |     | 0.25  |     | mV/V             |

| DYN            | AMIC PERFORMANCE                                                       | · · · · ·                                                                                                             |     |       |     |                  |

|                |                                                                        | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 10%FSR, $V_{\text{DD}}$ = 5.5 V                                     |     | 8     |     |                  |

| sett           | Output voltage settling time                                           | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 10%FSR, $V_{DD}$ = 5.5 V, internal $V_{REF}$ , gain = 4x            |     | 12    |     | μs               |

|                | Slew rate                                                              | V <sub>DD</sub> = 5.5 V                                                                                               |     | 1     |     | V/µs             |

|                | Power-on glitch magnitude                                              | At startup (DAC output disabled), R <sub>L</sub> = 5 k $\Omega$ , C <sub>L</sub> = 200 pF                             |     | 75    |     | mV               |

|                |                                                                        | At startup (DAC output disabled), $R_L = 100 \text{ k}\Omega$                                                         |     | 200   |     |                  |

|                | Output enable glitch magnitude                                         | DAC output disabled to enabled (DAC registers at zero scale, $R_L$ = 100 $k\Omega$                                    |     | 250   |     | mV               |

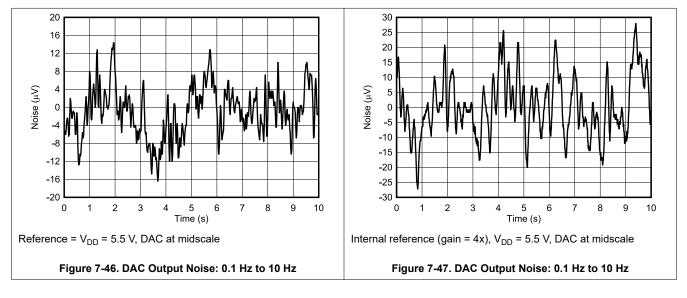

|                |                                                                        | 0.1 Hz to 10 Hz, DAC at midscale, $V_{DD}$ = 5.5 V                                                                    |     | 34    |     |                  |

| / <sub>n</sub> | Output noise voltage (peak to peak)                                    | Internal V <sub>REF</sub> , gain = 4x, 0.1 Hz to 10 Hz, DAC at midscale, V <sub>DD</sub> = 5.5 V                      |     | 70    |     | μV <sub>PP</sub> |

|                |                                                                        | Measured at 1 kHz, DAC at midscale, $V_{DD}$ = 5.5 V                                                                  |     | 0.2   |     |                  |

|                | Output noise density                                                   | Internal V <sub>REF,</sub> gain = 4x, measured at 1 kHz, DAC at midscale, V <sub>DD</sub> = 5.5 V                     |     | 0.7   |     | µV/√Hz           |

|                | Power supply rejection ratio (ac) <sup>(3)</sup>                       | Internal $V_{REF}$ , gain = 4x, 200-mV 50-Hz or 60-Hz sine wave superimposed on power supply voltage, DAC at midscale |     | -71   |     | dB               |

|                | Code change glitch impulse                                             | ±1 LSB change around mid code (including feedthrough)                                                                 |     | 10    |     | nV-s             |

|                | Code change glitch impulse magnitude                                   | ±1 LSB change around mid code (including feedthrough)                                                                 |     | 15    |     | mV               |

| /0Ľ            | TAGE REFERENCE                                                         | · · · · ·                                                                                                             |     |       |     |                  |

|                | Initial accuracy                                                       | T <sub>A</sub> = 25°C                                                                                                 |     | 1.212 |     | V                |

|                | Reference output temperature coefficient <sup>(2)</sup>                |                                                                                                                       |     |       | 65  | ppm/°C           |

| EEP            | ROM                                                                    |                                                                                                                       |     |       |     |                  |

|                | Endurance <sup>(2)</sup>                                               | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                                             |     | 20000 |     | Cycles           |

|                |                                                                        | T <sub>A</sub> > 85°C                                                                                                 |     | 1000  |     | Cycles           |

|                | Data retention <sup>(2)</sup>                                          | T <sub>A</sub> = 25°C                                                                                                 |     | 50    |     | Years            |

|                |                                                                        | T <sub>A</sub> = 125°C                                                                                                |     | 20    |     | 10013            |

|                | EEPROM programming write cycle time <sup>(2)</sup>                     |                                                                                                                       | 10  |       | 20  | ms               |

| DIGI           | TAL INPUTS                                                             |                                                                                                                       |     |       |     |                  |

|                | Digital feedthrough                                                    | DAC output static at midscale, fast mode plus, SCL toggling                                                           |     | 20    |     | nV-s             |

|                | Pin capacitance                                                        | Per pin                                                                                                               |     | 10    |     | pF               |

## 7.5 Electrical Characteristics (continued)

all minimum/maximum specifications at  $T_A = -40^{\circ}$ C to +125°C and typical specifications at  $T_A = 25^{\circ}$ C, 1.8 V  $\leq V_{DD} \leq 5.5$  V, DAC reference tied to VDD, gain = 1x, DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|                                          | PARAMETER                               | TEST CONDITIONS                                      | MIN | TYP   | MAX  | UNIT |

|------------------------------------------|-----------------------------------------|------------------------------------------------------|-----|-------|------|------|

| POW                                      | ER                                      |                                                      |     |       |      |      |

|                                          | Load capacitor - CAP pin <sup>(2)</sup> |                                                      | 0.5 |       | 15   | μF   |

|                                          | Current flowing into V/DD               | Normal mode, DACs at full scale, digital pins static |     | 0.225 | 0.55 | mA   |

| I <sub>DD</sub> Current flowing into VDD |                                         | DAC power-down, internal reference power down        |     | 80    |      | μA   |

(1) Measured with DAC output unloaded. For external reference between end-point codes: 8d to 1016d for 10-bit resolution, 2d to 254d for 8-bit resolution. For internal reference V<sub>DD</sub> ≥ 1.21 x gain + 0.2 V, between end-point codes: 8d to 1016d for 10-bit resolution, 2d to 254d for 8-bit resolution.

(2) Specified by design and characterization, not production tested.

(3) Specified with 200-mV headroom with respect to reference value when internal reference is used.

(4) Measured with DAC output unloaded. For 10-bit resolution, between end-point codes: 8d to 1016d and for 8-bit resolution, between end-point codes: 2d to 254d.

## 7.6 Timing Requirements: I<sup>2</sup>C Standard Mode

all input signals are timed from VIL to 70% of  $V_{DD}$ , 1.8 V  $\leq V_{DD} \leq 5.5$  V,  $-40^{\circ}C \leq T_A \leq +125^{\circ}C$ , and 1.8 V  $\leq V_{pull-up} \leq V_{DD}$  V

|                    |                                                 | MIN  | NOM MAX | UNIT |

|--------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>  | SCL frequency                                   |      | 0.1     | MHz  |

| t <sub>BUF</sub>   | Bus free time between stop and start conditions | 4.7  |         | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated start                  | 4    |         | μs   |

| t <sub>SUSTA</sub> | Repeated start setup time                       | 4.7  |         | μs   |

| t <sub>susto</sub> | Stop condition setup time                       | 4    |         | μs   |

| t <sub>HDDAT</sub> | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub> | Data setup time                                 | 250  |         | ns   |

| t <sub>LOW</sub>   | SCL clock low period                            | 4700 |         | ns   |

| t <sub>HIGH</sub>  | SCL clock high period                           | 4000 |         | ns   |

| t <sub>F</sub>     | Clock and data fall time                        |      | 300     | ns   |

| t <sub>R</sub>     | Clock and data rise time                        |      | 1000    | ns   |

#### 7.7 Timing Requirements: I<sup>2</sup>C Fast Mode

all input signals are timed from VIL to 70% of V<sub>DD</sub>, 1.8 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C, and 1.8 V  $\leq$  V<sub>pull-up</sub>  $\leq$  V<sub>DD</sub> V

|                    | 0 80 9                                          | <i>,</i> ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | pun up  |      |

|--------------------|-------------------------------------------------|----------------------------------------------|---------|------|

|                    |                                                 | MIN                                          | NOM MAX | UNIT |

| f <sub>SCLK</sub>  | SCL frequency                                   |                                              | 0.4     | MHz  |

| t <sub>BUF</sub>   | Bus free time between stop and start conditions | 1.3                                          |         | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated start                  | 0.6                                          |         | μs   |

| t <sub>SUSTA</sub> | Repeated start setup time                       | 0.6                                          |         | μs   |

| t <sub>SUSTO</sub> | Stop condition setup time                       | 0.6                                          |         | μs   |

| t <sub>HDDAT</sub> | Data hold time                                  | 0                                            |         | ns   |

| t <sub>SUDAT</sub> | Data setup time                                 | 100                                          |         | ns   |

| t <sub>LOW</sub>   | SCL clock low period                            | 1300                                         |         | ns   |

| t <sub>HIGH</sub>  | SCL clock high period                           | 600                                          |         | ns   |

| t <sub>F</sub>     | Clock and data fall time                        |                                              | 300     | ns   |

| t <sub>R</sub>     | Clock and data rise time                        |                                              | 300     | ns   |

|                    |                                                 |                                              |         |      |

## 7.8 Timing Requirements: I<sup>2</sup>C Fast Mode Plus

all input signals are timed from VIL to 70% of V<sub>DD</sub>, 1.8 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C, and 1.8 V  $\leq$  V<sub>pull-up</sub>  $\leq$  V<sub>DD</sub> V

|                    |                                                 | MIN  | NOM MAX | UNIT |

|--------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>  | SCL frequency                                   |      | 1       | MHz  |

| t <sub>BUF</sub>   | Bus free time between stop and start conditions | 0.5  |         | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated start                  | 0.26 |         | μs   |

| t <sub>SUSTA</sub> | Repeated start setup time                       | 0.26 |         | μs   |

| t <sub>SUSTO</sub> | Stop condition setup time                       | 0.26 |         | μs   |

| t <sub>HDDAT</sub> | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub> | Data setup time                                 | 50   |         | ns   |

| t <sub>LOW</sub>   | SCL clock low period                            | 0.5  |         | μs   |

| t <sub>HIGH</sub>  | SCL clock high period                           | 0.26 |         | μs   |

| t <sub>F</sub>     | Clock and data fall time                        |      | 120     | ns   |

| t <sub>R</sub>     | Clock and data rise time                        |      | 120     | ns   |

## 7.9 Timing Requirements: GPI

all input signals are timed from VIL to 70% of  $V_{DD}$ .  $V_{DD}$  = 1.8 V to 5.5 V and  $T_A$  = -40°C to +125°C (unless otherwise noted)

|                       |                                                                                                | MIN | NOM | MAX | UNIT |

|-----------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>GPIDELAY</sub> | GPI edge to start of operation delay, 1.7 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V <sup>(1)</sup> |     | 2   |     | μs   |

(1) The value specified for t<sub>GPIDELAY</sub> in the timing table is in addition to 2x SLEW\_RATE for margin-high, low and function generation operations. The typical value for the total delay is (2xSLEW\_RATE + t<sub>GPIDELAY</sub>).

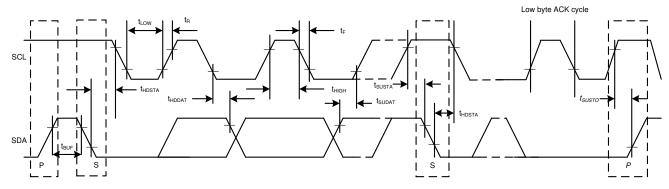

## 7.10 Timing Diagram

Figure 7-1. I<sup>2</sup>C Timing Diagram

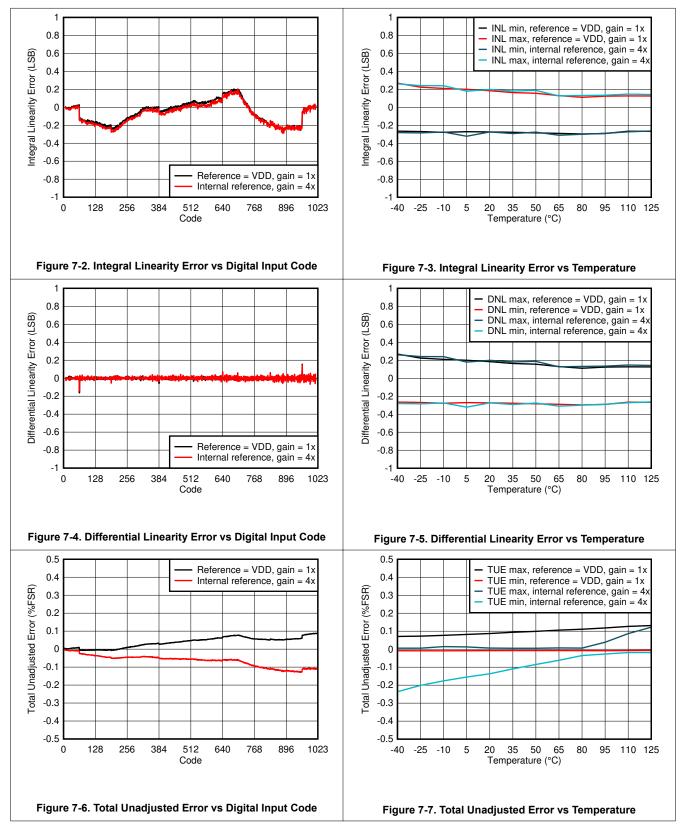

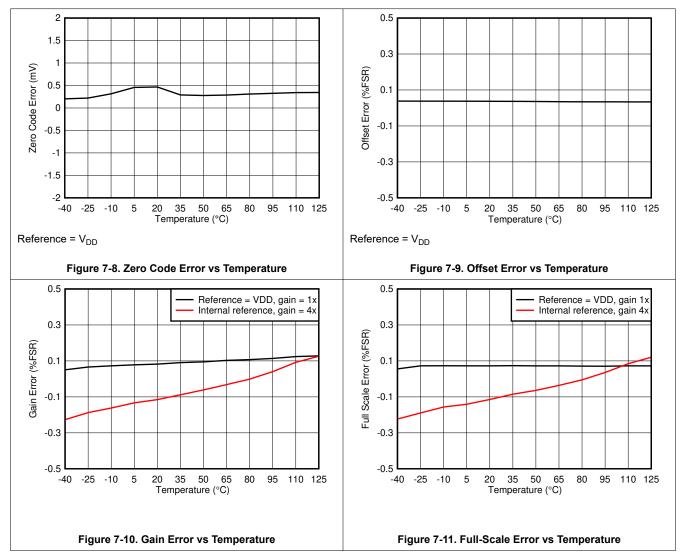

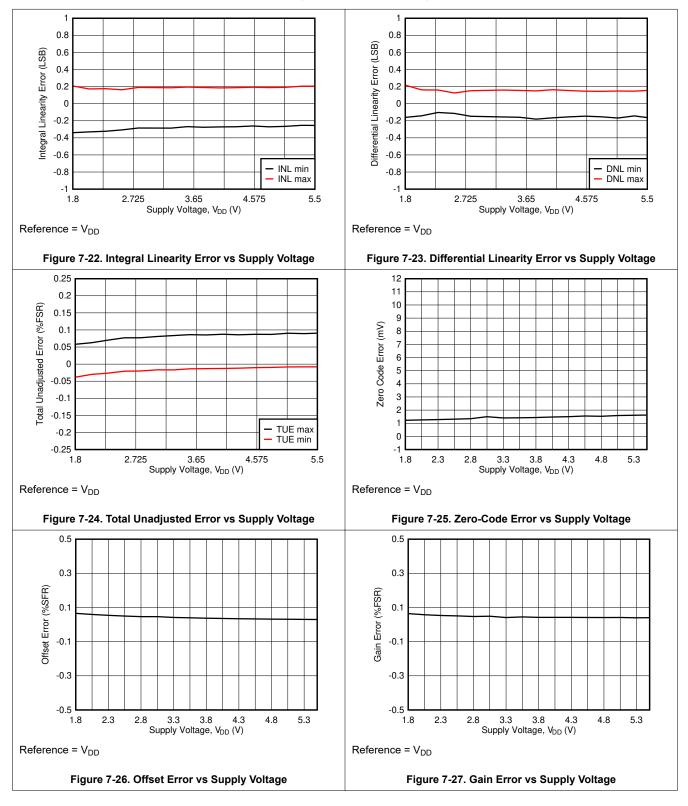

# 7.11 Typical Characteristics: $V_{DD}$ = 5.5 V (Reference = $V_{DD}$ ) or $V_{DD}$ = 5 V (Internal Reference)

at  $T_A = 25^{\circ}$ C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

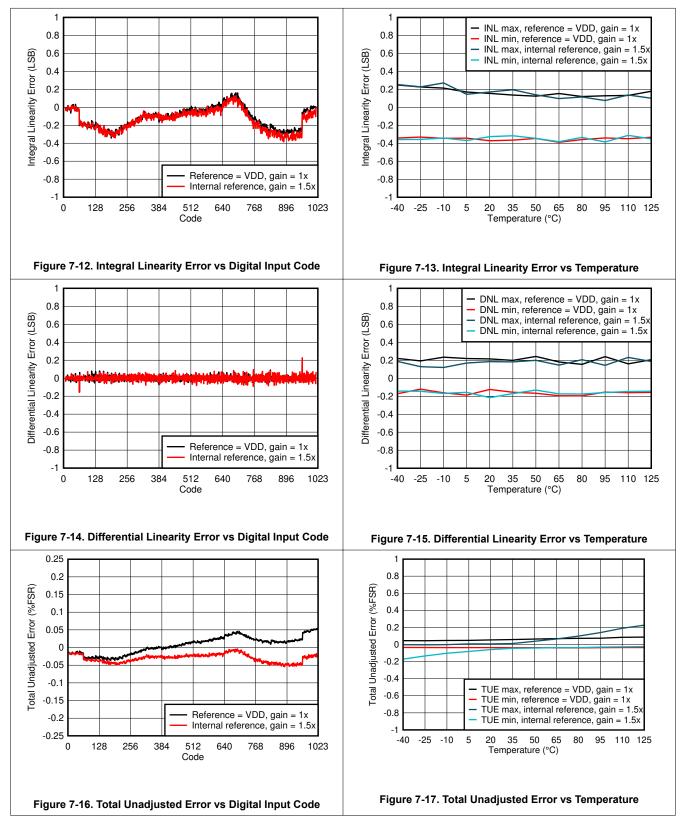

# 7.11 Typical Characteristics: $V_{DD}$ = 5.5 V (Reference = $V_{DD}$ ) or $V_{DD}$ = 5 V (Internal Reference) (continued)

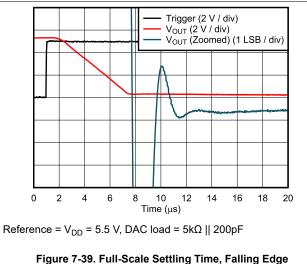

at T<sub>A</sub> = 25°C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

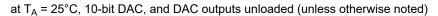

# 7.12 Typical Characteristics: $V_{DD}$ = 1.8 V (Reference = $V_{DD}$ ) or $V_{DD}$ = 2 V (Internal Reference)

at  $T_A = 25^{\circ}$ C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

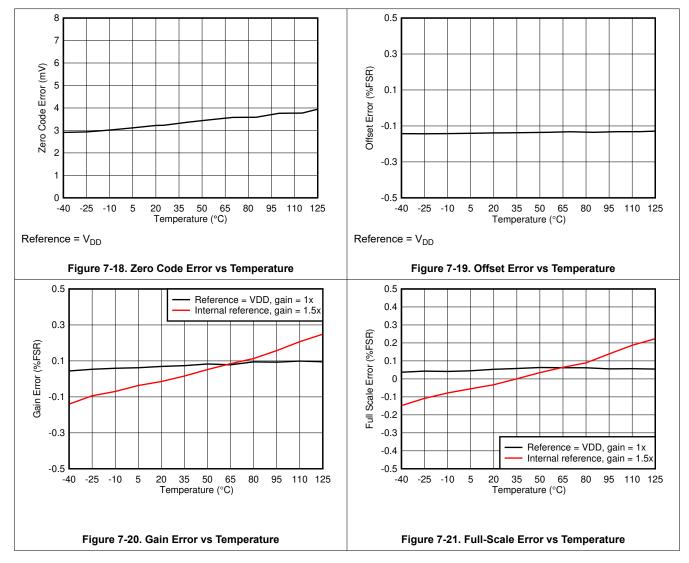

# 7.12 Typical Characteristics: $V_{DD}$ = 1.8 V (Reference = $V_{DD}$ ) or $V_{DD}$ = 2 V (Internal Reference) (continued)

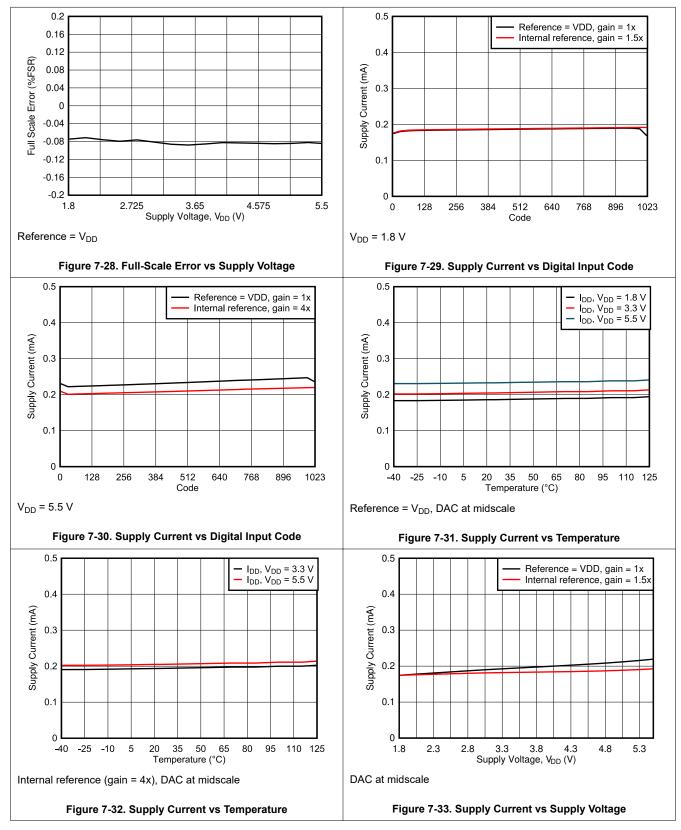

## 7.13 Typical Characteristics

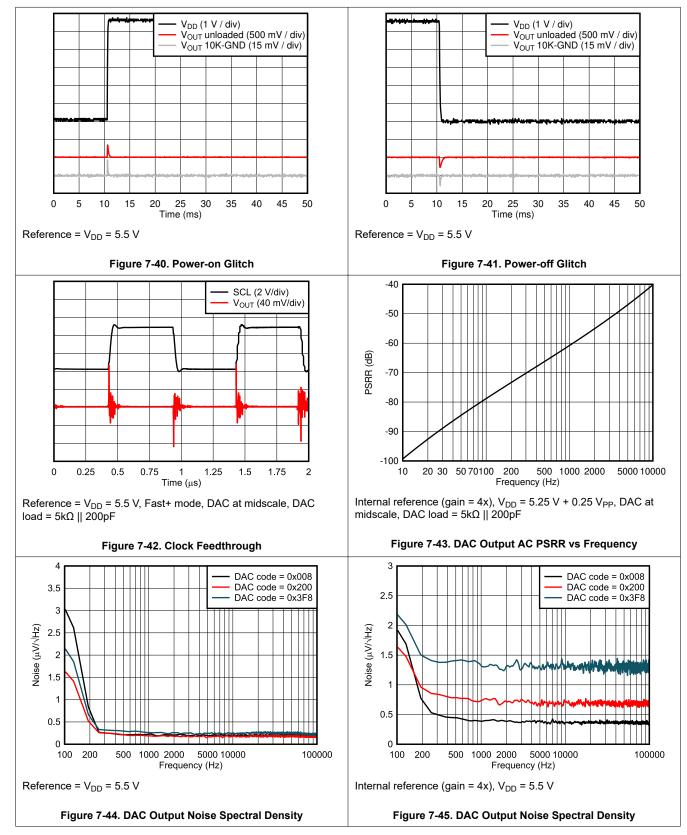

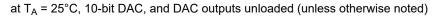

at T<sub>A</sub> = 25°C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

DAC53701, DAC43701 SLASEY5 – DECEMBER 2020

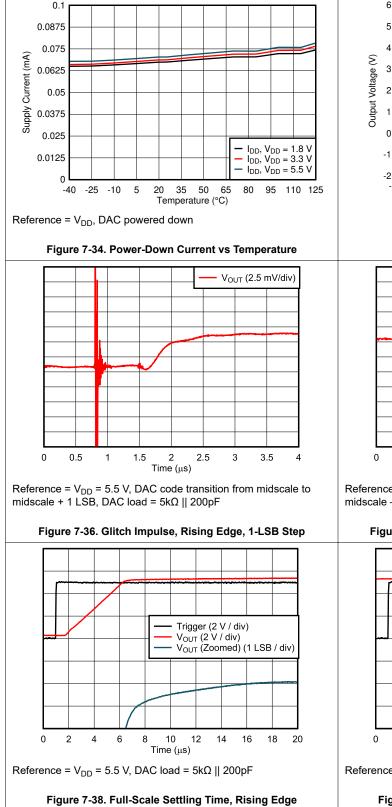

## 7.13 Typical Characteristics (continued)

at  $T_A$  = 25°C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

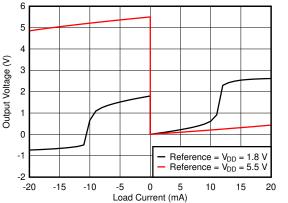

# 7.13 Typical Characteristics (continued)

at T<sub>A</sub> = 25°C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

Figure 7-35. Source and Sink Capability

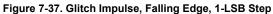

Reference =  $V_{DD}$  = 5.5 V, DAC code transition from midscale to midscale – 1 LSB, DAC load = 5k $\Omega$  || 200pF

DAC53701, DAC43701 SLASEY5 – DECEMBER 2020

# 7.13 Typical Characteristics (continued)

at  $T_A$  = 25°C, 10-bit DAC, and DAC outputs unloaded (unless otherwise noted)

## 7.13 Typical Characteristics (continued)

17

## 8 Detailed Description

## 8.1 Overview

The 10-bit DAC53701 and 8-bit DAC43701 (DACx3701) are a pin-compatible family of buffered voltage-output, smart digital-to-analog converters (DACs). These smart DACs contain nonvolatile memory (NVM), an internal reference, a PMBus-compatible  $I^2C$  interface, force-sense output, and a general-purpose input. The DACx3701 operate with either an internal reference or with a power supply as the reference, and provide a full-scale output of 1.8 V to 5.5 V.

These devices communicate through an I<sup>2</sup>C interface, and support I<sup>2</sup>C standard mode (100 kbps), fast mode (400 kbps), and fast mode plus (1 Mbps). These devices also support specific PMBus commands such as *turn on/off, margin high or low*, and more. The GPI input can be configured as a power-down trigger, margin-high-low, function trigger, and medical alarm trigger. The DACx3701 also include digital slew rate control, and support basic signal generation such as *square, ramp*, and *sawtooth* waveforms. These devices can generate pulsewidth modulation (PWM) output with the combination of the triangular or sawtooth waveform and the FB pin. These features enable the DACx3701 to go beyond the limitations of a conventional DAC that depends on a processor to function. Because of processor-less operation and the *smart* feature set, the DACx3701 are called smart DACs.

The DACx3701 have a power-on-reset (POR) circuit that makes sure all the registers start with default or userprogrammed settings using NVM. The DAC output powers on in high-impedance mode (default); this setting can be programmed to  $10k\Omega$ -GND using NVM.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Digital-to-Analog Converter (DAC) Architecture

The DACx3701 family of devices consists of string architecture with an output buffer amplifier. Section 8.2 shows the DAC architecture within the block diagram. This DAC architecture operates from a 1.8-V to 5.5-V power supply. These devices consume only 0.2 mA of current when using a 1.8-V power supply. The DAC output pin starts up in high-impedance mode, making these devices an excellent choice for power-supply control applications. To change the power-up mode to  $10k\Omega$ -GND, program the DAC\_PDN bit (address: D1h), and load these bits in the device NVM. The DACx3701 devices include a *smart* feature set to enable processor-less operation and high-integration. The NVM enables a predictable startup. The GPI triggers the DAC output without the I<sup>2</sup>C interface in the absence of a processor or when the processor or software fails. The integrated functions and the FB pin enable PWM output for control applications. The FB pin enables this device to be used as a programmable comparator. The digital slew rate control and the Hi-Z power-down modes enable a hassle-free voltage margining and function.

#### 8.3.1.1 Reference Selection and DAC Transfer Function

The device writes the input data to the DAC data registers in straight-binary format. After a power-on or a reset event, the device sets all DAC registers to the values set in the NVM.

#### 8.3.1.1.1 Power Supply as Reference

By default, the DACx3701 operate with the power-supply pin (VDD) as a reference. Equation 1 shows DAC transfer function when the power-supply pin is used as reference. The gain at the output stage is always 1x.

$$V_{OUT} = \frac{DAC\_DATA}{2^N} \times V_{DD}$$

where:

- N is the resolution in bits, either 8 (DAC43701) or 10 (DAC53701).

- DAC\_DATA is the decimal equivalent of the binary code that is loaded to the DAC register.

- DAC\_DATA ranges from 0 to 2<sup>N</sup> 1.

- V<sub>DD</sub> is used as the DAC reference voltage.

#### 8.3.1.1.2 Internal Reference

The DACx3701 also contain an internal reference that is disabled by default. Enable the internal reference by writing 1 to REF\_EN (address D1h). The internal reference generates a fixed 1.21-V voltage (typical). Using DAC\_SPAN (address D1h) bits, gain of 1.5x, 2x, 3x, 4x can be achieved for the DAC output voltage ( $V_{OUT}$ ) Equation 2 shows DAC transfer function when the internal reference is used.

$$V_{OUT} = \frac{DAC\_DATA}{2^N} \times V_{REF} \times GAIN$$

(2)

(1)

where:

- N is the resolution in bits, either 8 (DAC43701) or 10 (DAC53701).

- DAC\_DATA is the decimal equivalent of the binary code that is loaded to the DAC register

- DAC DATA ranges from 0 to 2<sup>N</sup> 1.

- V<sub>REF</sub> is the internal reference voltage = 1.21 V.

- GAIN = 1.5x, 2x, 3x, 4x, based on DAC\_SPAN (address D1h) bits.

#### 8.3.2 General-Purpose Input (GPI)

The GPI pin of DACx3701 enables processorless operation. The GPI pin can be configured to trigger various functions, as shown in Table 8-1. The GPI\_EN bit in the TRIGGER (Section 8.6.4) register enables or disables the GPI input. The GPI\_CONFIG field in the CONFIG2 (Section 8.6.3) register maps the GPI pin to various functions. The GPI operations are edge-triggered once the device boots up. Once the power supply ramps up, the device registers the GPI level and executes the associated command. This feature allows the user to configure the initial output state at power-on. By default, the GPI pin is not mapped to any operation. Pull the GPI pin to high or low when not used. When the GPI pin is mapped to a specific function, the corresponding software bit functionality is disabled to avoid a race condition. When the GPI is mapped to margin-high or low trigger function, the output changes dynamically, unlike the behavior with I<sup>2</sup>C-based programming. This behavior is shown in Section 9.2.1.3. All other constraints of the functions are applied to the GPI-based trigger.

| REGISTER NAME                    | GPI_EN | GPI_CONFIG          | PIN FUNCTION                   | PIN EDGE | COMMAND                                       |

|----------------------------------|--------|---------------------|--------------------------------|----------|-----------------------------------------------|

|                                  | 0      | Х                   | None                           | Х        | No Operation (Default)                        |

|                                  | 1      | 000                 | Power-Up, Down                 | Rising   | Power-Up                                      |

|                                  | I      | 000                 | (Hi-Z)                         | Falling  | Hi-Z Power-Down                               |

| -                                | 1      | 001                 | Power-Up, Down                 | Rising   | Power-Up                                      |

|                                  | I      | 001                 | (10-kΩ)                        | Falling  | 10-kΩ Power-Down                              |

|                                  | 1 010  | 010                 | Margin-High, Low               | Rising   | Margin High Trigger                           |

|                                  |        | 010                 |                                | Falling  | Margin Low Trigger                            |

|                                  | 1 0    | 011                 | Function<br>Generation         | Rising   | Start Function Generation                     |

| D2h, CONFIG2 and<br>D3h, TRIGGER |        | 011                 |                                | Falling  | Stop Function Generation                      |

| 2 on, 11 0 0 2 1 0               | 1 100  | 100                 | High-Priority                  | Rising   | Start High-Priority Medical Alarm             |

|                                  | I      | 1 100 Medical Alarm | Medical Alarm                  | Falling  | Stop High-Priority Medical Alarm              |

|                                  | 1 101  | 101                 | Medium-Priority                | Rising   | Start Medium-Priority Medical Alarm           |

|                                  | I      | 101                 | Medical Alarm                  | Falling  | Stop Medium-Priority Medical Alarm            |

|                                  | 1      | 110                 | Low-Priority                   | Rising   | Start Low-Priority Medical Alarm              |

|                                  | 1      |                     | Medical Alarm                  | Falling  | Stop Low-Priority Medical Alarm               |

|                                  | 1      | 111                 | I <sup>2</sup> C Slave Address | Rising   | Enable I <sup>2</sup> C Slave Address Update  |

|                                  | I      |                     | 1 C Slave Addless              | Falling  | Disable I <sup>2</sup> C Slave Address Update |

Table 8-1. GPI Configuration

#### 8.3.3 DAC Update

The DAC output pin (OUT) is updated at the end of  $I^2C$  DAC write frame.

#### 8.3.3.1 DAC Update Busy

The DAC\_UPDATE\_BUSY bit (address D0h) is set to 1 by the device when certain DAC update operations, such as *function generation*, *transition to margin high or low*, or any of the medical alarms are in progress. When the DAC\_UPDATE\_BUSY bit is set to 1, do not write to any of the DAC registers. After the DAC update operation is completed (DAC\_UPDATE\_BUSY = 0), any of the DAC registers can be written.

#### 8.3.4 Nonvolatile Memory (EEPROM or NVM)

The DACx3701 contain nonvolatile memory (NVM) bits. These memory bits are user programmable and erasable, and retain the set values in the absence of a power supply. All the register bits, as shown in Table 8-2, can be stored in the device NVM by setting NVM\_PROG = 1 (address D3h). The NVM\_BUSY bit (address D0h) is set to 1 by device when a NVM write or reload operation is ongoing. During this time, the device blocks all write operations to the device. The NVM\_BUSY bit is set to 0 after the write or reload operation is complete; at this point, all write operations to the device are allowed. The default value for all the registers in the DACx3701 is loaded from NVM as soon as a POR event is issued. Do not perform a read operation from the DAC register while NVM\_BUSY = 1.

The DACx3701 also implement NVM\_RELOAD bit (address D3h). Set this bit to 1 for the device to start an NVM reload operation. After the operation is complete, the device autoresets this bit to 0. During the NVM\_RELOAD operation, the NVM\_BUSY bit is set to 1.

| REGISTER ADDRESS | REGISTER NAME   | BIT ADDRESS | BIT NAME                              |

|------------------|-----------------|-------------|---------------------------------------|

|                  |                 | 13          | DEVICE_LOCK                           |

|                  |                 | 11:9        | CODE_STEP                             |

| D1h              | GENERAL_CONFIG  | 8:5         | SLEW_RATE                             |

| Dill             | GENERAL_CONFIG  | 4:3         | DAC_PDN                               |

|                  |                 | 2           | REF_EN                                |

|                  |                 | 1:0         | DAC_SPAN                              |

|                  |                 | 15:14       | SLAVE_ADDRESS                         |

|                  | CONFIG2         | 13:11       | GPI_CONFIG                            |

| D2h              |                 | 5:4         | INTERBURST_TIME                       |

|                  |                 | 3:2         | PULSE_OFF_TIME                        |

|                  |                 | 1:0         | PULSE_ON_TIME                         |

| D3h              | TRIGGER         | 10          | GPI_EN                                |

| 21h              | DAC_DATA        | 11:2        | DAC_DATA                              |

| 25h              | DAC_MARGIN_HIGH | 11:4        | MARGIN_HIGH (8 most significant bits) |

| 26h              | DAC_MARGIN_LOW  | 11:4        | MARGIN_LOW (8 most significant bits)  |

#### 8.3.4.1 NVM Cyclic Redundancy Check

The DACx3701 implement a cyclic redundancy check (CRC) feature for the device NVM to make sure that the data stored in the device NVM is uncorrupted. There are two types of CRC alarm bits implemented in DACx3701:

- NVM\_CRC\_ALARM\_USER

- NVM\_CRC\_ALARM\_INTERNAL

The NVM\_CRC\_ALARM\_USER bit indicates the status of user-programmable NVM bits, and the NVM\_CRC\_ALARM\_INTERNAL bit indicates the status of internal NVM bits The CRC feature is implemented by storing a 10-Bit CRC (CRC-10-ATM) along with the NVM data each time NVM program operation (write or reload) is performed and during the device start up. The device reads the NVM data and validates the data with the stored CRC. The CRC alarm bits (NVM\_CRC\_ALARM\_USER and NVM\_CRC\_ALARM\_INTERNAL address D0h) report any errors after the data are read from the device NVM.

#### 8.3.4.2 NVM\_CRC\_ALARM\_USER Bit

A logic 1 on NVM\_CRC\_ALARM\_USER bit indicates that the user-programmable NVM data are corrupt. During this condition, all registers in the DAC are initialized with factory reset values, and any DAC registers can be written to or read from. To reset the alarm bits to 0, issue a software reset (see *Section 8.3.7*) command, or cycle power to the DAC. A power cycle also reloads the user-programmable NVM bits. In case of NVM data corruption, program the NVM again.

#### 8.3.4.3 NVM\_CRC\_ALARM\_INTERNAL Bit

A logic 1 on NVM\_CRC\_ALARM\_INTERNAL bit indicates that the internal NVM data are corrupt. During this condition, all registers in the DAC are initialized with factory reset values, and any DAC registers can be written to or read from. In case of a temporary failure, to reset the alarm bits to 0, issue a software reset (see Section 8.3.7) command or cycle power to the DAC.

#### 8.3.5 Programmable Slew Rate

When the DAC data registers are written, the voltage on DAC output ( $V_{OUT}$ ) immediately transitions to the new code following the slew rate and settling time specified in *Section 7.5*. The slew rate control feature allows the user to control the rate at which the output voltage ( $V_{OUT}$ ) changes. When this feature is enabled (using SLEW\_RATE[3:0] bits), the DAC output changes from the current code to the code in MARGIN\_HIGH (address 25h) or MARGIN\_LOW (address 26h) registers (when margin high or low commands are issued to the DAC) using the step and rate set in CODE\_STEP and SLEW\_RATE bits. With the default slew rate control setting (CODE\_STEP and SLEW\_RATE bits, address D1h), the output changes smoothly at a rate limited by the output drive circuitry and the attached load. Using this feature, the output steps digitally at a rate defined by bits CODE\_STEP and SLEW\_RATE on address D1h. SLEW\_RATE defines the rate at which the digital slew updates; CODE\_STEP defines the amount by which the output value changes at each update. Table 8-3 and Table 8-4 show different settings for CODE\_STEP and SLEW\_RATE.

When the slew rate control feature is used, the output changes happen at the programmed slew rate. This configuration results in a staircase formation at the output. Do not write to CODE\_STEP, SLEW\_RATE, or DAC\_DATA during the output slew.

| Table 8-3. Code Step         |              |              |              |                                     |  |  |

|------------------------------|--------------|--------------|--------------|-------------------------------------|--|--|

| REGISTER ADDRESS<br>AND NAME | CODE_STEP[2] | CODE_STEP[1] | CODE_STEP[0] | COMMENT                             |  |  |

|                              | 0            | 0            | 0            | Code step size = 1 LSB<br>(default) |  |  |

|                              | 0            | 0            | 1            | Code step size = 2 LSB              |  |  |

|                              | 0            | 1            | 0            | Code step size = 3 LSB              |  |  |

| D1h, GENERAL_CONFIG          | 0            | 1            | 1            | Code step size = 4 LSB              |  |  |

|                              | 1            | 0            | 0            | Code step size = 6 LSB              |  |  |

|                              | 1            | 0            | 1            | Code step size = 8 LSB              |  |  |

|                              | 1            | 1            | 0            | Code step size = 16 LSB             |  |  |

|                              | 1            | 1            | 1            | Code step size = 32 LSB             |  |  |

## Table 8-4. Slew Rate

|                              |              |              | elett late   |              |                           |

|------------------------------|--------------|--------------|--------------|--------------|---------------------------|

| REGISTER ADDRESS<br>AND NAME | SLEW_RATE[3] | SLEW_RATE[2] | SLEW_RATE[1] | SLEW_RATE[0] | TIME PERIOD (PER<br>STEP) |

|                              | 0            | 0            | 0            | 0            | 25.6 µs                   |

|                              | 0            | 0            | 0            | 1            | 32 µs                     |

|                              | 0            | 0            | 1            | 0            | 38.4 μs                   |

|                              | 0            | 0            | 1            | 1            | 44.8 µs                   |

|                              | 0            | 1            | 0            | 0            | 204.8 µs                  |

|                              | 0            | 1            | 0            | 1            | 256 µs                    |

|                              | 0            | 1            | 1            | 0            | 307.2 µs                  |

| D1h, GENERAL_CONFIG          | 0            | 1            | 1            | 1            | 819.2 μs                  |

| DIII, GENERAL_CONFIG         | 1            | 0            | 0            | 0            | 1638.4 µs                 |

|                              | 1            | 0            | 0            | 1            | 2457.6 µs                 |

|                              | 1            | 0            | 1            | 0            | 3276.8 µs                 |

|                              | 1            | 0            | 1            | 1            | 4915.2 µs                 |

|                              | 1            | 1            | 0            | 0            | 12 µs                     |

|                              | 1            | 1            | 0            | 1            | 8 µs                      |

|                              | 1            | 1            | 1            | 0            | 4 µs                      |

|                              | 1            | 1            | 1            | 1            | 0 μs, no slew (default)   |

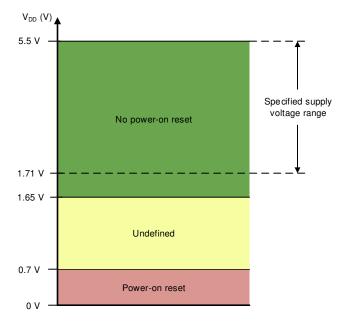

#### 8.3.6 Power-on-Reset (POR)

The DACx3701 family of devices includes a power-on reset (POR) function that controls the output voltage at power up. After the  $V_{DD}$  supply has been established, a POR event is issued. The POR causes all registers to initialize to default values, and communication with the device is valid only after a 30-ms, POR delay. The default value for all the registers in the DACx3701 is loaded from NVM as soon as the POR event is issued.

When the device powers up, a POR circuit sets the device to the default mode. The POR circuit requires specific  $V_{DD}$  levels, as indicated in Figure 8-1, in order to make sure that the internal capacitors discharge and reset the device on power up. To make sure that a POR occurs,  $V_{DD}$  must be less than 0.7 V for at least 1 ms. When  $V_{DD}$  drops to less than 1.65 V, but remains greater than 0.7 V (shown as the undefined region), the device may or may not reset under all specified temperature and power-supply conditions. In this case, initiate a POR. When  $V_{DD}$  remains greater than 1.65 V, a POR does not occur.

Figure 8-1. Threshold Levels for V<sub>DD</sub> POR Circuit

#### 8.3.7 Software Reset

To initiate a device software reset event, write the reserved code 1010 to the SW\_RESET (address D3h). A software reset initiates a POR event.

#### 8.3.8 Device Lock Feature

The DACx3701 implement a device lock feature that prevents an accidental or unintended write to the DAC registers. The device locks all the registers when the DEVICE\_LOCK bit (address D1h) is set to 1. To bypass the DEVICE\_LOCK setting, write 0101 to the DEVICE\_UNLOCK\_CODE bits (address D3h).

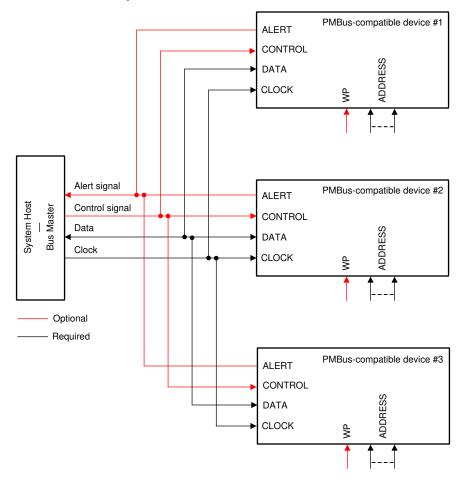

#### 8.3.9 PMBus Compatibility

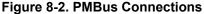

The PMBus protocol is an I<sup>2</sup>C-based communication standard for power-supply management. PMBus contains standard command codes tailored to power supply applications. The DACx3701 implement some PMBus commands such as *Turn Off, Turn On, Margin Low, Margin High, Communication Failure Alert Bit (CML)*, as well as *PMBUS revision*. Figure 8-2 shows typical PMBus connections. The EN\_PMBUS bit (Bit 12, address D1h) must be set to 1 to enable the PMBus protocol.

Similar to I<sup>2</sup>C, PMBus is a variable length packet of 8-bit data bytes, each with a receiver acknowledge, wrapped between a start and stop bit. The first byte is always a 7-bit *slave address* followed by a *write* bit, sometimes called the *even address* that identifies the intended receiver of the packet. The second byte is an 8-bit *command* byte, identifying the PMBus command being transmitted using the respective command code. After the command byte, the transmitter either sends data associated with the command to write to the receiver command register (from most significant byte to least significant byte), or sends a new start bit indicating the desire to read the data associated with the command register from the receiver. Then the receiver transmits the data following the same most significant byte first format (see Table 8-11).

#### 8.4 Device Functional Modes

## 8.4.1 Power Down Mode

The DACx3701 output amplifier and internal reference can be independently powered down through the DAC\_PDN bits (address D1h). At power up, the DAC output and the internal reference are disabled by default. In power-down mode, the DAC output (OUT pin) is in a high-impedance state. To change this state to  $10k\Omega$ -A<sub>GND</sub> (at power up), use the DAC\_PDN bits (address D1h).

The DAC power-up state can be programmed to any state (power-down or normal mode) using the NVM. Table 8-5 shows the DAC power-down bits.

| REGISTER ADDRESS AND NAME | DAC_PDN[1] | DAC_PDN[0] | DESCRIPTION                                     |

|---------------------------|------------|------------|-------------------------------------------------|

|                           | 0          | 0          | Power up                                        |

|                           | 0          | 1          | Power down to 10 $k\Omega$                      |

| D1h, GENERAL_CONFIG       | 1          | 0          | Power down to high impedance (HiZ)<br>(default) |

|                           | 1          | 1          | Power down to 10 $k\Omega$                      |

#### Table 8-5. DAC Power-Down Bits

#### 8.4.2 Continuous Waveform Generation (CWG) Mode

The DACx3701 implement a continuous waveform generation feature. To set the device to this mode, set the START\_FUNC\_GEN (address D3h) to 1. In this mode, the DAC output pin (OUT) generates a continuous waveform based on the FUNC\_CONFIG bits (address D1h). Table 8-6 shows the continuous waveforms that can be generated in this mode. The frequency of the waveform depends on the resistive and capacitive load on the OUT pin, high and low codes, and slew rate settings as shown in the following equations.

$$f_{SQUARE-WAVE} = \frac{1}{2 \times SLEW_RATE}$$

(3)

$$f_{TRIANGLE-WAVE} = \frac{1}{2 \times SLEW_RATE \times \left(\frac{MARGIN_HIGH - MARGIN_LOW + 1}{CODE_STEP}\right)}$$

(4)

$$f_{SAWTOOTH-WAVE} = \frac{1}{SLEW_RATE \times \left(\frac{MARGIN_HIGH - MARGIN_LOW + 1}{CODE_STEP}\right)}$$

(5)

where:

- SLEW\_RATE is the programmable DAC slew rate specified in Table 8-4.

- MARGIN\_HIGH and MARGIN\_LOW are the programmable DAC codes.

- CODE\_STEP is the programmable DAC step code in Table 8-3.

| Table 8-6. FUNC_CONFIG bits |                |                |                                                                                                                                                                                                                  |  |  |  |

|-----------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| REGISTER ADDRESS AND NAME   | FUNC_CONFIG[1] | FUNC_CONFIG[0] | DESCRIPTION                                                                                                                                                                                                      |  |  |  |

|                             | 0              | 0              | Generates a triangle wave between<br>MARGIN_HIGH (address 25h) code to<br>MARGIN_LOW (address 26h) code with slope<br>defined by SLEW_RATE and CODE_STEP<br>(address D1h) bits                                   |  |  |  |

| D1h. GENERAL CONFIG         | 0              | 1              | Generates Saw-Tooth wave between<br>MARGIN_HIGH (address 25h) code to<br>MARGIN_LOW (address 26h) code, with rising<br>slope defined by SLEW_RATE and CODE_STEP<br>(address D1h) bits and immediate falling edge |  |  |  |

| DIII, GENERAL_CONTIG        | 1              | 0              | Generates Saw-Tooth wave between<br>MARGIN_HIGH (address 25h) code to<br>MARGIN_LOW (address 26h) code, with falling<br>slope defined by SLEW_RATE and CODE_STEP<br>(address D1h) bits and immediate rising edge |  |  |  |

|                             | 1              | 1              | Generates a square wave between<br>MARGIN_HIGH (address 25h) code to<br>MARGIN_LOW (address 26h) code with pulse<br>high and low period defined by SLEW_RATE<br>(address D1h) bits                               |  |  |  |

#### 8.4.3 PMBus Compatibility Mode

The DACx3701 I<sup>2</sup>C interface implements some of the PMBus commands. Table 8-7 shows the supported PMBus commands that are implemented in DACx3701.The DAC uses MARGIN\_LOW (address 26h), MARGIN\_HIGH (address 25h) bits, SLEW\_RATE, and CODE\_STEP bits (address D1h) for PMBUS\_OPERATION\_CMD. The EN\_PMBUS bit (Bit 12, address D1h) must be set to 1 to enable the PMBus protocol.

| REGISTER ADDRESS AND NAME | PMBUS_OPERATION_CMD[15:8] | DESCRIPTION |

|---------------------------|---------------------------|-------------|

|                           | 00h                       | Turn off    |

| 01h, PMBUS OPERATION      | 80h                       | Turn on     |

| UTII, FINIBUS_OFERATION   | 94h                       | Margin low  |

|                           | A4h                       | Margin high |

#### Table 8-7. PMBus Operation Commands

The DACx3701 also implement PMBus features such as group command protocol and communication time-out failure. The CML bit (address 78h) indicates a communication fault in the PMBus. This bit is reset by writing 1.

To get the PMBus version, read the PMBUS\_VERSION bits (address 98h).

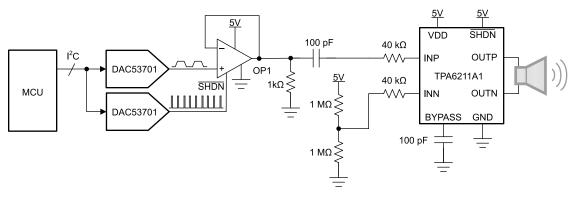

#### 8.4.4 Medical Alarm Generation Mode

The DACx3701 are also used to generate continuous alarm tones for medical devices. Use a suitable analog mixer, audio amplifier, and a speaker to generate low, medium, or high priority alarm tones. See the *Application and Implementation* section for more details. The DACx3701 allow tunability and configurability to support different alarm generation. Using this approach, configurable medical alarm tones can be generated with a simple circuit, and with no need for runtime software. The GPI pin can be used for trigerring an alarm directly without using the I<sup>2</sup>C interface. This feature helps when the processor fails or the software crashes. This feature is also helpful when there is a power failure and the alarm circuit is driven by a battery or a super capacitor.

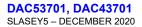

#### 8.4.4.1 Low-Priority Alarm

The MED\_ALARM\_LP bit (address D2h) is used to trigger a medical low-priority alarm generation. The DAC generates a continuous-alarm signal until this bit is set back to 0. After the bit is set to 0, the device does not abruptly end the alarm generation; the device stops only after completing the ongoing burst.

#### 8.4.4.2 Medium-Priority Alarm

The MED\_ALARM\_MP bit (address D2h) is used to trigger a medical medium-priority alarm generation. The DAC generates a continuous-alarm signal until this bit is set back to 0. After the bit is set to 0, the device does not abruptly end the alarm generation; the device stops only after completing the ongoing burst.

#### 8.4.4.3 High-Priority Alarm

The MED\_ALARM\_HP bit (address D2h) is used to trigger a medical high-priority alarm generation. The DAC generates a continuous-alarm signal until this bit is set back to 0. After the bit is set to 0, the device does not abruptly end the alarm generation; the device stops only after completing the ongoing burst.

#### 8.4.4.4 Interburst Time

The INTERBURST\_TIME bit (address D2h) is used set the time between two adjacent bursts. Table 8-8 lists the INTERBURST\_TIME settings.

|                              | Ia                   |                                        |                                             |                                       |

|------------------------------|----------------------|----------------------------------------|---------------------------------------------|---------------------------------------|

| REGISTER ADDRESS<br>AND NAME | INTERBURST_TIME[1:0] | HIGH PRIORITY ALARM<br>INTERBURST TIME | MEDIUM PRIORITY<br>ALARM INTERBURST<br>TIME | LOW PRIORITY ALARM<br>INTERBURST TIME |

|                              | 00                   | 2.55 s                                 | 2.60 s                                      |                                       |

| D2h, CONFIG2                 | 01                   | 2.96 s                                 | 3.06 s                                      | 16 s                                  |

| D211, CONFIG2                | 10                   | 3.38 s                                 | 3.52 s                                      | 105                                   |

|                              | 11                   | 3.80 s                                 | 4.00 s                                      |                                       |

#### Table 8-8. Interburst Time

#### 8.4.4.5 Pulse Off Time

The PULSE\_OFF\_TIME bit (address D2h) is used to control the low period of trapezoid in a medical alarm waveform. Table 8-9 lists the PULSE\_OFF\_TIME settings.

|                              | 10                  |                                       |                                            |                                      |

|------------------------------|---------------------|---------------------------------------|--------------------------------------------|--------------------------------------|

| REGISTER ADDRESS<br>AND NAME | PULSE_OFF_TIME[1:0] | HIGH PRIORITY ALARM<br>PULSE OFF TIME | MEDIUM PRIORITY<br>ALARM PULSE OFF<br>TIME | LOW PRIORITY ALARM<br>PULSE OFF TIME |

| D2h, CONFIG2                 | 00                  | 15 ms                                 | 40 ms                                      | 40 ms                                |

|                              | 01                  | 36 ms                                 | 60 ms                                      | 60 ms                                |

|                              | 10                  | 58 ms                                 | 80 ms                                      | 80 ms                                |

|                              | 11                  | 80 ms                                 | 100 ms                                     | 100 ms                               |

Table 8-9. Pulse Off Time

#### 8.4.4.6 Pulse On Time

The PULSE\_ON\_TIME bit (address D2h) controls the high period of trapezoid in a medical alarm waveform. Table 8-10 lists the PULSE\_ON\_TIME settings.

#### Table 8-10. Pulse On Time

| REGISTER ADDRESS<br>AND NAME | PULSE_ON_TIME[1:0] | HIGH PRIORITY ALARM<br>PULSE ON TIME | MEDIUM PRIORITY<br>ALARM PULSE ON TIME | LOW PRIORITY ALARM<br>PULSE ON TIME |

|------------------------------|--------------------|--------------------------------------|----------------------------------------|-------------------------------------|

|                              | 00                 | 80 ms                                | 130 ms                                 | 130 ms                              |

| D2h, CONFIG2                 | 01                 | 103 ms                               | 153 ms                                 | 153 ms                              |

|                              | 10                 | 126 ms                               | 176 ms                                 | 176 ms                              |

|                              | 11                 | 150 ms                               | 200 ms                                 | 200 ms                              |

## 8.5 Programming

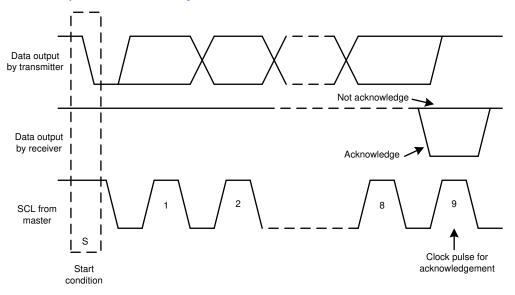

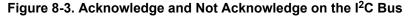

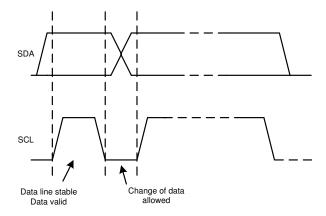

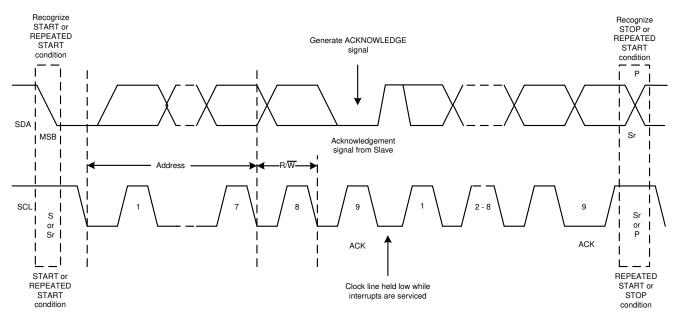

The DACx3701 devices have a 2-wire serial interface (SCL and SDA) as shown in the pin diagram of Section 6. The  $I^2C$  bus consists of a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is idle, both SDA and SCL lines are pulled high. All the  $I^2C$ -compatible devices connect to the  $I^2C$  bus through the open drain I/O pins, SDA and SCL.

The  $l^2C$  specification states that the device that controls communication is called a *master*, and the devices that are controlled by the master are called *slaves*. The master device generates the SCL signal. The master device also generates special timing conditions (start condition, repeated start condition, and stop condition) on the bus to indicate the start or stop of a data transfer. Device addressing is completed by the master. The master device on an  $l^2C$  bus is typically a microcontroller or digital signal processor (DSP). The DACx3701 family operates as a slave device on the  $l^2C$  bus. A slave device acknowledges master commands, and upon master control, receives or transmits data.

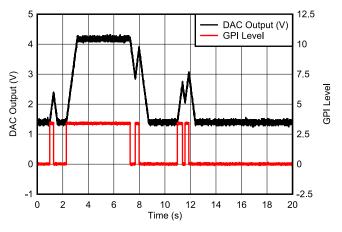

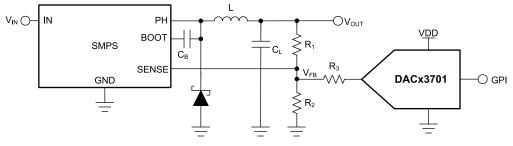

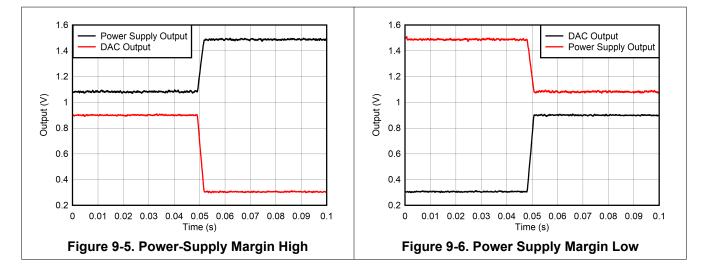

Typically, theDACx3701 family operates as a slave receiver. A master device writes to the DACx3701, a slave receiver. However, if a master device requires the DACx3701 internal register data, the DACx3701 operate as a slave transmitter. In this case, the master device reads from the DACx3701. According to I<sup>2</sup>C terminology, read and write refer to the master device.