# iW-RainboW-G36S Zynq Ultrascale+ MPSoC SBC Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

#### **Document Revision History**

| Document Number               |  | iW-PRGGG-UM-01-R2.0-REL0.1-Hardware |  |  |

|-------------------------------|--|-------------------------------------|--|--|

| ReleaseDateDescription        |  | Description                         |  |  |

| 0.1 18 <sup>th</sup> May 2021 |  | Initial Draft Version               |  |  |

PROPRIETARY NOTICE: This document contains proprietary material for the sole use of the intended recipient(s). Do not read this document if you are not the intended recipient. Any review, use, distribution or disclosure by others is strictly prohibited. If you are not the intended recipient (or authorized to receive for the recipient), you are hereby notified that any disclosure, copying distribution or use of any of the information contained within this document is STRICTLY PROHIBITED. Thank you. "iWave Systems Tech. Pvt. Ltd."

#### Disclaimer

iWave Systems reserves the right to change details in this publication including but not limited to any Product specification without notice.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CPU and other major components used in this product may have several silicon errata associated with it. Under no circumstances, iWave Systems shall be liable for the silicon errata and associated issues.

#### Trademarks

All registered trademarks, product names mentioned in this publication are the property of their respective owners and used for identification purposes only.

#### Certification

iWave Systems Technologies Pvt. Ltd. is an ISO 9001:2015 Certified Company.

#### Warranty & RMA

Warranty support for Hardware: 1 Year from iWave or iWave's EMS partner. For warranty terms, go through the below web link, <u>http://www.iwavesystems.com/support/warranty.html</u>

For Return Merchandise Authorization (RMA), go through the below web link,

http://www.iwavesystems.com/support/rma.html

#### **Technical Support**

iWave Systems technical support team is committed to provide the best possible support for our customers so that our Hardware and Software can be easily migrated and used.

For assistance, contact our Technical Support team at,

Email : <u>support.ip@iwavesystems.com</u> Website : <u>www.iwavesystems.com</u> Address : iWave Systems Technologies Pvt. Ltd. # 7/B, 29<sup>th</sup> Main, BTM Layout 2<sup>nd</sup> Stage, Bangalore, Karnataka, India – 560076

iWave Systems Technologies Pvt. Ltd.

### **Table of Contents**

| 1.2       SBC Overview         1.3       List of Acronyms         1.4       Terminlogy Description         1.5       References         2.       ARCHITECTURE AND DESIGN         2.1       Zynq Ultrascale+ MPSoC SBC Block Diagram         2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.3.1       MPSoC Power         2.3.2       MPSoC Reference Clock         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PS         2.5.4       EPROM         2.5.5       Micro SD Connector (Optional)         2.6       Patters from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RI45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR.         2.7.1       Dislay Opt Connector         2.7.2       Dual USB30 Type A Jack         2.7.3       M.2 Key B Connector         2.7.4       Dua                                                                            | INTROD   | DUCTION                                            | 8  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------|----|

| 1.3       List of Acronyms         1.4       Terminlogy Description         1.5       References         2.       ARCHITECTURE AND DESIGN         2.1       Zynq Ultrascale+ MPSoC SBC Block Diagram         2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.3.1       MPSoC Power         2.3.2       MPSoC Reset         2.3.3       MPSoC Configuration & Status         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PS         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR.         2.7.1       Display Port Connector         2.7.2       Dual US                                                                            | 1.1 Pur  | irpose                                             | 8  |

| 1.4       Terminlogy Description         1.5       References         2.       ARCHITECTURE AND DESIGN         2.1       Zynq Ultrascale+ MPSoC SBC Block Diagram         2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.4       MPSoC Power         2.3.1       MPSoC Reset         2.3.2       MPSoC Reset         2.3.3       MPSoC Configuration & Status         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory.         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2                                                                             | 1.2 SBC  | C Overview                                         | 8  |

| 1.4       Terminlogy Description         1.5       References         2.       ARCHITECTURE AND DESIGN         2.1       Zynq Ultrascale+ MPSoC SBC Block Diagram         2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.4       MPSoC Power         2.3.1       MPSoC Reset         2.3.2       MPSoC Reset         2.3.3       MPSoC Configuration & Status         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory.         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2                                                                             | 1.3 List | t of Acronyms                                      | 8  |

| 1.5       References         2.       ARCHITECTURE AND DESIGN         2.1       Zynq Ultrascale+ MPSoC SBC Block Diagram         2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.3.1       MPSoC Power         2.3.2       MPSoC Reset         2.3.3       MPSoC Configuration & Status         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Configuration & Status         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.8       HDMI Input Connector         2.8.3 <td>1.4 Ter</td> <td>rminlogy Description</td> <td>10</td>            | 1.4 Ter  | rminlogy Description                               | 10 |

| 2.1       Zynq Ultrascale+ MPSoC SBC Block Diagram         2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3.1       MPSoC Power         2.3.2       MPSoC Reset         2.3.3       MPSoC Reference Clock         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector with SATA & USB3.0         2.8       Features from PL-GTH         2.8.1       HDMI louput Connector         2.8.2       SFP+ Connector         2.8.3       SFP+ Connector         2.8.4 <td></td> <td>ferences</td> <td></td>                                |          | ferences                                           |    |

| 2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.3.1       MPSoC Reset         2.3.2       MPSoC Reference Clock         2.3.3       MPSoC Configuration & Status         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR.         2.7.1       Display Port Connector .         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector with SATA & USB3.0         2.8       Features from PL-GTH.         2.8.1       HDMI loupt Connector         2.8.2       SFP+ Connector.         2                                                                   | ARCHITI  | ECTURE AND DESIGN                                  | 11 |

| 2.2       Zynq Ultrascale+ MPSoC SBC Features         2.3       Zynq Ultrascale+ MPSoC         2.3.1       MPSoC Power         2.3.2       MPSoC Reset         2.3.3       MPSoC Reference Clock         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ4S Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR.         2.7.1       Display Port Connector .         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector with SATA & USB3.0         2.8       Features from PL-GTH.         2.8.1       HDMI loupt Connector         2.8.2       SFP+ Connector.         2.8.3       <                                                                        | 2.1 Zvr  | ng Ultrascale+ MPSoC SBC Block Diagram             | 11 |

| 2.3       Zynq Ultrascale+ MPSoC         2.3.1       MPSoC Power         2.3.2       MPSoC Reset         2.3.3       MPSoC Ceference Clock         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory.         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash.         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector with SATA & USB3.0         2.8       Features from PL-GTH         2.8.1       HDMI lout Connector         2.8.2       SFP+ Connector.         2.8.3       SFP+ Connector.         2.8.4       3G/12G SDI Nut (Op                                                                            | -        |                                                    |    |

| 2.3.1       MPSoC Power         2.3.2       MPSoC Reset         2.3.3       MPSoC Configuration & Status         2.3.4       MPSoC Boot Mode         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory.         2.5.1       DDR4 SDRAM for PS.         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash.         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.3       Debug UART Header         2.7       Features from PS-GTR.         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector with SATA & USB3.0         2.8       Features from PL-GTH.         2.8.1       HDMI lout Connector         2.8.2       SG/12G SDI N (Optional)         2.8.3       SFP+ Connector.         2.8.4       3G/12G SDI N (Optional)         2.8.5       3G/12G SDI N (Uptional)         2.9       Additional Features                                                                                     | •        | •                                                  |    |

| 2.3.3       MPSoC Reference Clock         2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector         2.8.4       Features from PL-GTH         2.8.1       HDMI Input Connector         2.8.2       HDMI Output Connector         2.8.4       3G/12G SDI IN (Optional)         2.8.5       3G/12G SDI Output (Optional)         2.8.5       3G/12G SDI Output (Optional)         2.9       Additional Features         2.9.1                                                                         |          | MPSoC Power                                        |    |

| 2.3.4       MPSoC Configuration & Status         2.3.5       MPSoC Boot Mode         2.3.6       MPSoC System Monitor/ADC         2.4       PMIC with RTC         2.5       Memory         2.5.1       DDR4 SDRAM for PS         2.5.2       DDR4 SDRAM for PL         2.5.3       eMMC Flash         2.5.4       EEPROM         2.5.5       Micro SD Connector (Optional)         2.6       Fearures from PS Block         2.6.1       Dual 10/100/1000Mbps Ethernet through RJ45 Magjack         2.6.2       WLAN & BT Module with Antenna connector         2.6.3       Debug UART Header         2.7       Features from PS-GTR.         2.7.1       Display Port Connector         2.7.2       Dual USB3.0 Type A Jack         2.7.3       M.2 Key B Connector with SATA & USB3.0         2.8       Features from PL-GTH.         2.8.1       HDMI Input Connector         2.8.2       HDMI Output Connector         2.8.3       SFP+ Connector         2.8.4       3G/12G SDI IN (Optional)         2.8.5       3G/12G SDI Output (Optional)         2.8.5       3G/12G SDI Output (Optional)         2.8.5       3G/12G SDI Output (Optional) <tr< td=""><td>2.3.2</td><td>MPSoC Reset</td><td>19</td></tr<> | 2.3.2    | MPSoC Reset                                        | 19 |

| 2.3.5       MPSoC Boot Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.3.3 N  | MPSoC Reference Clock                              | 19 |

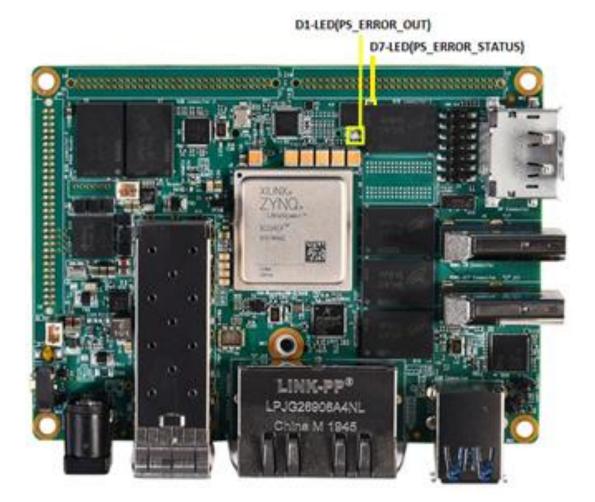

| 2.3.6MPSoC System Monitor/ADC2.4PMIC with RTC2.5Memory.2.5.1DDR4 SDRAM for PS.2.5.2DDR4 SDRAM for PL2.5.3eMMC Flash.2.5.4EEPROM2.5.5Micro SD Connector (Optional)2.6Fearures from PS Block.2.6.1Dual 10/100/1000Mbps Ethernet through RJ45 Magjack2.6.2WLAN & BT Module with Antenna connector.2.6.3Debug UART Header2.7Features from PS-GTR.2.7.1Display Port Connector .2.7.2Dual USB3.0 Type A Jack2.7.3M.2 Key B Connector with SATA & USB3.02.8Features from PL-GTH.2.8.1HDMI Input Connector .2.8.2HDMI Output Connector .2.8.3SFP+ Connector .2.8.43G/12G SDI IN (Optional) .2.9Additional Features .2.9.1Clock Synthesizers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3.4    | MPSoC Configuration & Status                       | 20 |

| <ul> <li>2.4 PMIC with RTC.</li> <li>2.5 Memory.</li> <li>2.5.1 DDR4 SDRAM for PS.</li> <li>2.5.2 DDR4 SDRAM for PL.</li> <li>2.5.3 eMMC Flash.</li> <li>2.5.4 EEPROM .</li> <li>2.5.5 Micro SD Connector (Optional)</li> <li>2.6 Fearures from PS Block.</li> <li>2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack .</li> <li>2.6.2 WLAN &amp; BT Module with Antenna connector.</li> <li>2.6.3 Debug UART Header .</li> <li>2.7 Features from PS-GTR.</li> <li>2.7.1 Display Port Connector .</li> <li>2.7.2 Dual USB3.0 Type A Jack .</li> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH.</li> <li>2.8.1 HDMI Input Connector .</li> <li>2.8.2 HDMI Output Connector .</li> <li>2.8.3 SFP+ Connector .</li> <li>2.8.4 3G/12G SDI IN (Optional) .</li> <li>2.9 Additional Features .</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                               |          | MPSoC Boot Mode                                    |    |

| <ul> <li>2.4 PMIC with RTC.</li> <li>2.5 Memory.</li> <li>2.5.1 DDR4 SDRAM for PS.</li> <li>2.5.2 DDR4 SDRAM for PL.</li> <li>2.5.3 eMMC Flash.</li> <li>2.5.4 EEPROM .</li> <li>2.5.5 Micro SD Connector (Optional)</li> <li>2.6 Fearures from PS Block.</li> <li>2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack .</li> <li>2.6.2 WLAN &amp; BT Module with Antenna connector.</li> <li>2.6.3 Debug UART Header .</li> <li>2.7 Features from PS-GTR.</li> <li>2.7.1 Display Port Connector .</li> <li>2.7.2 Dual USB3.0 Type A Jack .</li> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH.</li> <li>2.8.1 HDMI Input Connector .</li> <li>2.8.2 HDMI Output Connector .</li> <li>2.8.3 SFP+ Connector .</li> <li>2.8.4 3G/12G SDI IN (Optional) .</li> <li>2.9 Additional Features .</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                               | 2.3.6 N  | MPSoC System Monitor/ADC                           | 21 |

| <ul> <li>2.5.1 DDR4 SDRAM for PS.</li> <li>2.5.2 DDR4 SDRAM for PL.</li> <li>2.5.3 eMMC Flash</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | /IC with RTC                                       |    |

| <ul> <li>2.5.2 DDR4 SDRAM for PL.</li> <li>2.5.3 eMMC Flash</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.5 Me   | emory                                              | 22 |

| <ul> <li>2.5.3 eMMC Flash</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.5.1 [  | DDR4 SDRAM for PS                                  | 22 |

| <ul> <li>2.5.4 EEPROM</li> <li>2.5.5 Micro SD Connector (Optional)</li> <li>2.6 Fearures from PS Block</li> <li>2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack</li> <li>2.6.2 WLAN &amp; BT Module with Antenna connector</li> <li>2.6.3 Debug UART Header</li> <li>2.6.7 Features from PS-GTR</li> <li>2.7 Features from PS-GTR</li> <li>2.7.1 Display Port Connector</li> <li>2.7.2 Dual USB3.0 Type A Jack</li> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH</li> <li>2.8.1 HDMI Input Connector</li> <li>2.8.2 HDMI Output Connector</li> <li>2.8.3 SFP+ Connector</li> <li>2.8.4 3G/12G SDI IN (Optional)</li> <li>2.8.5 3G/12G SDI Output (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.5.2 [  | DDR4 SDRAM for PL                                  | 22 |

| <ul> <li>2.5.5 Micro SD Connector (Optional)</li> <li>2.6 Fearures from PS Block</li> <li>2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack</li> <li>2.6.2 WLAN &amp; BT Module with Antenna connector</li> <li>2.6.3 Debug UART Header</li> <li>2.6.3 Debug UART Header</li> <li>2.7 Features from PS-GTR</li> <li>2.7.1 Display Port Connector</li> <li>2.7.2 Dual USB3.0 Type A Jack</li> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH</li> <li>2.8.1 HDMI Input Connector</li> <li>2.8.2 HDMI Output Connector</li> <li>2.8.3 SFP+ Connector</li> <li>2.8.4 3G/12G SDI IN (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.5.3 €  | eMMC Flash                                         | 22 |

| <ul> <li>2.6 Fearures from PS Block.</li> <li>2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.5.4 E  | EEPROM                                             | 22 |

| <ul> <li>2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack</li> <li>2.6.2 WLAN &amp; BT Module with Antenna connector.</li> <li>2.6.3 Debug UART Header</li> <li>2.6.3 Debug UART Header</li> <li>2.7 Features from PS-GTR.</li> <li>2.7.1 Display Port Connector</li> <li>2.7.2 Dual USB3.0 Type A Jack</li> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH.</li> <li>2.8.1 HDMI Input Connector</li> <li>2.8.2 HDMI Output Connector</li> <li>2.8.3 SFP+ Connector</li> <li>2.8.4 3G/12G SDI IN (Optional)</li> <li>2.8.5 3G/12G SDI Output (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.5.5 N  | Micro SD Connector (Optional)                      | 23 |

| <ul> <li>2.6.2 WLAN &amp; BT Module with Antenna connector</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.6 Fea  | arures from PS Block                               | 24 |

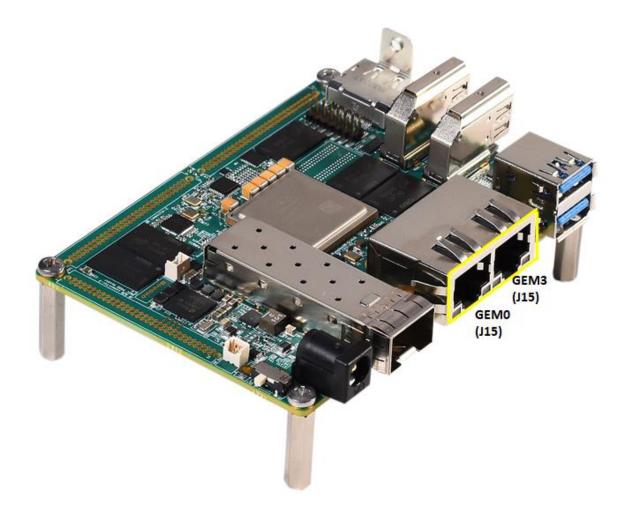

| <ul> <li>2.6.3 Debug UART Header</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.6.1    | Dual 10/100/1000Mbps Ethernet through RJ45 Magjack | 24 |

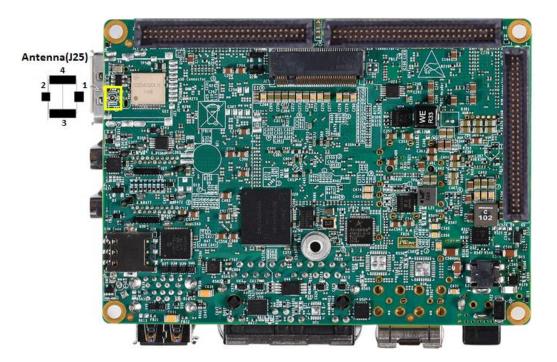

| <ul> <li>2.7 Features from PS-GTR.</li> <li>2.7.1 Display Port Connector</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.6.2 \  | WLAN & BT Module with Antenna connector            | 25 |

| <ul> <li>2.7.1 Display Port Connector</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.6.3    | Debug UART Header                                  | 26 |

| <ul> <li>2.7.2 Dual USB3.0 Type A Jack</li> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH.</li> <li>2.8.1 HDMI Input Connector</li> <li>2.8.2 HDMI Output Connector</li> <li>2.8.3 SFP+ Connector.</li> <li>2.8.4 3G/12G SDI IN (Optional)</li> <li>2.8.5 3G/12G SDI Output (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.7 Fea  | atures from PS-GTR                                 | 27 |

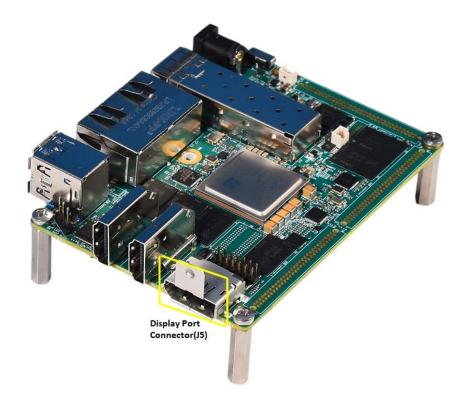

| <ul> <li>2.7.3 M.2 Key B Connector with SATA &amp; USB3.0</li> <li>2.8 Features from PL-GTH.</li> <li>2.8.1 HDMI Input Connector</li> <li>2.8.2 HDMI Output Connector</li> <li>2.8.3 SFP+ Connector.</li> <li>2.8.4 3G/12G SDI IN (Optional)</li> <li>2.8.5 3G/12G SDI Output (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.7.1    | Display Port Connector                             | 27 |

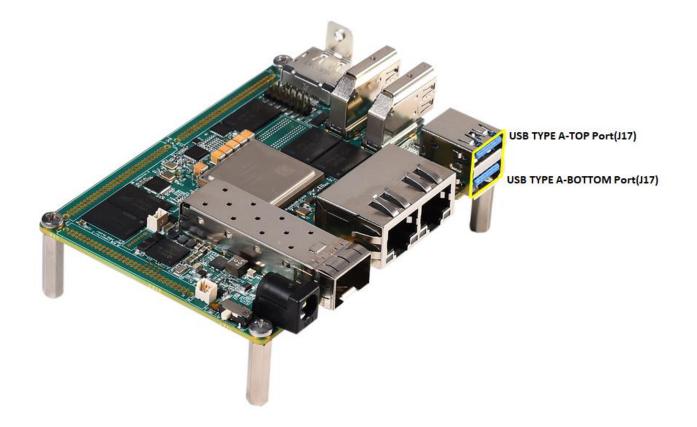

| <ul> <li>2.8 Features from PL-GTH</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.7.2    | Dual USB3.0 Type A Jack                            | 28 |

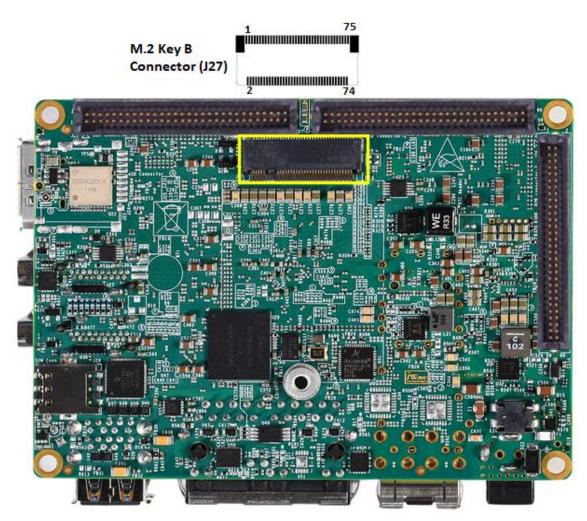

| <ul> <li>2.8.1 HDMI Input Connector</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.7.3 N  | M.2 Key B Connector with SATA & USB3.0             | 29 |

| <ul> <li>2.8.2 HDMI Output Connector</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.8 Fea  | atures from PL-GTH                                 | 33 |

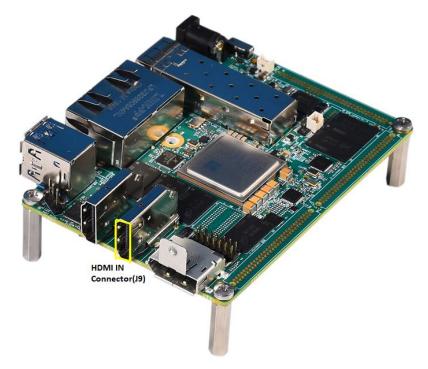

| <ul> <li>2.8.3 SFP+ Connector</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.8.1 H  | HDMI Input Connector                               | 33 |

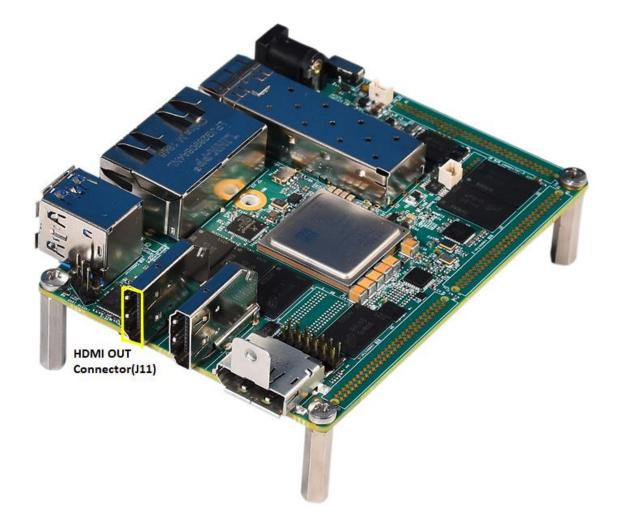

| <ul> <li>2.8.4 3G/12G SDI IN (Optional)</li> <li>2.8.5 3G/12G SDI Output (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.8.2 H  | HDMI Output Connector                              | 34 |

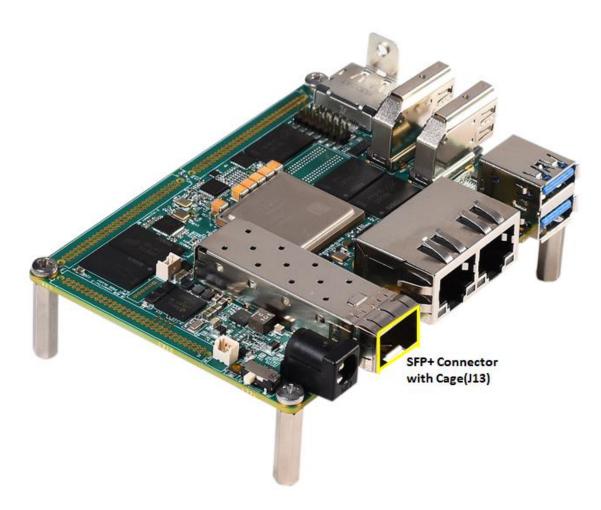

| <ul> <li>2.8.5 3G/12G SDI Output (Optional)</li> <li>2.9 Additional Features</li> <li>2.9.1 Clock Synthesizers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.8.3    | SFP+ Connector                                     | 35 |

| 2.9       Additional Features         2.9.1       Clock Synthesizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.8.4    | 3G/12G SDI IN (Optional)                           | 37 |

| 2.9.1 Clock Synthesizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.8.5    | 3G/12G SDI Output (Optional)                       | 37 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.9 Add  | lditional Features                                 |    |

| 2.9.2 JTAG Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.9.1 (  | Clock Synthesizers                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.9.2 J  | JTAG Header                                        |    |

| 2.9.3 Fan Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.9.3 F  | Fan Header                                         | 40 |

## Zynq Ultrascale+ MPSoC SBC Hardware User Guide

| 2.9.4 RTC Header                                                             | 41 |

|------------------------------------------------------------------------------|----|

| 2.9.5 Power On/OFF Switch                                                    | 42 |

| 2.9.6 Reset Switch                                                           | 42 |

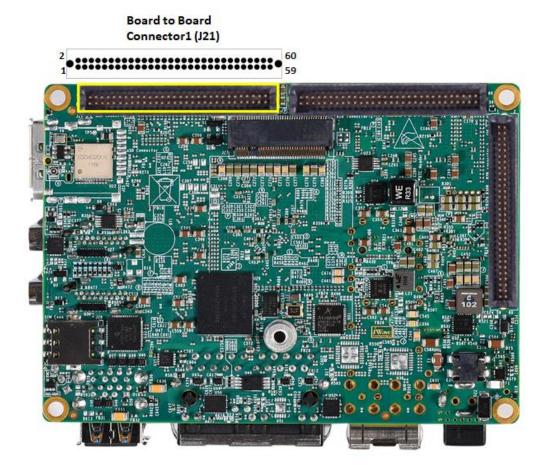

| 2.10 Board to Board Connector1                                               | 43 |

| 2.10.1 PS Interfaces                                                         | 45 |

| 2.10.1.1 SPI Interface                                                       | 45 |

| 2.10.1.2 CAN Interface                                                       | 45 |

| 2.10.1.3 I2C Interface                                                       | 46 |

| 2.10.2 PL Interfaces                                                         | 46 |

| 2.10.2.1 PL IOs – HP BANK64                                                  | 46 |

| 2.10.2.2 PL IOs – HD BANK45                                                  | 51 |

| 2.10.3 Power                                                                 | 52 |

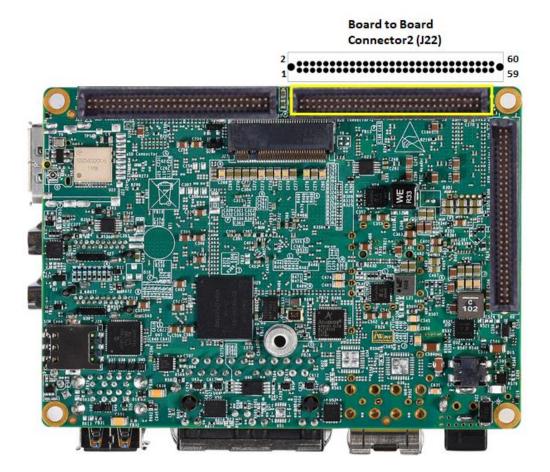

| 2.11 Board to Board Connector2                                               | 53 |

| 2.11.1 PL Interfaces                                                         | 55 |

| 2.11.1.1 PL IOs – HP BANK64                                                  | 55 |

| 2.11.1.2 PL IOS – HD BANK45                                                  | 58 |

| 2.11.1.3 PL IOs – HD BANK46                                                  | 60 |

| 2.11.2 Power                                                                 | 65 |

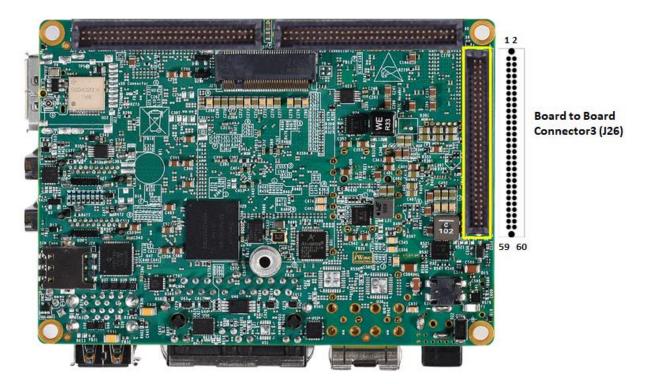

| 2.12 Board to Board Connector3                                               | 66 |

| 2.12.1 PL Interfaces                                                         | 68 |

| 2.12.1.1 PL IOS – HD BANK43                                                  |    |

| 2.12.1.2 PL IOS – HD BANK44                                                  | 73 |

| 2.12.2 Power                                                                 | 77 |

| 2.13 Zynq Ultrascale+ MPSoC PS Pin Multiplexing on Board to Board Connectors | 78 |

| 3. TECHNICAL SPECIFICATION                                                   | 80 |

|                                                                              |    |

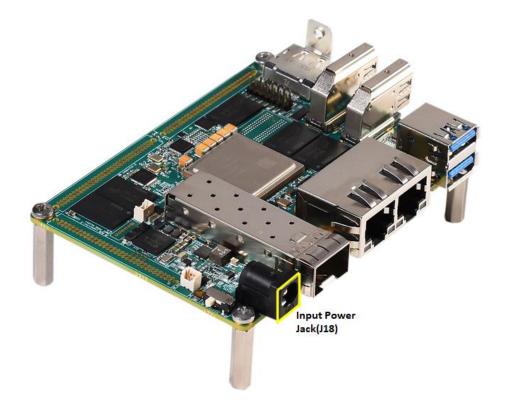

| 3.1 Power Input Requirement                                                  | 80 |

| 3.2 Power Output Specification                                               | 81 |

| 3.2.1 Power Consumption                                                      | 81 |

| 3.3 Environmental Characteristics                                            | 82 |

| 3.3.1 Temperature Specification                                              | 82 |

| 3.3.2 RoHS2 Compliance                                                       | 82 |

| 3.3.3 Electrostatic Discharge                                                | 82 |

| 3.3.4 Heat Sink                                                              | 82 |

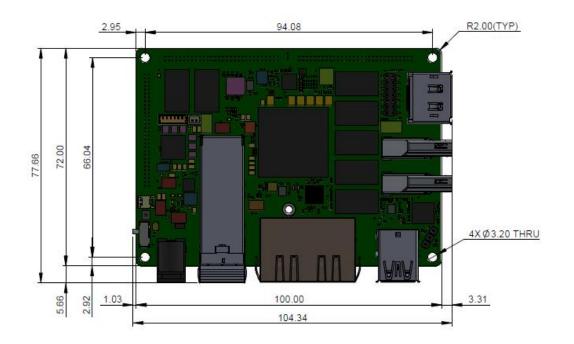

| 3.4 MechanicalCharacteristics                                                |    |

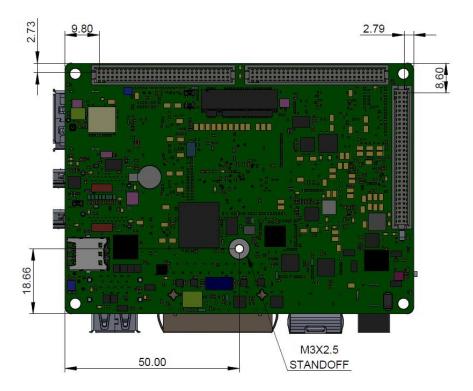

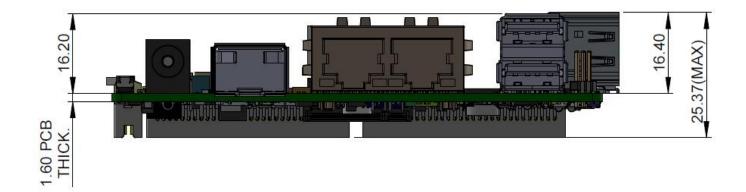

| 3.4.1 Zynq Ultrascale+ MPSoC SBC Mechanical Dimensions                       | 83 |

| 4. ORDERING INFORMATION                                                      | 85 |

### List of Figures

| Figure 1: Zynq Ultrascale+ MPSoC SBC Block Diagram                          | 11 |

|-----------------------------------------------------------------------------|----|

| Figure 2: Zynq Ultrascale+ MPSoC CPU Simplified Block Diagram               | 16 |

| Figure 3: Zynq Ultrascale+ MPSoC Devices Comparison                         | 17 |

| Figure 4: Error Status Indication LEDs                                      |    |

| Figure 5: Dual Gigabit Ethernet Port                                        | 24 |

| Figure 6: WLAN & BT with Antenna Connector                                  | 25 |

| Figure 7: Debug UART Header                                                 | 26 |

| Figure 8: Display Port Connector                                            | 27 |

| Figure 9: Dual Stack USB3.0 Type-A Jack                                     | 28 |

| Figure 10: M.2 Key B Connector                                              | 29 |

| Figure 11: HDMI IN Connector                                                | 33 |

| Figure 12: HDMI Out Connector                                               | 34 |

| Figure 13: SFP+ Connector                                                   | 35 |

| Figure 14: JTAG Header                                                      | 39 |

| Figure 15: Fan Header                                                       | 40 |

| Figure 16: RTC Header                                                       | 41 |

| Figure 17: Power ON/OFF Switch                                              | 42 |

| Figure 18: Reset Switch                                                     | 42 |

| Figure 19: Board to Board Connector1                                        | 43 |

| Figure 20: Board to Board Connector2                                        | 53 |

| Figure 21: Board to Board Connector3                                        | 66 |

| Figure 22: Input Power Jack                                                 | 80 |

| Figure 23: Mechanical dimension of Zynq Ultrascale+ MPSoC SBC - Top View    | 83 |

| Figure 24: Mechanical dimension of Zynq Ultrascale+ MPSoC SBC - Bottom View | 83 |

| Figure 25: Mechanical dimension of Zynq Ultrascale+ MPSoC SBC - Side View   | 84 |

|                                                                             |    |

### **List of Tables**

| Table 1: Acronyms & Abbreviations                              | 8  |

|----------------------------------------------------------------|----|

| Table 1: Acronyms & Abbreviations         Table 2: Terminology | 10 |

| Table 3: Zynq Ultrascale+ MPSoC SBC Reference Clock            |    |

| Table 4: Debug UART Header Pin Assignment                      |    |

| Table 5: M.2 Connector Pin Assignment                          |    |

| Table 6: SFP+ Connector Pin Assignment                         | 36 |

| Table 7: Clock Synthesier Output Clocks                        |    |

| Table 8: JTAG Header Pinout                                    |    |

| Table 9: Fan Header Pinout                                     |    |

| Table 10: RTC Header Pinout                                    | 41 |

| Table 11: Board to Board Connector1 Pinout                     | 44 |

| Table 12: Board to Board Connector2 Pinout                     |    |

| Table 13: Board to Board Connector3 Pinout                     | 67 |

| Table 14: PS IOMUX on Zynq Ultrascale+ MPSoC SBC               |    |

| Table 15: Power Input Requirement                              | 80 |

| Table 16: Power Output Specification                           | 81 |

| Table 17: Power Consumption <sup>1</sup>                       | 81 |

| Table 18: Temperature Specification                            | 82 |

| Table 19: Orderable Product Part Numbers                       | 85 |

|                                                                |    |

#### 1. INTRODUCTION

#### 1.1 Purpose

This document is the Hardware User Guide for the Zynq Ultrascale+ MPSoC Single Board Computer based on the Xilinx Zynq Ultrascale+ MPSoC. This board is fully supported by iWave Systems Technologies Pvt. Ltd. This Guide provides detailed information on the overall design and usage of the Zynq Ultrascale+ MPSoC SBC from a Hardware Systems perspective.

#### 1.2 SBC Overview

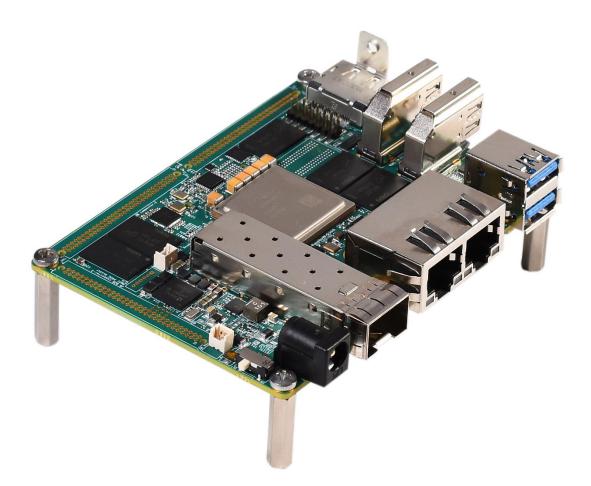

The Zynq Ultrascale+ MPSoC SBC is an extension of Zynq Ultrascale+ MPSoC. Zynq Ultrascale+ MPSoC SBC has a form factor of 72mm x 100mm and provides the functional requirements for an embedded application. Three high speed ruggedized terminal strip connectors provide the interface to carry all the I/O signals from Zynq Ultrascale+ MPSoC.

#### 1.3 List of Acronyms

The following acronyms will be used throughout this document.

#### Table 1: Acronyms & Abbreviations

| Acronyms   | Abbreviations                                                               |  |  |  |

|------------|-----------------------------------------------------------------------------|--|--|--|

| ADC        | Analog to Digital Converter                                                 |  |  |  |

| ARM        | Advanced RISC Machine                                                       |  |  |  |

| BSP        | Board Support Package                                                       |  |  |  |

| CAN        | Controller Area Network                                                     |  |  |  |

| CPU        | Central Processing Unit                                                     |  |  |  |

| DDR4 SDRAM | Double Data Rate fourth-generation Synchronous Dynamic Random Access Memory |  |  |  |

| FPGA       | Field Programmable Gate Array                                               |  |  |  |

| eMMC       | Embedded Multimedia Card                                                    |  |  |  |

| GB         | Giga Byte                                                                   |  |  |  |

| Gbps       | Gigabits per sec                                                            |  |  |  |

| GEM        | Gigabit Ethernet Controller                                                 |  |  |  |

| GHz        | Giga Hertz                                                                  |  |  |  |

| GPIO       | General Purpose Input Output                                                |  |  |  |

| 12C        | Inter-Integrated Circuit                                                    |  |  |  |

| IC         | Integrated Circuit                                                          |  |  |  |

| JTAG       | Joint Test Action Group                                                     |  |  |  |

| Kbps       | Kilobits per second                                                         |  |  |  |

| LVDS       | Low Voltage Differential Signalling                                         |  |  |  |

| MAC        | Media Access Controller                                                     |  |  |  |

| MB         | Mega Byte                                                                   |  |  |  |

| Mbps       | Megabits per sec                                                            |  |  |  |

| MHz        | Mega Hertz                                                                  |  |  |  |

## Zynq Ultrascale+ MPSoC SBC Hardware User Guide

| Acronyms | Abbreviations                               |  |  |  |

|----------|---------------------------------------------|--|--|--|

| NPTH     | Non Plated Through hole                     |  |  |  |

| РСВ      | Printed Circuit Board                       |  |  |  |

| PMIC     | Power Management Integrated IC              |  |  |  |

| PTH      | Plated Through hole                         |  |  |  |

| PL       | Programmable Logic                          |  |  |  |

| PS       | Processing System                           |  |  |  |

| RGMII    | Reduced Gigabit Media Independent Interface |  |  |  |

| RTC      | Real Time Clock                             |  |  |  |

| SBC      | Single Board Computer                       |  |  |  |

| SD       | Secure Digital                              |  |  |  |

| SDIO     | Secure Digital Input Output                 |  |  |  |

| SoC      | System On Chip                              |  |  |  |

| SPI      | Serial Peripheral Interface                 |  |  |  |

| UART     | Universal Asynchronous Receiver/Transmitter |  |  |  |

| ULPI     | UTMI+ Low Pin Interface                     |  |  |  |

| USB      | Universal Serial Bus                        |  |  |  |

| USB OTG  | USB On The Go                               |  |  |  |

| UTMI     | USB2.0 Transceiver Macrocell Interface      |  |  |  |

### Zynq Ultrascale+ MPSoC SBC Hardware User Guide

#### 1.4 Terminlogy Description

In this document, wherever Signal Type is mentioned, below terminology is used.

#### Table 2: Terminology

| Terminology | Description                                                          |  |  |  |

|-------------|----------------------------------------------------------------------|--|--|--|

| 1           | Input Signal                                                         |  |  |  |

| 0           | Output Signal                                                        |  |  |  |

| 10          | Bidirectional Input/output Signal                                    |  |  |  |

| CMOS        | Complementary Metal Oxide Semiconductor Signal                       |  |  |  |

| LVDS        | Low Voltage Differential Signal                                      |  |  |  |

| GBE         | Gigabit Ethernet Media Dependent Interface differential pair signals |  |  |  |

| USB         | Universal Serial Bus differential pair signals                       |  |  |  |

| OD          | Open Drain Signal                                                    |  |  |  |

| OC          | Open Collector Signal                                                |  |  |  |

| Power       | Power Pin                                                            |  |  |  |

| PU          | Pull Up                                                              |  |  |  |

| PD          | Pull Down                                                            |  |  |  |

| NA          | Not Applicable                                                       |  |  |  |

| NC          | Not Connected                                                        |  |  |  |

Note: Signal Type does not include internal pull-ups or pull-downs implemented by the chip vendors and only includes the pull-ups or pull-downs implemented On-SBC.

#### 1.5 References

- Zynq Ultrascale+ MPSoC Technical Reference Manual

- Zynq Ultrascale+ MPSoC Device Overview

#### 2. ARCHITECTURE AND DESIGN

This section provides detailed information about the Zyng Ultrascale+ MPSoC SBC features and Hardware architecture with high level block diagram. Also, this section provides detailed information about Board to Board connectors pin assignment and usage.

#### 2.1 Zyng Ultrascale+ MPSoC SBC Block Diagram

| iW-RainboW-G36                                                                                                                                                                       | S-Zynq Ultrascale+ MI                                                                                                                                           | PSoC SBC SOM Block Diagram                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12V Power<br>Connector<br>RTC Coin cell<br>Header<br>PMIC<br>Power to<br>Peripherals<br>DDR4 – 2GB<br>(Upgradable)<br>DDR4 (64bit)<br>DDR4 ECC (8bit)<br>(Upgradable)<br>eMMC (8bit) | Processing System (PS)<br>Quad/Dual ARM Cortex-A53,<br>Dual Cortex-R5,Mali-400MP2,VCU<br>DDR<br>Memory<br>Controller<br>SDD<br>UARTO                            | DP (2nd Lane) x 1<br>DP (1st Lane) x 1<br>SIM Nano SIM                                                                                                           |

| Debug UART<br>Header<br>JTAG Header<br>Micro SD<br>(Optional)<br>Antenna<br>Connectors<br>RF (WLAN, BT)<br>WLAN+BT                                                                   | UARTO<br>PS JTAG<br>SD1<br>USB0                                                                                                                                 | SATA/PCIe x 1<br>USB3.0 x 1<br>USB3.0 x 1<br>USB .0 x 1<br>USB .0 x 1<br>USB .0/2.0 x 1<br>USB .0/2.0 x 1<br>USB .0/2.0 x 2<br>ULPI<br>USB 2.0<br>PHY<br>USB 2.0 |

| B2B<br>Connector 1                                                                                                                                                                   | UART1<br>SPI0,12C1<br>CAN0, CAN1<br>I2C0<br>CAN0, CAN1<br>GEM3<br>Zynq Ultrascale+ (SFVC784)<br>ZU4/ZU5 - CG/EG/EV <sup>2</sup><br>ZU2/ZU3 - CG/EG <sup>2</sup> | RGMII Ethernet<br>PHY1 Gigabit Ethernet1<br>Bigabit Ethernet2 Dual RJ45<br>Magjack                                                                               |

| From 45 HD Bank<br>FPGA (2LVDS/4SE)<br>FPGA (13LVDS/26SE)<br>FPGA (12LVDS/14SE)<br>FPGA (12LVDS/14SE)<br>FPGA (12LVDS/24SE) 3                                                        |                                                                                                                                                                 | High Speed Transceiver x 3<br>To Transceiver<br>Bank<br>Clock<br>Generator<br>SFP+ Conne                                                                         |

| B2B<br>Connector 3<br>DDR4 – 1GB<br>(Upgradable)                                                                                                                                     | HD Bank<br>45<br>HD Bank<br>43,44<br>HP Bank<br>65,66<br>Bank 224<br>CH3                                                                                        | High Speed Transceiver x 1 <sup>4</sup><br>SDI Video Out<br>BNC Jack<br>(Optional)<br>SDI Video In<br>BNC Jack<br>(Optional)                                     |

1. DP Dual line supports upto 4K resolution.

C De Duain ine Supports Upito AK resolution.

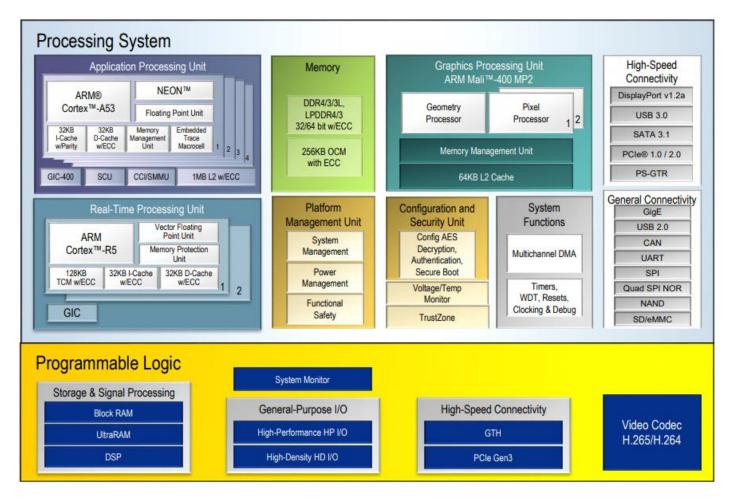

C G devices supports Dual ARM Cortex-AS3 & Dual ARM Cortex-R5. EG devices supports Quad ARM Cortex-AS3, Dual ARM Cortex-R5 & Mali-400MP2 GPU. EV devices supports Quad ARM

Cortex-AS3, Dual ARM Cortex-R5 & Mali-400MP2 GPU & H.264/H.265 VCU.

SYSMONE4 supports Jobit 200KSP5 ADC and supports upto 17 Analog Inputs (One dedicated Analog input and 16 auxiliary analog input from any PL BANK)

AGH Transceiver block is not supported in ZU2 & ZU3 MPSoC.

This symbol indicates Hardware assembly options available in the board and by default which option is support d. Contact iWave to support other assembly option.

mktg@iwavesystems.com

iWave Systems Technologies Pvt. Ltd.

Figure 1: Zynq Ultrascale+ MPSoC SBC Block Diagram

#### 2.1.1 Zynq Ultrascale+ MPSoC SBC Features

The Zynq Ultrascale+ MPSoC SBC supports the following features.

#### SoC

- Xilinx Zynq Ultrascale+ MPSoC

- Compatible Zynq Ultrascale+ MPSoC Family (SFVC784) ZU4EV, ZU5EV

- Programming Logic with up to 256K Logic cells and Processing System with integrated Quad-core ARM Cortex-A53 MPCore Application processor (up to 1.5GHz), Dual-core ARM Cortex-R5 MPCore Real Time Processor (up to 600MHz) and Mali<sup>™</sup>-400 MP2 Graphics Processor and H.264/H.265 Video Codec.

- Compatible Zynq Ultrascale+ MPSoC Family (SFVC784) ZU2EG, ZU3EG, ZU4EG, ZU5EG Programming Logic with up to 256K Logic cells and Processing System with integrated Quad-core ARM Cortex-A53 MPCore Application processor (up to 1.5GHz), Dual-core ARM Cortex-R5 MPCore Real Time Processor (up to 600MHz) and Mali<sup>™</sup>-400 MP2 Graphics Processor.

- Compatible Zynq Ultrascale+ MPSoC Family (SFVC784) ZU2CG, ZU3CG, ZU4CG, ZU5CG Programming Logic with up to 256K Logic cells and Processing System with integrated Dual-core ARM Cortex-A53 MPCore Application processor (up to 1.3GHz), Dual-core ARM Cortex-R5 MPCore Real Time Processor (up to 533MHz).

#### PMIC

• Dialog's DA9063 PMIC with RTC

#### Memory

- 2GB DDR4 SDRAM (64bit) for PS (Expandable)

- 1GB DDR4 SDRAM (32bit) for PL (Expandable)

- 8GB eMMC Flash (Expandable)

- EEPROM For MAC Address

- Micro SD Connector (Optional)<sup>1</sup>

#### **Features from PS Block**

- Dual 10/100/1000Mbps Ethernet through RJ45 Magjack

- WLAN & BT Module with Antenna connector <sup>1,2</sup>

- Debug UART Header

#### Features from PS-GTR Transceiver

- Display Port Connector (Dual Lane upto 4K@30)

- Dual USB3.0 Type A Jack

- M.2 Key B Connector with SATA, PClex1 and USB3.0

#### Features from PL-GTH Transceiver <sup>3</sup>

- HDMI Input Connector (Upto 4K@60)

- HDMI Output Connector (Upto 4K@60)

- 10G SFP+ Connector<sup>4</sup>

- 3G/12G SDI Input through HD BNC Jack (Optional)<sup>4</sup>

- 3G/12G SDI Output through HD BNC Jack (Optional)<sup>4</sup>

#### **Additional Features**

- Clock Synthesizer/Generator

- JTAG Header

- FAN Header

- RTC Coin Cell Header

- Power On/OFF & Reset Switch

#### Board to Board Connector1 Interfaces (60pin)

#### From PS Block

- DATA UART1 x 1 Port<sup>2</sup>

- SPI x 1 Port

- I2C1 x 1 Port

- CAN x 2 Ports

#### From PL Block

- PLIOs HP Bank64

- Upto 13 LVDS IOs/26 Single ended (SE) IOs

- Upto 3 GC Global Clock Input pins (LVDS/SE)

- Upto 8 ADC Input pins (Differential/Single Ended)

- $\circ$  ~ Variable IO voltage support from 1.2V to 1.8V ~

- PL IOs HD Bank45 <sup>5</sup>

- Upto 4 Single ended (SE) IOs

- Variable IO voltage support from 1.2V to 3.3V

#### Board to Board Connector2 Interfaces (60pin)

#### From PL Block

- PL IOs HP Bank64

- Upto 7 LVDS IOs/14 Single ended (SE) IOs

- Upto 1 GC Global Clock Input pins (LVDS/SE)

- Upto 5 ADC Input pins (Differential/Single Ended)

- Variable IO voltage support from 1.2V to 1.8V

- PLIOs HD Bank45 <sup>5</sup>

- Upto 4 LVDS IOs/8 Single ended (SE) IOs

- Upto 4 ADC Input pins (Differential/Single Ended)

- Variable IO voltage support from 1.2V to 3.3V

- PLIOs HD Bank46 <sup>5</sup>

- Upto 12 LVDS IOs/24 Single ended (SE) IOs

- Upto 4 GC Global Clock Input pins (LVDS/SE)

- Upto 12 ADC Input pins (Differential/Single Ended)

- Variable IO voltage support from 1.2V to 3.3V

- One dedicated ADC Input (Differential) from SYSMONE4

#### Board to Board Connector3 Interfaces (60pin)

#### From PL Block

- PL IOs HD Bank43 <sup>5</sup>

- Upto 11LVDS IOs/22 Single ended (SE) IOs

- Upto 3 GC Global Clock Input pins (LVDS/SE)

- Upto 11 ADC Input pins (Differential/Single Ended)

- Variable IO voltage support from 1.2V to 3.3V

- PLIOs HD Bank44 <sup>5</sup>

- Upto 12 LVDS IOs/24 Single ended (SE) IOs

- Upto 4 GC Global Clock Input pins (LVDS/SE)

- Upto 8 ADC Input pins (Differential/Single Ended)

- Variable IO voltage support from 1.2V to 3.3V

#### **General Specification**

- Power Supply : 12V, 5A Power Input Jack

- Form Factor : 72mm x 100mm

<sup>1</sup> In Zynq Ultrascale+ MPSoC SBC, SD1 signals from MPSoC is shared with WLAN module and MicroSD connector. So either WLAN or Micro SD connector can be supported. By default WLAN module is supported in SBC. Contact iWave to support Micro SD connector.